# МИКРОСХЕМЫ ИНТЕГРАЛЬНЫЕ 1273HA044

Руководство пользователя

# Содержание

| 1    | Введение                                                 | 3  |

|------|----------------------------------------------------------|----|

| 2    | Назначение и основные характеристики микросхем           | 4  |

| 2.1  | Архитектурные характеристики микросхем                   | 4  |

| 2.2  | Конструктивные характеристики микросхем                  | 5  |

| 2.3  | Электрические характеристики микросхем                   | 7  |

| 3    | Общая характеристика микросхем                           | 9  |

| 3.1  | Последовательный интерфейс для управления регистрами     | 10 |

| 3.2  | Общее описание последовательного интерфейса              | 11 |

| 3.3  | Командный байт                                           | 12 |

| 3.4  | Описание выводов последовательного интерфейса            | 13 |

| 3.5  | MSB(старший бит)/LSB(младший бит) передача               | 13 |

| 4.1  | Рекомендации относительно работы последовательного порта | 15 |

| 4    | Описание устройства                                      | 16 |

| 4.2  | Структура ЦАП                                            | 16 |

| 4.3  | Работа ЦАП                                               | 17 |

| 4.4  | Режим 1R/2R                                              | 19 |

| 4.5  | Тактовый вход                                            | 19 |

| 4.6  | Программируемая ФАПЧ                                     | 21 |

| 4.7  | Рассеиваемая мощность                                    | 25 |

| 4.8  | Режимы сна и низкого энергопотребления                   | 27 |

| 4.9  | Двухпортовый режим ввода данных                          | 27 |

| 4.10 | Двухпортовый режим ввода данных, ФАПЧ включена           | 28 |

| 4.11 | Инверсия DATACLK                                         | 29 |

| 4.12 | Нагрузочная способность формирователя DATACLK            | 29 |

| 4.13 | Однопортовыый режим, ФАПЧ включена                       | 30 |

| 4.14 | Инверсия ONEPORTCLK                                      | 31 |

| 4.15 | Нагрузочная способность формирователя ONEPORTCLK         | 32 |

| 4.16 | IQ спаривание                                            | 32 |

| 4.17 | Двухпортовыый режим, ФАПЧ выключена                      | 33 |

| 4.18 | Однопортовый режим, ФАПЧ выключена                       | 34 |

| 4.19 | Режимы цифрового фильтра                                 | 35 |

| 4.20 | Амплитудная модуляция                                    | 38 |

| 4.21 | Модуляция, интерполяция выключена                        | 39 |

| 4.22 | Модуляция, интерполяция 2 ×                              | 40 |

| 4.23 | Модуляция, интерполяция 4 ×                              | 42 |

| 4.24 | Модуляция, интерполяция 8 ×                              | 43 |

| 4.25 | Нуль-дополнение                                          | 44 |

| 4.26 | Модуляция (режим комплексного микширования)              | 45 |

| 4.27 | Операции на комплексных сигналах                         | 46 |

| 4.28 | Комплексная модуляция и подавление боковой полосы        | 47 |

|       | 4.29   | Подавление боковой полосы модулированных несущих           | 50     |

|-------|--------|------------------------------------------------------------|--------|

|       | 4.30   | Управление режимом через SPI                               | 61     |

|       | 4.31   | Описание регистров SPI                                     | 62     |

|       | 5      | Указания по применению и эксплуатации                      | 67     |

|       | 5.1    | Источник опорного напряжения                               | 67     |

|       | 5.2    | Различные виды подключения выходных цепей                  | 67     |

|       | 5.2.1  | Небуферизованный дифференциальный выход                    | 68     |

|       | 5.2.2  | Дифференциальное подключение, использующее трансформатор   | 69     |

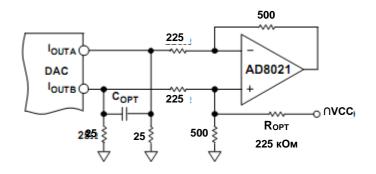

|       | 5.2.3  | Дифференциальное подключение, использующее операци         | ионный |

| усили | тель   |                                                            | 70     |

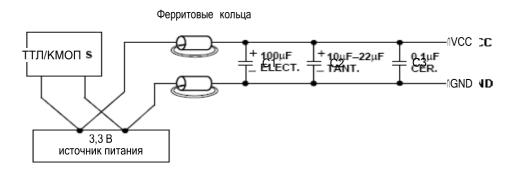

|       | 5.2.4  | Рекомендации по обеспечению питания, заземления и экраниро | эвания |

|       |        |                                                            | 71     |

|       | 6      | Заключение                                                 | 74     |

|       | Прил   | ожение А                                                   | 75     |

|       | Лист 1 | регистрации изменений                                      | 77     |

#### 1 Введение

Развитие цифровой техники и цифровых методов обработки сигналов определяет современные тенденции в разработке разнообразных устройств и приборов, при этом значительная роль принадлежит аналого- цифровому и цифро-аналоговому преобразованию. Такое преобразование широко используется во всех областях радиоэлектроники, в различной измерительной и контрольной аппаратуре, системах связи, радиовещании и телевидении.

Цифро-аналоговые преобразователи (ЦАП) предназначены для преобразования сигнала, определенного, как правило, в виде двоичного кода в напряжение или ток, пропорциональные значению цифрового кода.

Настоящее Руководство пользователя предназначено для изучения интегральных микросхем 1273HA044, содержит описание принципа работы, технические характеристики и другие сведения, необходимые для обеспечения полного использования технических возможностей микросхем.

Разработанные в ходе ОКР микросхемы ЦАП позволят уменьшить вес аппаратуры, обеспечить требуемые показатели по надежности и сроку службы, а также заменить аналогичные импортные ИС в средствах ВВСТ.

#### 2 Назначение и основные характеристики микросхем

1273HA044 — интегральная микросхема двухканального 16-разрядного параллельного цифро-аналогового преобразователя (ЦАП) на источниках тока.

Основной областью применения микросхем является одноканальное и многоканальное передающее коммуникационное оборудование, использующее цифровую модуляцию. К нему относятся как беспроводные передающие системы базовых станций сотовой связи, так и кабельные передатчики, модемы и другое оборудование.

#### 2.1 Архитектурные характеристики микросхем

Микросхема имеет порт последовательного интерфейса, встроенный источник опорного напряжения, умножитель тактовой частоты, в каждом канале имеются: параллельный интерфейс входных данных, цифровой комплексный модулятор, пара комплементарных токовых выходов и цифровые интерполирующие фильтры. Микросхема питается от трех источников напряжением 3,3 В и имеет два режима пониженного потребления мощности.

#### Характеристики ЦАП:

- максимальная частота обновления выходных данных 400 МГц;

- максимальная частота обновления входных данных 160 МГц;

- время установления 11 нс;

- интегральная нелинейность (типовое значение)  $\pm$  6,0 EMP;

- дифференциальная нелинейность (типовое значение) ± 3,0 EMP;

- разрядность 16 бит (65 536 значений выходного тока);

- дифференциальные токовые выходы IOUTA, IOUTB: максимальные токи  $I_{\text{OUTA}},\,I_{\text{OUTB}}$  от 2 до 20 мA;

- входные триггеры-защелки, срабатывающие по фронту тактового сигнала;

- диапазон температур окружающей среды: от минус 60 до 85 °C.

#### 2.2 Конструктивные характеристики микросхем

Микросхема выполнена в 88-выводном металлокерамическом корпусе 4235.88-1.

Масса микросхемы – не более 4,5 г.

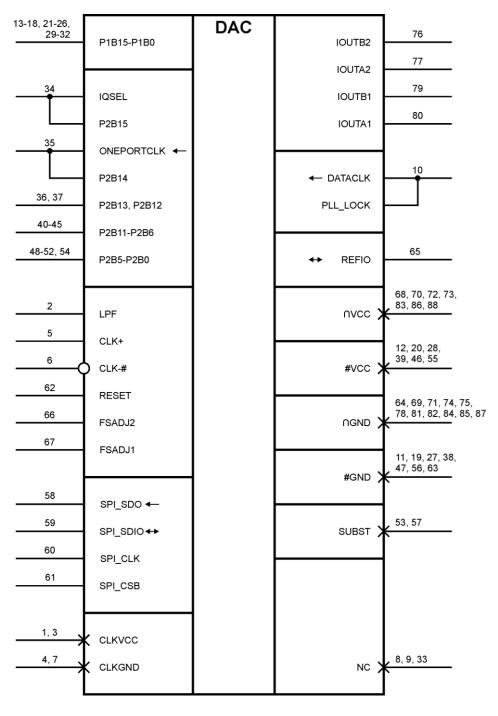

Условное графическое обозначение микросхемы приведено на рисунке 2.1.

Функциональное назначение выводов приведено в таблице 2.1.

Рисунок 2.1 – Условное графическое обозначение ИС 1273НА044

Та блица 2.1 – Функциональное назначение выводов микросхемы 1273HA044

| Номер                                            | Обозначение    | Обозна-<br>чение<br>альтерна- | Функциональное назначение                                      | Тип    |

|--------------------------------------------------|----------------|-------------------------------|----------------------------------------------------------------|--------|

| вывода                                           | вывода         | тивной<br>функции<br>вывода   | Функциональное назначение                                      | вывода |

| 13–18,<br>21–26, 29–32                           | P1B15 – P1B0   |                               | Биты данных от В15 до В0 порта 1                               | I      |

| 34                                               | IQSEL          | P2B15                         | Вход выбора канала<br>Бит данных В15 порта 2                   | I<br>I |

| 35                                               | ONEPORTCLK     | P2B14                         | Выход тактовой частоты<br>Бит данных В14 порта 2               | O<br>I |

| 36, 37, 40–45,<br>48–52, 54                      | P2B13 – P2B0   |                               | Биты данных от В13 до В0 порта 2                               | I      |

| 58                                               | SPI_SDO        |                               | Выход данных последовательного порта                           | О      |

| 59                                               | SPI_SDIO       |                               | Вход/выход данных последовательного порта                      | I/O    |

| 60                                               | SPI_CLK        |                               | Вход тактового сигнала последовательного порта                 | I      |

| 61                                               | SPI_CSB        |                               | Вход разрешения работы последовательного порта                 | I      |

| 2                                                | LPF            |                               | Вход фильтра ФАПЧ                                              | I      |

| 5                                                | CLK+           |                               | Прямой вход дифференциального тактового сигнала                | I      |

| 6                                                | CLK-#          |                               | Инверсный вход дифференциального тактового сигнала             | I      |

| 62                                               | RESET          |                               | Сброс регистров последовательного порта                        | I      |

| 66                                               | FSADJ2         |                               | Вход установки тока полной шкалы канала Q                      | I      |

| 67                                               | FSADJ1         |                               | Вход установки тока полной шкалы канала I                      | I      |

| 65                                               | REFIO          |                               | Вход/выход ИОН                                                 | I/O    |

| 76                                               | IOUTB2         |                               | Дополнительный токовый выход ЦАП, Q канал                      | O      |

| 77                                               | IOUTA2         |                               | Прямой токовый выход ЦАП, Q канал                              | O      |

| 79                                               | IOUTB1         |                               | Дополнительный токовый выход ЦАП, І канал                      | О      |

| 80                                               | IOUTA1         |                               | Прямой токовый выход ЦАП, І канал                              | O      |

| 10                                               | DATACLK        | PLL_LOCK                      | Вход тактовой частоты данных Выход индикации захвата фазы ФАПЧ | O      |

| 1, 3                                             | CLKVCC         |                               | Вывод питания тактового сигнала                                | _      |

| 4, 7                                             | CLKGND         |                               | Общий вывод тактового сигнала                                  | _      |

| 11, 19, 27, 38,<br>47, 56, 63                    | #GND           |                               | Общий вывод цифровой части микросхемы                          | _      |

| 64, 69, 71, 74,<br>75, 78, 81, 82,<br>84, 85, 87 |                |                               | Общий вывод аналоговой части микросхемы                        | _      |

| 12, 20, 28, 39,<br>46, 55                        | #VCC           |                               | Вывод питания цифровой части микросхемы                        | _      |

| 68, 70, 72, 73,<br>83, 86, 88                    | ∩VCC           |                               | Вывод питания аналоговой части микросхемы                      | _      |

| 53, 57                                           | SUBST          |                               | Подложка кристалла                                             | _      |

| 8, 9, 33                                         | NC             |                               | Выводы не используются                                         | _      |

| Приме                                            | чание – В граф | е «Тип выво                   | да»: I – вход, O – выход.                                      |        |

## 2.3 Электрические характеристики микросхем

Электрические характеристики микросхем 1273НА044 при приемке и поставке приведены в таблице 2.2.

Значения предельно допустимых электрических режимов эксплуатации в диапазоне рабочих температур приведены в таблице 2.3.

Термины, определения, сокращения и буквенные обозначения параметров – по ОСТ В 11 0998-99, ГОСТ 17021-88 и ГОСТ 19480-89.

Термины, определения и буквенные обозначения параметров, неустановленные действующими стандартами, представлены в приложении A.

Т а б л и ц а 2.2 — Значения электрических параметров микросхемы 1273HA044 при приемке и поставке

|                                                                                  | Буквенное          | Нор   |       | Темпера     |

|----------------------------------------------------------------------------------|--------------------|-------|-------|-------------|

| Наименование параметра,                                                          | обозначе-          | парам | етра  | тура        |

| единица измерения, режим измерения                                               | ние                | не    | не    | среды,      |

|                                                                                  | параметра          | менее | более | °C          |

| 1                                                                                | 2                  | 3     | 4     | 5           |

| 1 Выходное опорное напряжение на выводе                                          | U <sub>REFIO</sub> |       |       |             |

| REFIO, B, <sup>1)</sup>                                                          |                    | 1,14  | 1,26  |             |

| $U_{CC1} = 3.3 \text{ B}, U_{CC2} = 3.3 \text{ B}, U_{CC3} = 3.3 \text{ B}$      |                    |       |       |             |

| 2 Ток утечки низкого уровня на входах                                            | ${ m I}_{ m ILL}$  |       |       |             |

| P1B15 - P1B0, P2B15 - P2B0, RESET, CLK+,                                         |                    |       |       |             |

| CLK-#, SPI_SDIO, SPI_CLK, SPI_CSB, MKA, 1),2)                                    |                    | -10   | _     |             |

| $U_{CC1} = 3.6 \text{ B}, U_{CC2} = 3.6 \text{ B}, U_{CC3} = 3.6 \text{ B},$     |                    |       |       |             |

| $U_{IL} = 0 B$                                                                   | _                  |       |       |             |

| 3 Ток утечки высокого уровня на входах                                           | $I_{\rm ILH}$      |       |       |             |

| P1B15 - P1B0, P2B15 - P2B0, RESET, CLK+,                                         |                    |       |       |             |

| CLK-#, SPI_SDIO, SPI_CLK, SPI_CSB, MKA, 1),2)                                    |                    | _     | 10    |             |

| $U_{CC1} = 3.6 \text{ B}, \ U_{CC2} = 3.6 \text{ B}, \ U_{CC3} = 3.6 \text{ B},$ |                    |       |       |             |

| $U_{IH} = U_{CC1}$                                                               |                    |       |       | $-60 \pm 3$ |

| 4 Динамический ток потребления по выводам #VCC                                   | I <sub>OCC1</sub>  |       |       | $25 \pm 10$ |

| MA, <sup>1)</sup>                                                                |                    | _     | 50    | $85 \pm 3$  |

| $U_{CC1} = 3.6 \text{ B}, U_{CC2} = 3.6 \text{ B}, U_{CC3} = 3.6 \text{ B}$      |                    |       |       | 05 ± 5      |

| $f_{\text{CI\_CLK}} = 160 \text{ M}\Gamma$ ц                                     |                    |       |       |             |

| 5 Динамический ток потребления по выводам                                        | I <sub>OCC2</sub>  |       |       |             |

| $\cap VCC, MA,^{1)}$                                                             |                    | _     | 80    |             |

| $U_{CC1} = 3,6 \text{ B}, U_{CC2} = 3,6 \text{ B}, U_{CC3} = 3,6 \text{ B},$     |                    |       |       |             |

| $f_{\text{CI\_CLK}} = 160 \text{ M}\Gamma$ ц                                     |                    |       |       |             |

| 6 Динамический ток потребления по выводам                                        | I <sub>OCC3</sub>  |       |       |             |

| CLKVCC, MA,                                                                      |                    | _     | 30    |             |

| $U_{CC1} = 3.6 \text{ B}, U_{CC2} = 3.6 \text{ B}, U_{CC3} = 3.6 \text{ B},$     |                    |       |       |             |

| $f_{\text{CI\_CLK}} = 160 \text{ M}\Gamma$ ц                                     |                    |       |       |             |

| 7 Интегральная нелинейность, МР, 1),2)                                           | $E_L$              | -9,5  | 9,5   |             |

| $U_{CC1} = 3.3 \text{ B}, U_{CC2} = 3.3 \text{ B}, U_{CC3} = 3.3 \text{ B},$     |                    |       |       |             |

| $I_{OUTFS} = 20 \text{ mA}$                                                      |                    |       |       |             |

# Окончание таблицы 2.2

| 1                                                                                              | 2        | 3    | 4   | 5 |

|------------------------------------------------------------------------------------------------|----------|------|-----|---|

| 8 Дифференциальная нелинейность, МР, 1),2)                                                     | $E_{LD}$ | -6,5 | 6,5 |   |

| $U_{CC1} = 3.3 \text{ B}, U_{CC2} = 3.3 \text{ B}, U_{CC3} = 3.3 \text{ B},$                   |          |      |     |   |

| $I_{OUTFS} = 20 \text{ MA}$                                                                    |          |      |     |   |

| 9 Функциональный контроль                                                                      | ΦК       | _    | _   |   |

| $U_{CC1} = U_{CC2} = U_{CC3} = (3,0; 3,6) B;$                                                  |          |      |     |   |

| $f_{\text{CI\_CLK}} = 160 \text{ M}\Gamma$ ц, $f_{\text{CI\_SPI\_CLK}} = 15 \text{ M}\Gamma$ ц |          |      |     |   |

Таблица 2.3 – Предельно допустимые и предельные режимы эксплуатации микросхемы 1273НА044

| Наименование параметра режима,                                                                                               | Буквенное<br>обозначение | Предельно допустимый режим |                  | Предельный режим |                        |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------|------------------|------------------|------------------------|

| единица измерения                                                                                                            | параметра                | не менее                   | не более         | не менее         | не более               |

| 1 Напряжение питания цифровой части, В                                                                                       | U <sub>CC1</sub>         | 3,0                        | 3,6              | -0,3             | 4,0                    |

| 2 Напряжение питания аналого-<br>вой части микросхемы, В                                                                     | U <sub>CC2</sub>         | 3,0                        | 3,6              | -0,3             | 4,0                    |

| 3 Напряжение питания формирователей тактовых импульсов, В                                                                    | Ucc3                     | 3,0                        | 3,6              | -0,3             | 4,0                    |

| 4 Входное напряжение низкого уровня на входах P1B15 — P1B0, P2B15 — P2B0, RESET, CLK+, CLK-#, SPI_SDIO, SPI_CLK, SPI_CSB, B  | U <sub>IL</sub>          | 0                          | 0,9              | -0,3             | _                      |

| 5 Входное напряжение высокого уровня на входах P1B15 — P1B0, P2B15 — P2B0, RESET, CLK+, CLK-#, SPI_SDIO, SPI_CLK, SPI_CSB, B | $U_{\mathrm{IH}}$        | 2,1                        | U <sub>CC1</sub> | _                | U <sub>CC1</sub> + 0,3 |

| 6 Частота следования импульсов тактовых сигналов CLK, МГц                                                                    | $f_{CI\_CLK}$            |                            | 160              |                  |                        |

| 7 Частота следования импульсов по входу SPI_CLK, МГц                                                                         | f <sub>CI_SPI_CLK</sub>  | _                          | 15               | _                | _                      |

Параметр измеряется при выключенном блоке PLL. Параметры  $I_{ILL}$ ,  $I_{ILH}$ ,  $E_{LD}$ ,  $E_{L}$  при температуре минус 60 °C не измеряются, а гарантируются нормами при температуре ( $25 \pm 10$ ) °С.

#### 3 Общая характеристика микросхем

1273НА044 — сдвоенный интерполирующий ЦАП, состоящий из двух каналов данных, которые могут работать полностью независимо или соединенными в форме комплексного модулятора в архитектуре с подавлением зеркальной боковой полосы. Каждый канал ИС 1273НА044 содержит три КИХ-фильтра интерполятора: 2×, 4× и 8×. Скорости передачи входных и выходных данных могут быть достигнуты в пределах ограничений, приведенных в таблице 3.1.

Таблица 3.1

| Коэффициент  | Предельная частота     | Предельная частота |

|--------------|------------------------|--------------------|

| интерполяции | выборки входных данных | опроса ЦАП         |

|              | (MSPS)                 |                    |

| 1×           | 160                    | 160                |

| 2×           | 160                    | 320                |

| 4×           | 100                    | 400                |

| 8×           | 50                     | 400                |

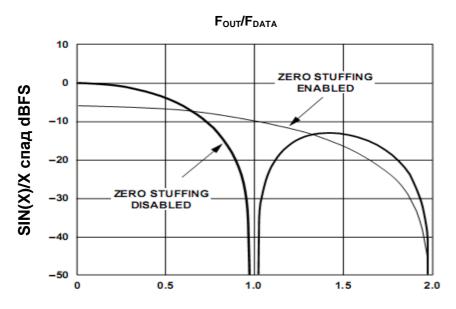

Каждый канал данных содержит цифровой модулятор, способный смешивать поток данных с сигналом гетеродина (LO) частоты  $f_{DAC}/2$ ,  $f_{DAC}/4$ , или  $f_{DAC}/8$ , где  $f_{DAC}$  — частота выходных данных ЦАП. Функция дополнения нулями также может быть включена для улучшения равномерности АЧХ в полосе пропускания или компенсации затухания, вносимого выходной характеристикой  $\sin(x)/x$  ЦАП. Быстродействие 1273HA044, вместе с возможностью цифровой модуляции, позволяет реализовать архитектуру прямого преобразования промежуточной частоты от 70 МГц и выше.

Цифровые модуляторы на ИС 1273НА044 могут быть объединены в комплексный модулятор. При использовании этой особенности с внешним аналоговым квадратурным модулятором, таким как AD8345, может быть создана архитектура с подавлением зеркальной боковой полосы. Чтобы оптимизировать подавление зеркальной боковой полосы, так же как и проникновение сигнала гетеродина в этой архитектуре, 1273НА044 позволяет устанавливать (через порт SPI) усиление и смещение для каждого канала ЦАП.

Микросхема 1273НА044 содержит схему фазовой автоподстройки частоты ФАПЧ (PLL), генератор тактовых импульсов и внутренний опорный источник напряжением 1,2 В. При включенной PLL, частота тактовых импульсов, подаваемых на CLK+/CLK-#, умножается и генерируются все необходимые внутренние синхросигналы. Каждый 16разрядный канал ЦАП содержит два комплементарных токовых выхода, токи полной шкалы которых могут быть заданы для обоих каналов одним внешним резистором или отдельным резистором для каждого канала (см. 1R/2R). 1273HA044 обладает низким «джиттером». раздел: режим Дифференциальный вход источника тактовых импульсов обеспечивает высокое подавление шумов, принимая синусоидальный или прямоугольный сигнал на входе. Для каждого функционального блока предоставлены отдельные выводы напряжения питания, чтобы гарантировать оптимальные характеристики по шуму и искажениям.

Режимы сна или низкого энергопотребления могут использоваться, чтобы отключить выходной ток ЦАП (режим сна) или все цифровые и аналоговые блоки микросхемы (режим низкого энергопотребления). Порт последовательного интерфейса SPI используется для программирования большинства функций 1273HA044. Отметим, что в режиме низкого потребления порт SPI остается активным.

# 3.1 Последовательный интерфейс для управления регистрами

Последовательный порт 1273НА044 – адаптивный, синхронный, последовательный порт, который позволяет легко создавать интерфейс со многими промышленными микроконтроллерами и микропроцессорами. Последовательный вход/выход совместим с большинством синхронных форматов передачи данных, включая оба протокола Motorola SPI и Intel SSR. Интерфейс позволяет осуществлять чтение/запись всех регистров, однобайтовая или расположенных В 1273HA044. Поддерживается многобайтовая передача, так же как и форматы первым MSB или LSB. Порт последовательного интерфейса может быть сконфигурирован с одним (двунаправленным) pin' ввода-вывода (SDIO) или c двумя (однонаправленными) pin' для ввода и вывода (SDI/SDO).

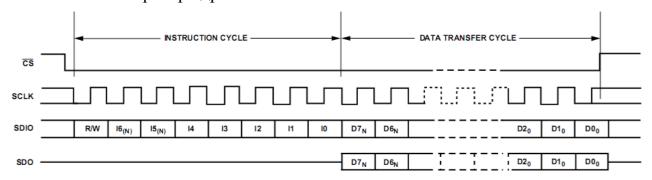

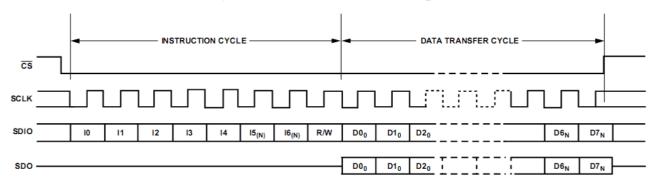

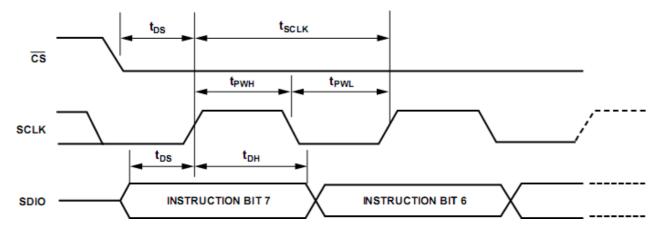

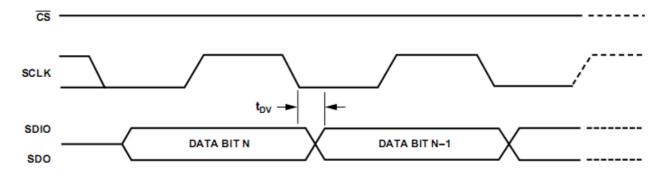

#### 3.2 Общее описание последовательного интерфейса

Есть две фазы цикла передачи данных ИС 1273НА044. Фаза 1 командный цикл, который записывает командный байт в контроллер 1273HA044 синхронно с первыми восьмью импульсами SCLK по возрастающему фронту. Командный байт предоставляет контроллеру последовательного интерфейса 1273НА044 информацию относительно обмена данными, который является фазой 2 этого цикла передачи данных. Командный байт фазы 1 определяет: считываются ли поступающие данные или записываются; он так же определяет число байт в фазе обмена данными адрес регистра для первого стартовый байта. Первые положительных импульсов SCLK каждого цикла передачи данных используются, чтобы записать командный байт в 1273НА044. Остальные фронты SCLK – для фазы 2 цикла передачи. Фаза 2 – это фактическая между контроллером 1273HA044 И системным передача данных контроллером. Фаза 2 цикла – это передача от одного до четырех байт данных, в зависимости от того, как определено командным байтом. Обычно, мультибайт более использование передачи на ОДИН является предпочтительным методом. Однако, передачи одиночного байта полезны для уменьшения лишних циклов центрального процессора, когда для доступа к регистру требуется только один байт. Регистры изменяются тотчас на записи последнего бита каждого передаваемого байта.

Значение логической единицы на выводе SPI\_CSB сбросит последовательный интерфейс в начальное состояние командного цикла. Это произойдет независимо от текущего состояния внутренних регистров или сигналов на входах SPI. Если порт последовательного интерфейса находится в середине командной фазы или в фазе передачи данных, то никакие данные не будут записаны.

#### 3.3 Командный байт

Командный байт содержит информацию, приведенную в таблице 3.1.

Таблица 3.1

| MSB |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|-----|

| I7  | I6 | I5 | I4 | I3 | I2 | I1 | IO  |

| R/W | N1 | N0 | A4 | A3 | A2 | A1 | A0  |

#### R/W

Бит 7 из управляющего байта определяет, произойдет чтение или запись данных после командного байта. Логическая единица означает чтение. Логический ноль – запись.

#### N1, N0

Биты 6 и 5 из управляющего байта определяют число байт, которые будут переданы во время цикла передачи данных. Дешифровка бит показана в таблице 3.2.

Таблица 3.2

| N1 | N0 | Описание         |

|----|----|------------------|

| 0  | 0  | Передача 1 байта |

| 0  | 1  | Передача 2 байт  |

| 1  | 0  | Передача 3 байт  |

| 1  | 1  | Передача 4 байт  |

#### A4, A3, A2, A1, A0

Биты 4, 2, 3, 1 и 0 из управляющего байта определяют, к какому регистру получают доступ во время передачи данных в цикле связи. Для мультибайтовой передачи этот адрес – стартовый адрес байта. Оставшиеся адреса регистра генерируются ИС 1273HA044.

#### 3.4 Описание выводов последовательного интерфейса

#### SPI\_CLK (вывод 60) – синхросигнал

Вывод синхросигнала используется для синхронизации данных «к» и «от» ИС 1273НА044 и выполнения внутренних машинных команд. Максимальная частота SPI\_CLK составляет 15 МГц. Ввод данных происходит по фронту SPI\_CLK. Вывод данных из 1273НА044 происходит по спаду SCLK.

#### SPI\_CSB (вывод 61) – выбор схемы

Активный низкий уровень входа инициирует цикл передачи. Это позволяет использовать более одного устройства на одной и той же последовательной линии связи. Выводы SPI\_SDO и SPI\_SDIO будут в состоянии высокого импеданса при высоком уровне сигнала на этом входе. Сигнал выбора схемы должен быть низким в продолжении всего цикла передачи.

#### SPI\_SDIO (вывод 59) – последовательные данные I/O

Данные всегда записываются в 1273НА044 с этого вывода. Однако этот вывод может использоваться как двунаправленная линия данных. Конфигурацией этого вывода управляет бит 7 из нулевого регистра. Значение по умолчанию – логический нуль, который конфигурирует вывод SPI\_SDIO как однонаправленный.

#### SPI\_SDO (вывод 58) – последовательный выход данных

Данные считываются с этого вывода для протоколов, которые используют отдельные линии для передачи и получения данных. В случае, где 1273НА044 работает в режиме с одним двунаправленным pin' I/O, этот вывод не выдает выходных данных и находится в состоянии высокого импеданса.

## 3.5 MSB(старший бит)/LSB(младший бит) передача

Последовательный порт 1273HA044 может поддерживать оба формата данных «MSB первый» или «LSB первый». Этой функциональной возможностью управляет бит 6 в нулевом регистре.

По умолчанию бит 6 равен нулю, т.е. – MSB первый. Когда этот бит находится в активном высоком уровне, последовательный порт ИС 1273HA044 находится в формате LSB первый. В режиме LSB первый, байт

команды и байты данных должны записываться от LSB к MSB. В режиме первый LSB, внутренний байт генератора адреса наращивается для каждого байта многобайтового цикла передачи.

Когда данный бит находится в низком уровне, последовательный порт 1273HA044 находится в формате MSB первый. В режиме MSB первый байт команды и байты данных должны записываться от MSB к LSB.

Увеличение от 1Fh изменяет генератор адреса к 00h. Уменьшение от 00h изменяет генератор адреса к 1Fh.

Рисунок 3.1 – Режим MSB первый

Рисунок 3.2 – Режим LSB первый

Рисунок 3.3 – Временные диаграммы для записи в регистр 1273НА044

Рисунок 3.4 – Временные диаграммы для чтения из регистра 1273НА044

# 4.1 Рекомендации относительно работы последовательного порта

Шестой и седьмой биты из регистра с адресом 00h являются битами конфигурации последовательного порта ИС 1273HA044. Важно отметить, что конфигурация изменяется тотчас на записи последнего бита в регистр. Для многобайтовой передачи запись в этот регистр может произойти в середине цикла передачи. Необходимо позаботиться о компенсации для остающихся байтов текущего цикла передачи.

Вышесказанное применимо к установке бита сброса в регистре 00h. Все другие регистры устанавливаются в их значения по умолчанию, но биты регистра 00h программный сброс не затрагивает.

Рекомендуется использовать передачу одиночного байта для изменения конфигурации последовательного порта или инициируя программный сброс.

# 4 Описание устройства

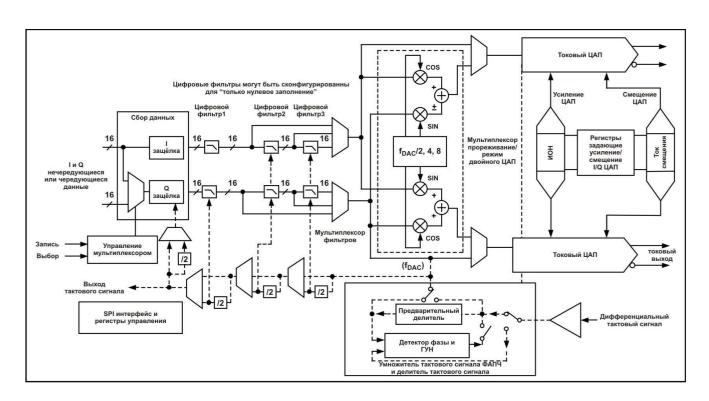

#### 4.2 Структура ЦАП

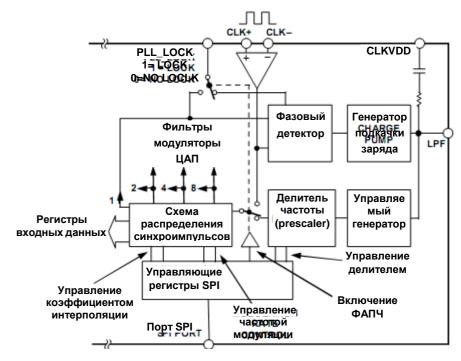

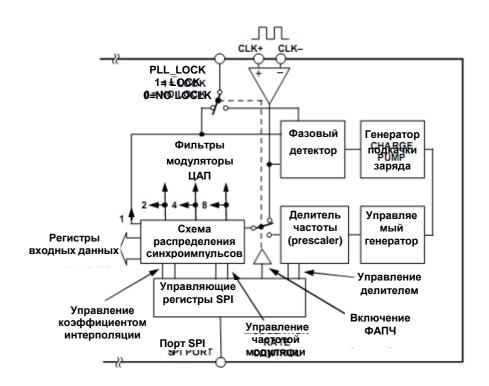

Микросхема содержит следующие функциональные блоки (смотри рисунок 4.1):

- последовательный интерфейс (SPI);

- два канала ЦАП;

- входные триггеры-защелки I, Q;

- умножитель частоты тактового сигнала ФАПЧ;

- цифровые интерполяционные фильтры;

- регистры усиление/смещение;

- цифровой модулятор;

- источник опорного напряжения 1,2 В (ИОН).

Рисунок 4.1 – Схема электрическая структурная микросхемы 1273 НА 044

Микросхема имеет независимые выводы для питания аналоговых, цифровых, тактовых блоков и схемы умножения частоты. Для питания аналоговых блоков используются выводы  $\cap$ VCC и  $\cap$ GND. Для питания

цифровых блоков используются выводы #VCC и #GND. Для питания тактовой схемы используются выводы CLKVCC и CLKGND.

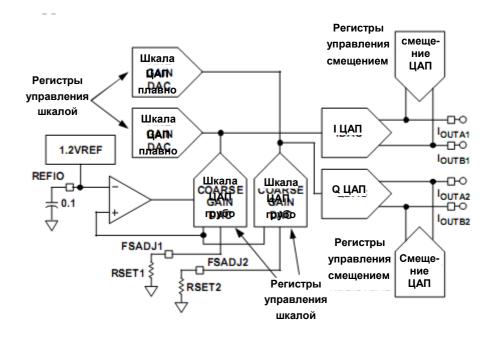

#### 4.3 Работа ЦАП

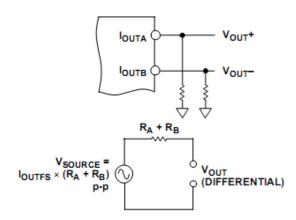

На рисунке 4.2 показан двойной 16-битовый выход ЦАП вместе с внутренним источником, усилителем и регистрами управления усилением и смещением. Отметим, что внешний источник может использоваться для принудительного задания уровня внутреннего источника простой подачей выхода внешнего источника на вывод REFIO.

Рисунок 4.2 – Выходы ЦАП, масштабирование тока внутреннего источника и регулировка усиления/смещения

В уравнении (1) описывается функция преобразования ЦАП.

$$I_{OUTA} = \begin{bmatrix} 6 \times I_{REF} \\ -8 \end{bmatrix} \underbrace{\begin{pmatrix} COARSE + 1 \\ 16 \end{pmatrix}}_{16} - \underbrace{\begin{pmatrix} 3 \times I_{REF} \\ 32 \end{pmatrix}}_{256} \underbrace{\begin{pmatrix} FINE \\ 256 \end{pmatrix}}_{256} \times \underbrace{\begin{pmatrix} 1024 \\ 24 \end{pmatrix}}_{216} \underbrace{\begin{pmatrix} DATA \\ 2^{16} \end{pmatrix}}_{16},$$

$$I_{OUTB} = \underbrace{\begin{pmatrix} 6 \times I_{REF} \\ 8 \end{pmatrix}}_{16} \underbrace{\begin{pmatrix} COARSE + 1 \\ 32 \end{pmatrix}}_{16} \underbrace{\begin{pmatrix} 3 \times I_{REF} \\ 16 \end{pmatrix}}_{256} \underbrace{\begin{pmatrix} FINE \\ 1024 \end{pmatrix}}_{24} \underbrace{\begin{pmatrix} 2^{16} - DATA - 1 \\ 2 \end{pmatrix}}_{16},$$

$$I_{IO} = \underbrace{4 \times I_{REF}}_{REF} \underbrace{\begin{pmatrix} OFFSET \\ 1024 \end{pmatrix}}_{1024},$$

где DATA – значение регистра данных канала (входной код);

$I_{REF}$  – опорный ток, устанавливаемый внутренним источником 1,2 В и внешним резистором  $R_{SET}$ ;

COARSE, FINE – значения регистров грубой и плавной настройки, соответственно;

$I_{IO}$  – ток смещения нуля;

OFFSET – значения регистров смещения.

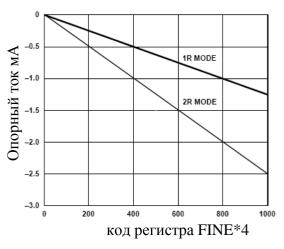

Что касается функции преобразования в уравнении (1), то ток устанавливается внутренним источником 1,2 В, внешним резистором  $R_{\rm SET}$  и значением регистра грубой настройки. Плавное усиление ЦАП введено для IDAC и QDAC, это значение масштабировано и равно 1024/24. На рисунке 4.3 показывается эффект масштабирования грубой  $I_{\rm FULLSCALE}$ , на рисунке 4.4 – плавной регулировки  $I_{\rm FULLSCALE}$  ЦАП.

Рисунок 4.3

Рисунок 4.4

IDAC и QDAC – есть PMOS матрицы источников тока, сегментированные в конфигурации 5-4-7. Пять старших разрядов регистра данных (DATA) управляют старшей матрицей из 31 источника тока. Следующие четыре бита управляют средней матрицей из 15 источников тока, значения которых равны 1/16 источника тока старшей матрицы. Семь младших разрядов – есть двоично-взвешенные доли (1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128) источника тока средней матрицы. Все источники тока подключены или к  $I_{OUTA}$  или к  $I_{OUTB}$ , в зависимости от входного кода (DATA).

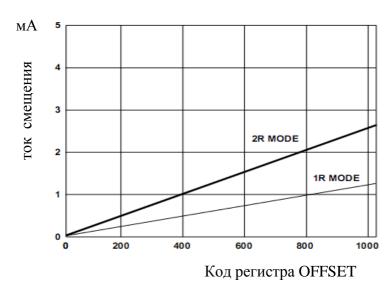

Управление смещением (OFFSET) определяет небольшой ток (рисунок 4.5), который может быть добавлен к  $I_{OUTA}$  или  $I_{OUTB}$  (только на один) в каждом канале. Выбор выхода  $I_{OUT}$ , на который направляется ток смещения, программируется через регистр 08h, бит 7– (для IDAC) и

регистр 0Ch, бит 7 = (для QDAC). Плавная регулировка усиления каждого канала приводит к улучшению баланса квадратурной амплитудной модуляции (QAM), улучшению точностей модуляции и подавления зеркальной боковой полосы.

Рисунок 4.5 Смещение выходного тока ЦАП

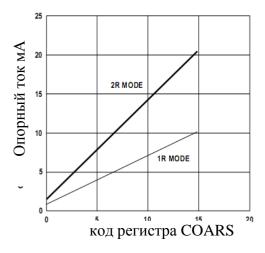

#### 4.4 Режим 1R/2R

В режиме 2R опорный ток для каждого канала устанавливается резистором FSADJ канале. В независимо на ЭТОМ режиме преобразователь включен таким образом, чтобы формировать опорный ток от одного резистора на выводе FSADJ1. Функция преобразования в уравнении (1) действительна для режима 2R. В режиме 1R ток задается одним резистором FSADJ и делится поровну между двумя каналами. Вследствие этого в режиме 1R к уравнению (1) должен быть применен коэффициент масштабирования 1/2. Полномасштабный ток ЦАП в режиме 1R может быть равен 20 мA при использовании внутреннего источника 1,2B и резистора на 950 Ом вместо 1,9 кОм, обычно используемого в 2R режиме.

#### 4.5 Тактовый вход

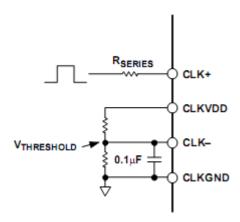

Тактовые входы 1273НА044 могут подключаться дифференциально или несимметрично. У внутренней тактовой схемы есть линии питания и земли (CLKVCC, CLCGND), которые отделяются от другого питания на кристалле, чтобы минимизировать **jitter** от внутренних источников шума.

На рисунке 4.6 показан 1273HA044, тактируемый несимметричным тактовым источником. Выводы CLK+/CLK-# формируют дифференциальный вход (CLKIN) так, чтобы неиспользуемый вход был смещен по постоянному току к уровню среднего значения напряжения управляемого тактового входа.

Рисунок 4.6 – Несимметричное управление тактовым входом

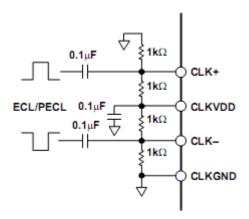

Конфигурация для дифференциального управления тактовым входом показана на рисунке 4.7. Разделительные конденсаторы по постоянному току могут быть соединены с выходом формирователя тактовых импульсов, размах напряжения которого превышает CLKVCC или CLKGND. Если размах напряжения формирователя находится в пределах диапазона питания 1273HA044, то разделительные конденсаторы и смещающие резисторы не нужны.

Рисунок 4.7 Дифференциальное управление тактовым входом

Для преобразования однопроводного тактового сигнала в дифференциальный может использоваться трансформатор. Оптимальная эффективность 1273HA044 достигается размещением формирователя очень

близко к тактовому входу 1273НА044, что позволяет подавить негативное влияние линии передачи, например, такое как отражения из-за несогласованности.

Качество сигналов тактовых импульсов и входных данных особенно важно в достижении оптимальных рабочих характеристик. Схема внешнего формирователя тактовых импульсов должна иметь низкий JITTER, подходящие логические уровни и короткие фронты. Хотя короткий фронт тактового сигнала уменьшает JITTER, который проявляет себя как фазовый шум при восстановлении формы выходного аналогового сигнала, высокое усиление широкополосного компаратора тактового входа 1273НА044 допускает использование дифференциального сигнала синусоидальной формы с размахом не менее 0,5 В и минимальной деградацией по уровню шума на выходе.

#### 4.6 Программируемая ФАПЧ

Тактовый вход CLKIN может функционировать или как тактовый сигнал для входных данных (если ФАПЧ разрешен) или как тактовый сигнал данных ЦАП (если ФАПЧ заблокирован), соответственносостоянию бита 7 в четвертом регистре последовательного порта. Принцип работы внутренней схемы синхронизации 1273НА044 в этих двух режимах приведен на рисунках 4.8 и 4.9.

Рисунок 4.9 – ФАПЧ и схема синхроимпульсов с запрещенной ФАПЧ

Тактовый ФАПЧ умножитель и схема распределения вырабатывают необходимую внутреннюю синхронизированную  $1\times$ ,  $2\times$ ,  $4\times$  и  $8\times$  смесь для триггерных защелок, фильтров интерполяторов, модуляторов и ЦАП. Эта схема состоит из фазового детектора, генератора подкачки заряда, управляемого напряжением генератора (ГУН), делителя частоты, схемы распределения тактовых сигналов И регистра управления последовательным портом (SPI). Генератор подкачки дифференциального тактового входа, фазовый детектор, делитель частоты синхросигналов получают питание CLKVCC. распределитель OT ФАПЧ Состояние индицируется логическим сигналов на PLL LOCK, как состояние бита 1, нулевого регистра. Чтобы гарантировать оптимальный фазовый шум от ФАПЧ, умножителя и распределителя тактовых сигналов, питание CLKVCC должно обеспечиваться от чистого аналогового источника. В таблице 4.1 приведена минимальная частота входных данных в зависимости от коэффициента интерполяции и значения делителя ФАПЧ. Если частота передачи входных данных окажется ниже

определенного уровня, то фазовый шум VCO может значительно увеличиться. Частота ГУН зависит от скорости передачи входных данных, коэффициента интерполяции, делителя частоты ГУН и определяется согласно следующей функции:

$\Gamma$ УН (М $\Gamma$ ц) =  $F_{DATA}$  (М $\Gamma$ ц) × Коэффициент Интерполяции × Делитель

Таблица 4.1 – Оптимизация ФАПЧ

| Коэффициент  | Установка | Минимум       | Максимум            |

|--------------|-----------|---------------|---------------------|

| интерполяции | делителя  | $ m f_{DATA}$ | $f_{\mathrm{DATA}}$ |

| 1            | 1         | 32            | 160                 |

| 1            | 2         | 16            | 160                 |

| 1            | 4         | 8             | 112                 |

| 1            | 8         | 4             | 56                  |

| 2            | 1         | 24            | 160                 |

| 2            | 2         | 12            | 112                 |

| 2            | 4         | 6             | 56                  |

| 2            | 8         | 3             | 28                  |

| 4            | 1         | 24            | 100                 |

| 4            | 2         | 12            | 56                  |

| 4            | 4         | 6             | 28                  |

| 4            | 8         | 3             | 14                  |

| 8            | 1         | 24            | 50                  |

| 8            | 2         | 12            | 28                  |

| 8            | 4         | 6             | 14                  |

| 8            | 8         | 3             | 7                   |

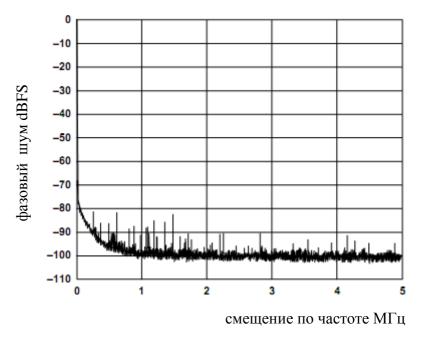

Активация опции дополнения нулями удваивает частоту ГУН. С разрешенным PLL может немного возрасти фазовый шум. На рисунке 4.10 приведен типичный уровень фазового шума 1273HA044 с интерполяцией  $2\times$  и различной скоростью входных данных. Сигнал, синтезированный для измерения фазового шума, состоял только из одной несущей частоты  $f_{DATA}/4$ . Периодический характер этого сигнала устраняет шумы квантования и искажения при измерении.

Рисунок 4.10 – Характеристика фазового шума

Хотя кривые на рисунке 4.10 сливаются воедино, различия условий проясняются в таблице 4.2.

Т а б л и ц а 4.2 — Требуемая норма делителя частоты ФАПЧ относительно  $f_{DATA}$

| f <sub>DATA</sub> (MSPS) | ФАПЧ     | Коэффициент делителя |

|--------------------------|----------|----------------------|

| 125                      | Запрещен | _                    |

| 125                      | Разрешен | 1                    |

| 100                      | Разрешен | 2                    |

| 75                       | Разрешен | 2                    |

| 50                       | Разрешен | 4                    |

В таблице 4.1 поясняются параметры настройки делителя ФАПЧ относительно коэффициента интерполяции и максимальной и минимальной частоты  $f_{DATA}$ . Отметим, что максимальная частота  $f_{DATA}$

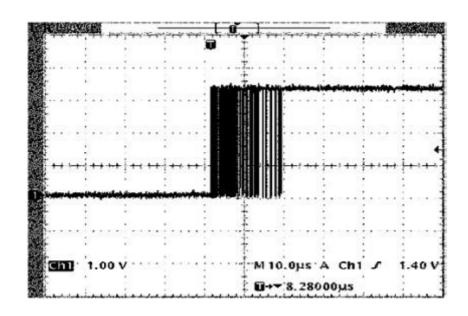

160 MSPS является предельной частотой ввода данных 1273HA044. Однако, максимальная частота меньшая, чем 160 MSPS и все минимальные частоты  $f_{DATA}$  зависят от максимальных и минимальных частот внутреннего генератора управляемого напряжением (ГУН) ФАПЧ. На рисунке 4.11 показана типичная работа сигнала PLL\_LOCK ФАПЧ (вывод 10 или 58), когда ФАПЧ находится в процессе захватывания частоты.

Рисунок 4.11 – Сигнал вывода PLL\_LOCK (вывод 10) в процессе захвата частоты (типичное время захвата)

Важно отметить, что резистор и конденсатор, необходимый для фильтра нижних частот ФАПЧ, являются внутренними. Этого будет достаточно, если частота ввода данных не ниже 10 МГц, иначе потребуются внешняя RC между выводами LPF и CLKVCC.

#### 4.7 Рассеиваемая мощность

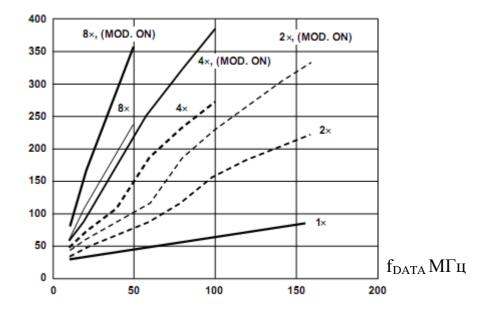

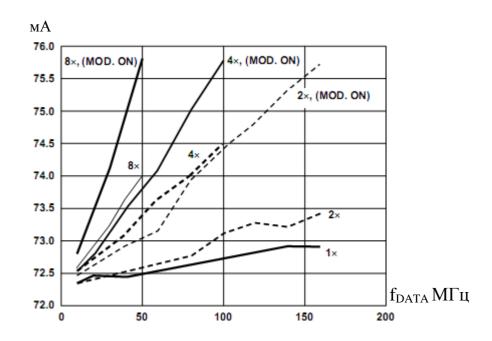

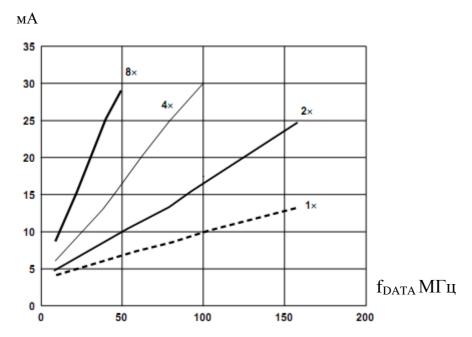

У микросхемы 1273HA044 есть три питающих напряжения: #VCC,  $\cap$ VCC и CLKVCC. На рисунках 4.12 – 4.14 показывается ток, требуемый от каждого из этих питающих напряжений, когда каждое питающее напряжение установлено номиналом 3,3 В. Рассеиваемая мощность  $P_D$  может быть легко получена умножением данных характеристик на величину 3.3. Из рисунка 4.12, видно, что ток  $I_{\#VCC}$  сильно зависит отчастоты входных данных, коэффициента интерполяции и включениявнутреннего цифрового модулятора. Однако ток  $I_{\#VCC}$  относительно нечувствительность тока  $I_{\Pi VCC}$  к скорости входных данных, коэффициенту интерполяции и функции модулятора, но в меньшей степени (< 10 %). На рисунке 4.14 ток  $I_{CLKVCC}$  изменяется в широком диапазоне, тем не менее отвечает только за маленький процент требуемого полного тока источника питания ИС 1273HA044.

Рисунок 4.12 –  $I_{\#VCC}$  относительно  $f_{DATA}$ , коэффициента интерполяции (ФАПЧ запрещен)

Рисунок 4.13 –  $I_{\cap VCC}$  относительно  $f_{DATA}$ , коэффициента интерполяции (ФАПЧ запрещен)

Рисунок  $4.14 - I_{CLKVCC}$  относительно  $f_{DATA}$ , коэффициента интерполяции ( ФАПЧ запрещен)

#### 4.8 Режимы сна и низкого энергопотребления

ИС 1273НА044 обеспечивает два метода для программирования сокращения потребляемой мощности. Когда активирован режим сна, выключаются выходные токи ЦАП, но оставшаяся часть кристалла продолжает функционировать. При завершении режима сна ИС 1273НА044 немедленно возвратится к полному функционированию. В режиме низкого потребления мощности отключаются вся аналоговая и цифровая части за исключением порта SPI. При завершении режима низкого потребления цифровым фильтрам потребуется достаточно много тактов для очистки от случайных данных, полученных во время режима низкого потребления.

## 4.9 Двухпортовый режим ввода данных

Порты ввода цифровых данных могут быть построены как два независимых порта (регистр 2, бит 6 = 0 – режим «два порта») или как один порт (регистр 2, бит 6 = 1 – режим «один порт»). В режиме с двумя портами данные на входах двух портов защелкиваются по восходящему фронту тактовых импульсов (DATACLK). Кроме того, в режиме с двумя портами 1273HA044 может быть запрограммирован так, чтобы генерировать тактовые сигналы DATACLK для внешних схем с целью общей синхронизации данных. Тактовые импульсы ввода данных для внешних схем могут быть доступны или на выводе 10 (DATACLK/PLL\_LOCK) или на выводе 58 (SPI\_SDO). Поскольку вывод 10

может работать как индикатор состояния ФАПЧ, то когда ФАПЧ разрешен, есть несколько вариантов для конфигурирования выводов 10 и 58. Данные варианты описаны ниже.

#### $\Phi$ АПЧ выключен (регистр 4, бит 7 = 0)

регистр 3, бит 7 = 0; DATACLK на вывод 10; регистр 3, бит 7 = 1; DATACLK на вывод 58.

## $\Phi$ АПЧ включен (регистр 4, бит 7 = 1)

```

регистр 3, бит 7 = 0, регистр 1, бит 0 = 0; вывод 10 индикатор ФАПЧ; регистр 3, бит 7 = 1, регистр 1, бит 0 = 0; вывод 58 индикатор ФАПЧ; регистр 3, бит 7 = 0, регистр 1, бит 0 = 1; DATACLK на вывод 10; регистр 3, бит 7 = 1, регистр 1, бит 0 = 1; DATACLK на вывод 58.

```

В режиме с одним портом P2B14 и P2B15 от входных данных порта 2 переопределяются как IQSEL и ONEPORTCLK соответственно. Входные данные в режиме с одним портом поступают на один из двух внутренних каналов, определяемых логическим уровнем IQSEL. Тактовый сигнал ONEPORTCLK генерируется ИС 1273HA044 в этом режиме с целью общей синхронизации данных. ONEPORTCLK формируется с целью чередования входных данных, формируемая частота вдвое больше частоты данных на внутреннем входе любого канала.

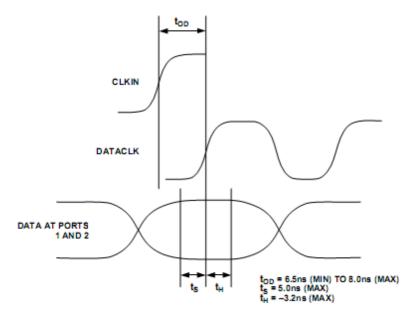

# 4.10 Двухпортовый режим ввода данных, ФАПЧ включена

(Регистр 2, бит 6 = 0 и регистр 4, бит 7 = 1)

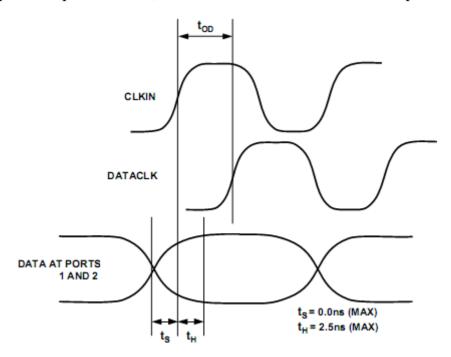

В двухпортовом режиме с включенной ФАПЧ частота CLKIN зависит от частоты входных данных. В режиме с двумя портами вывод 10 (DATACLK/PLL\_LOCK) может быть запрограммирован (регистр управления 1, бит нулевой) так, чтобы функционировать как индикатор состояния ФАПЧ или как тактовый сигнал для входных данных. Когда вывод 10 используется как выход тактового сигнала (DATACLK), его частота равна частоте CLKIN. Данные во входные порты 1273HA044 защелкиваются по восходящему фронту CLKIN. На рисунке 4.15 показывается задержка  $t_{\rm OD}$  между положительным фронтом CLKIN и положительным фронтом DATACLK, а так же длительности установления  $t_{\rm S}$  и необходимого удержания  $t_{\rm H}$  для данных портов 1 и 2. Длительности

установления и хранения входных данных, приведенные на рисунке 4.15, даны относительно CLKIN. Отметим, что в двухпортовом режиме (ФАПЧ разрешен или блокирован) частота ввода данных на входах фильтра интерполятора такая же, как и частота ввода данных портов 1 и 2.

Рисунок 4.15 — Требования синхронизации в двухпортовом режиме с разрешенным ФАПЧ

Частота выборок выходных данных ЦАП в двухвпортовом режиме равна частоте тактирования входных данных, умноженной на коэффициент интерполяции. Если используется функция дополнения нулями, скорость выборки ЦАП удваивается.

#### **4.11** Инверсия DATACLK

(Управляющий регистр 2, бит 4)

Программированием этого бита сигнал DATACLK, который показан на рисунке 4.15, может быть инвертирован. С разрешенной инверсией  $t_{\rm OD}$  определяется как задержка между положительным фронтом CLKIN и отрицательным фронтом DATACLK. Никаких других изменений в синхронизации не произойдет.

# **4.12** Нагрузочная способность формирователя DATACLK

(Управляющий регистр 2, бит 5)

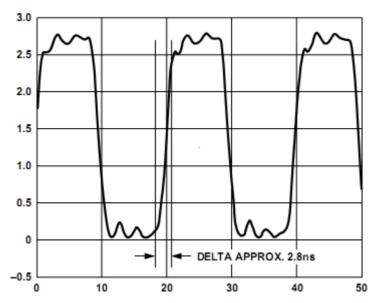

Вывод DATACLK может работать при токе больше 10 мА и нагрузке 330 Ом, обеспечивая время нарастания 3 нс. На рисунке 4.16 показывается DATACLK, работающий при активной нагрузке 330 Ом на частоте 50 МГц. При разрешенной опции интенсивности формирователя (управляющий регистр 2, бит 5) амплитуда DATACLK будет увеличена приблизительно на 200 мВ.

Рисунок 4.16 – Мощность формирователя нагрузка 330 Ом, частота 50 МГц

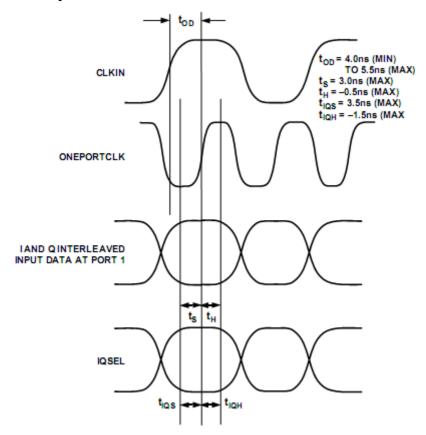

#### 4.13 Однопортовыый режим, ФАПЧ включена

(Регистр 2, бит от 6 = 1 и регистр 4, бит от 7 = 1)

В режиме с одним портом каналы от I и Q принимают свои данные из чередующегося потока на цифровом входе порта 1. На выводе 35, определенном как выход (ONEPORTCLK), генерируются тактовые импульсы с частотой вдвое большей внутренней частоты ввода данных каналов I и Q. Частота CLKIN равна внутренней частоте ввода данных каналов I и Q.

Выбор канала I или Q для защелкивания данных определяется логическим уровнем на выводе 34, определенном как вход (IQSEL, когда 1273НА044 работает в однопортовом режиме), а защелкивание данных происходит по положительному фронту ONEPORTCLK. IQSEL = 0 будет защелкивать данные в канал I, а IOSEL = 1 будет защелкивать данные в канале Q. Возможна инверсия выбора каналов I и Q установкой бита 1 регистра 02 в инверсное состояние (логической единицы). На рисунке 4.17

показываются требования синхронизации для входных данных и для входа IQSEL.

Отметим, что коэффициент интерполяции  $1 \times$  в режиме с одним портом недоступен.

Рисунок 4.17 — Требования синхронизации в режиме с одним портом, с включенной ФАПЧ

Частота выходных выборок ЦАП в однопортовом режиме равна частоте CLKIN, умноженной на коэффициент интерполяции. Если используется функция заполнения нулями, частота выборки ЦАП еще удваивается.

# 4.14 Инверсия ONEPORTCLK

(Управляющий регистр 02, бит 2)

Программированием этого бита сигнал ONEPORTCLK, который показан на рисунке 4.17, может быть инвертирован. С разрешенной инверсией  $t_{OD}$  определяется как задержка между положительным фронтом внешнего тактового генератора и отрицательным фронтом ONEPORTCLK. Время установления  $t_{\rm S}$  и время удержания  $t_{\rm H}$  определяются относительно

## 4.15 Нагрузочная способность формирователя ONEPORTCLK

Нагрузочная способность ONEPORTCLK идентична DATACLK в двухпортовом режиме, смотри рисунок 4.16.

#### 4.16 IQ спаривание

(Управляющий регистр 02, бит 0)

В режиме с одним портом чередующиеся данные фиксируются на внутренней защелке ИС 1273НА044 каналов I и Q попарно. Порядок защелкивания внутри пары определен этим управляющим регистром.

Последующее – пример этого влияния на входящие чередующиеся данные.

Задается следующий чередующийся поток данных, где данные указаны в единицах полной шкалы (смотри таблицы 4.3 - 4.5).

Таблица 4.3

| Ι   | Q   | I | Q | I   | Q   | I | Q | I   | Q   |

|-----|-----|---|---|-----|-----|---|---|-----|-----|

| 0,5 | 0,5 | 1 | 1 | 0,5 | 0,5 | 0 | 0 | 0,5 | 0,5 |

С установкой регистра управления в нуль (I — первый), данные будут появляться на внутренних входах каналов в следующем временномпорядке: Таблица 4.4

| I канал | 0,5 | 1 | 0,5 | 0 | 0,5 |

|---------|-----|---|-----|---|-----|

| Q канал | 0,5 | 1 | 0,5 | 0 | 0,5 |

С установкой регистров управления в единицу (Q – первый), данные будут появляться на внутренних входах каналов в следующем временном порядке:

Таблица 4.5

| I канал | 0,5 | 1   | 0,5 | 0   | 0,5 | X   |

|---------|-----|-----|-----|-----|-----|-----|

| Q канал | У   | 0,5 | 1   | 0,5 | 0   | 0,5 |

Значения х и у представляют последующее значение I и предыдущее значение Q.

#### 4.17 Двухпортовыый режим, ФАПЧ выключена

В режиме с выключенной ФАПЧ тактовый сигнал с частотой выборок ЦАП должен быть приложен к CLKIN. Внутренние делители тактового сигнала ИС 1273НА044 синтезируют сигнал DATACLK на выводе 10, который работает с частотой входных данных и может использоваться ДЛЯ синхронизации входных данных. Данные защелкиваются во входы портов 1 и 2 по положительному фронту DATACLK. Частота DATACLK определяется как частота CLKINделенная на коэффициент интерполяции. С включенной функцией дополнения нулями это деление увеличивается вдвое. На рисунке 4.18 показывается задержка между фронтом CLKIN и фронтом DATACLK, а так же ts и tн в этом режиме.

Программируемые режимы инверсии DATACLK и мощности DATACLK, описанные в предыдущем разделе (ФАПЧ включена, двухпортовый режим), имеют при выключенной ФАПЧ идентичные функциональные возможности.

Тактовый сигнал данных СLK, получаемый делением частоты ЦАП, в этом режиме может быть запрограммирован (через регистр 3, битом 7) таким образом, чтобы поступать на вывод SPI\_SDO, а не на вывод DATACLK. В некоторых приложениях это может улучшить комплексное подавление помех от зеркального канала. Когда SPI\_SDO будет использоваться как выход для тактирования данных, то t<sub>OD</sub> увеличится на 1,6 нс.

Рисунок 4.18 – Требования синхронизации при двухпортовом режиме, с выключенной ФАПЧ

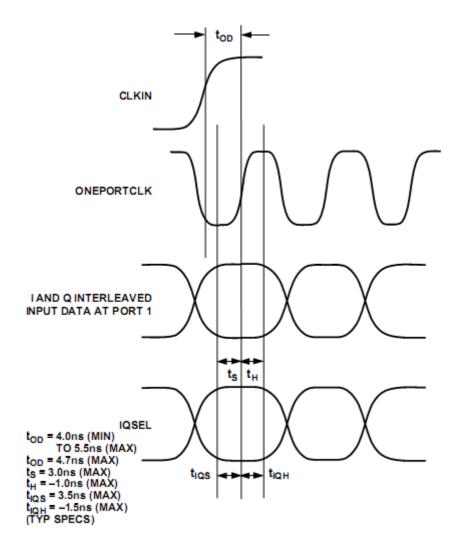

#### 4.18 Однопортовый режим, ФАПЧ выключена

В режиме с одним портом ИС 1273HA044 получает данные как чередующийся поток на порт 1. Частота тактового сигнала ONEPORTCLK при чередующихся данных равна удвоенной внутренней частоте ввода данных каналов I и Q. ONEPORTCLK доступен для синхронизации данных на выводе 35. С выключенной ФАПЧ частота выборок ЦАП будет равна СLKIN. Внутренние делители синтезируют сигнал ONEPORTCLK на выводе 35. Выбор данных для канала I или канала Q определяется логическим уровне на выводе 34 (IQSEL, когда ИС 1273HA044 находится в режиме с одним портом) по положительному фронту ONEPORTCLK. В этих условиях IQSEL = 0 будет защелкивать данные в канал I, в то время как IOSEL = 1 будет защелкивать данные в канал Q. Возможна инверсия выбора каналов I и Q установкой бита 1 регистра 2 в инверсное состояние (логической единицы). На рисунке 4.19 показывются требования синхронизации для входных данных и для входа IOSEL.

Отметим, что коэффициент интерполяции  $1 \times$  в режиме с одним портом недоступен.

Рисунок 4.19 – Требования синхронизации в режиме с одним портом и выключенной ФАПЧ

Режим с одним портом очень полезен для связи с устройствами, в которых имеются два чередующихся цифровых канала данных (мультиплексированных). Такие программируемые режимы, как инверсия ONEPORTCLK, мощность формирователя ONEPORTCLK и спаривание IQ, описанные в предыдущем разделе (ФАПЧ включена, однопортовый режим), имеют с выключенной ФАПЧ идентичные функциональныевозможности.

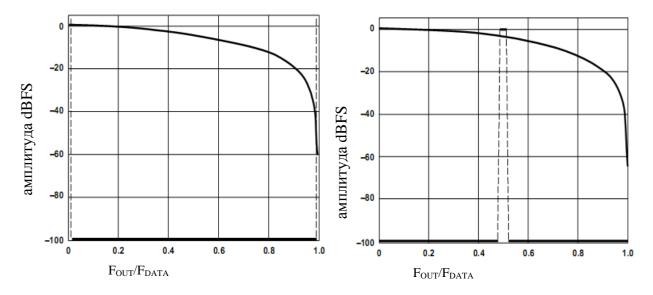

# 4.19 Режимы цифрового фильтра

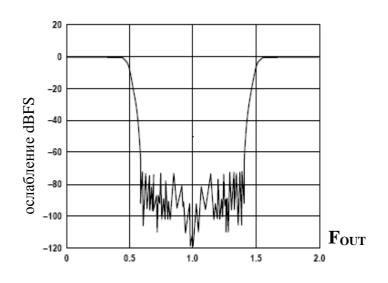

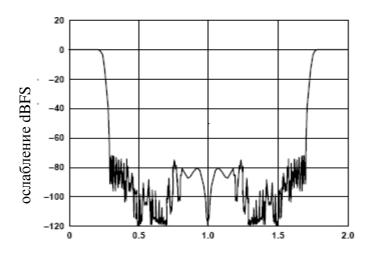

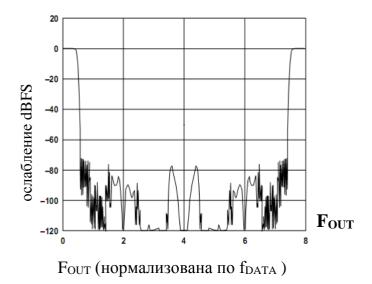

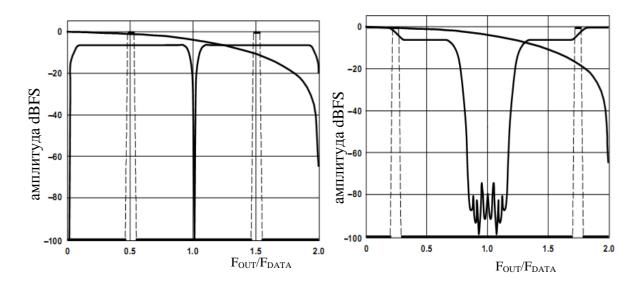

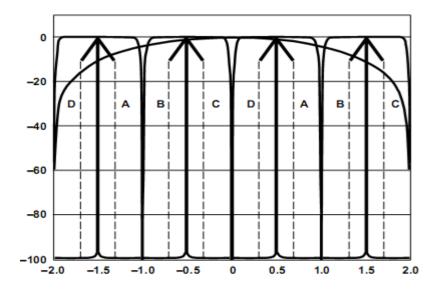

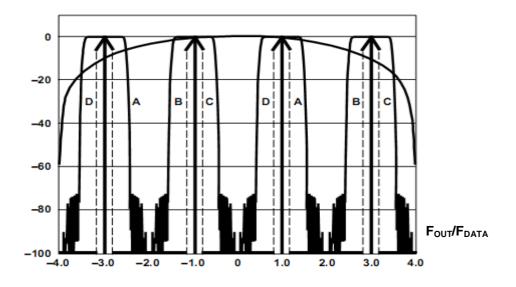

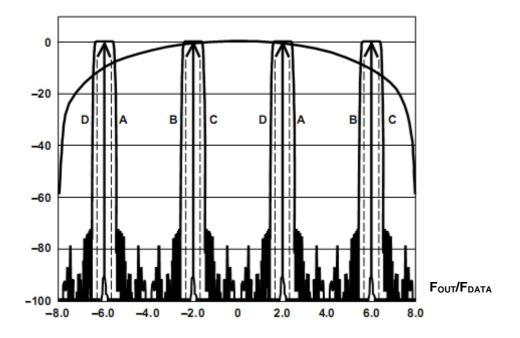

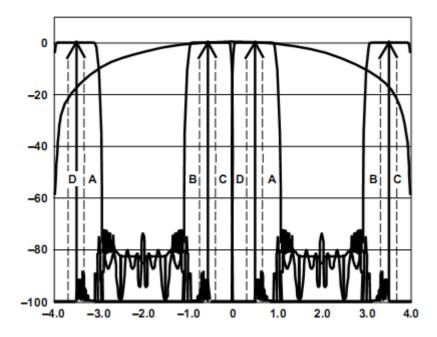

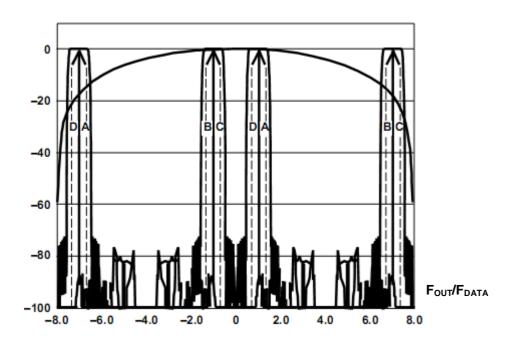

Каналы I и Q данных ИС 1273НА044 имеют собственные независимые полуполосные КИХ-фильтры. Каждый канал содержит три КИХ-фильтра, обеспечивая коэффициент интерполяции до 8×. Коэффициент интерполяции определен первым регистром управления, битами 7 и 6. На рисунках 4.20 — 4.22 показаны отклики цифровых

фильтров, когда ИС 1273НА044 работает в режимах с интерполяцией  $2 \times$ ,  $4 \times$ ,  $8 \times$ . Частотная ось этих рисунков нормализована к частоте входных данных ЦАП. Как показано на рисунках, цифровые фильтры (таблицы 4.6 - 4.8) могут обеспечить подавление вне полосы пропускания больше, чем на 75 дБ.

Т а б л и ц а 4.6 — Полудиапазонный фильтр № 1 (43 коэффициента)

| PINIBIP .= | 1 (15 Respons |

|------------|---------------|

| Отвод      | Коэффициент   |

| 1, 43      | 8             |

| 2, 42      | 0             |

| 3, 41      | -29           |

| 4, 40      | 0             |

| 5, 39      | 67            |

| 6, 38      | 0             |

| 7, 37      | -134          |

| 8, 36      | 0             |

| 9, 35      | 244           |

| 10, 34     | 0             |

| 11, 33     | -414          |

| 12, 32     | 0             |

| 13, 31     | 673           |

| 14, 30     | 0             |

| 15, 29     | -1 079        |

| 16, 28     | 0             |

| 17, 27     | 1 772         |

| 18, 26     | 0             |

| 19, 25     | -3 280        |

| 20, 24     | 0             |

| 21, 23     | 10 364        |

| 22         | 16 384        |

F<sub>OUT</sub> (нормализована по f<sub>DATA</sub>)

Рисунок 4.20–AЧX фильтра интерполятора 2×

Т а б л и ц а 4.7 — фильтр № 2

(19 коэффициентов)

| ` | 1 1   |             |

|---|-------|-------------|

|   | Отвод | Коэффициент |

|   | 1, 19 | 19          |

|   | 2, 18 | 0           |

|   | 3, 17 | -120        |

|   | 4, 16 | 0           |

|   | 5, 15 | 438         |

|   | 6, 14 | 0           |

|   | 7, 13 | -1,288      |

|   | 8, 12 | 0           |

|   | 9, 11 | 5047        |

|   | 10    | 8192        |

F<sub>OUT</sub> (нормализована по f<sub>DATA</sub> )

Рисунок 4.21 — АЧХ фильтра-интерполятора  $4\times$

Т а б л и ц а 4.8 — Полудиапазонный фильтр № 3 (11 коэффициентов)

| Отвод | Коэффициент |

|-------|-------------|

| 1, 11 | 7           |

| 2, 10 | 0           |

| 3, 9  | -53         |

| 4, 8  | 0           |

| 5, 7  | 302         |

| 6     | 512         |

Рисунок 4.22 — АЧХ фильтра интерполятора  $8\times$

# 4.20 Амплитудная модуляция

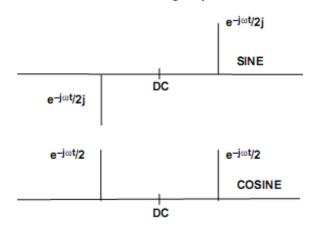

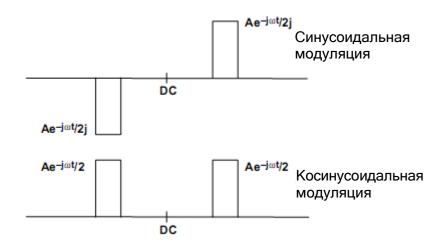

Для двух синусоидальных сигналов одной частоты, но с различием по фазе на 90°, точка отсчета во времени может быть взята таким образом, что сигнал с опережающей фазой является косинусоидальным, а сигнал с отстающей фазой является синусоидальным. Анализ комплексных переменных говорит о том, что косинусоидальный сигнал может быть определен как имеющий положительные действительные компоненты в положительной и отрицательной частотных областях, в то время как синусоидальный сигнал состоит из мнимых компонентов: положительной в положительной частотной области и отрицательной в отрицательной частотной области. Это показано на рисунке 4.23.

Рисунок 4.23 — Реальные и мнимые компоненты синусоидального и косинусоидального сигналов

Амплитудная модуляция, осуществляемая синусоидальным или косинусоидальным сигналами, является сверткой модулируемого сигнала с области. модулирующей несущей В частотной Амплитудное масштабирование модулированного сигнала уменьшает положительные и отрицательные боковые сигналы в два раза. Данное масштабирование очень обсуждении различных режимов модуляции. Фазовые соотношения модулированных сигналов зависят от того, является ли частота синусоидальной или косинусоидальной. Примеры модуляции синусом и косинусом приведены на рисунке 4.24.

Рисунок 4.24 – Амплитудная модуляция синусом и косинусом

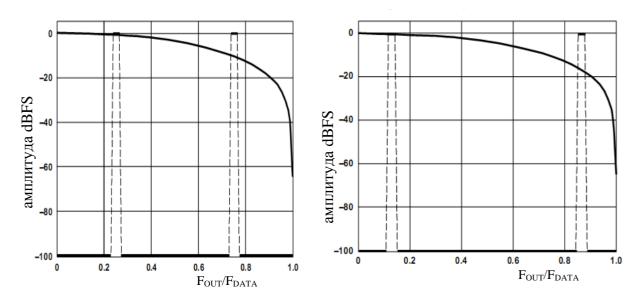

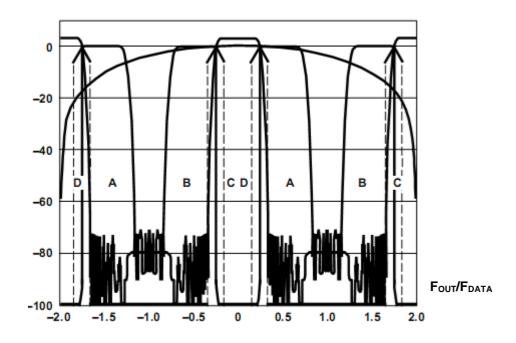

# 4.21 Модуляция, интерполяция выключена

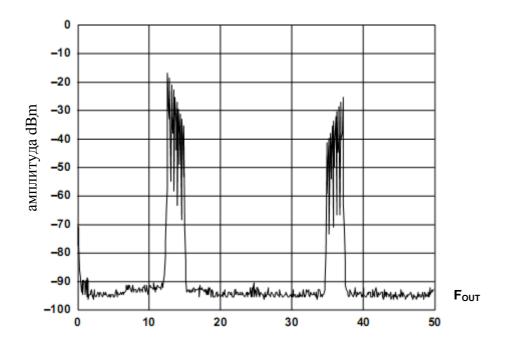

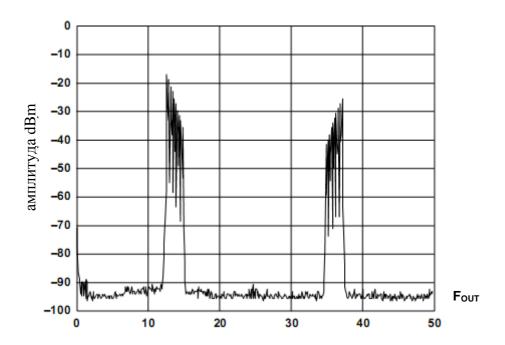

Управляющим регистром 1, битами 7 и 6, установленными в нулевое состояние, блокируется функция интерполяции на ИС 1273НА044. На рисунках 4.25 – 4.28 показаны выходные спектральные характеристикиЦАП 1273НА044 в различных модуляционных режимах, с блокированными фильтрами-интерполяторами. Частота модуляции определяется уровнем управляющего первого регистра, битами 5 и 4. Высокие прямоугольники представляют области цифрового спектра узкополосного модулирующего сигнала. Сравнивая цифровой спектр в области спада ЦАП sin(x)/x, можно сделать оценку требуемых характеристик ДЛЯ восстанавливающих фильтров. Заметим так же, по предыдущему обсуждению амплитудной спектральные модуляции, что компоненты (когда модуляция осуществляется  $f_{DAC}/4$  или  $f_{DAC}/8$ ) масштабируются с поправочным коэффициентом 2. Когда модуляция  $f_{DAC}/2$ , спектральные компоненты суммируются конструктивно и эффект масштабирования отсутствует. Это суммирование не отражено на графиках для  $f_{DAC}/4$  и  $f_{DAC}/8$ : здесь амплитуды прямоугольников должны составлять -6 дБ.

Влияние цифровой модуляции на спектральную характеристику ЦАП, интерполяция выключена.

Рисунок 4.25-Модуляция блокирована

Рисунок 4.26–Модуляция  $f_{DAC}/2$

Рисунок 4.27 -Модуляция  $= f_{DAC}/4$  Рисунок

Рисунок 4.28 -Модуляция  $= f_{DAC}/8$

# 4.22 Модуляция, интерполяция 2 ×

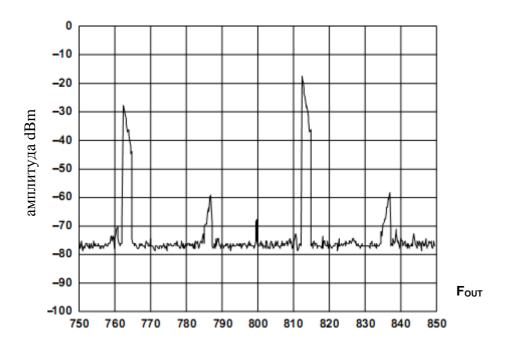

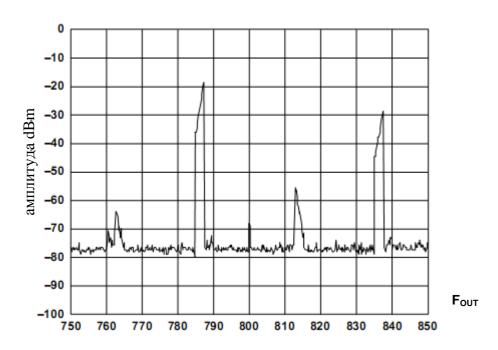

Коэффициент интерполяции ИС 1273НА044 2 × устанавливается первым регистром управления, битами 7, 6 установленными в состояние 01. Модуляция достигается поочередным умножением отсчетов на выходе фильтра-интерполятора последовательностью (+1, -1). На рисунках 4.29 – 4.32 показана спектральная характеристика выхода ЦАП с 2× интерполяцией в различных режимах модуляции (опять высокие прямоугольники на рисунке). Преимущество становится очевидным, и на рисунках это видно, что при обработке фильтрами интерполяторами до цифрового модулятора отсутствуют образы, которые обычно присутствуют

в спектре около значимой точки. Также на рисунках видно, что полоса пропускания фильтров интерполяторов может быть сдвинута, давая эквивалент цифрового фильтра высоких частот.

Стоит обратить внимание, что при использовании режима модуляции  $f_{DAC}/4$  нет полосы затухания, так как края полос совпадают друг с другом. В режиме модуляции  $f_{DAC}/8$  масштабирование амплитуды происходит только на части полосы пропускания цифрового фильтра из-за конструктивных добавлений только лишь к той части полосы пропускания.

Рисунок 4.29 – Интерполяция 2×, модуляция блокирована

Рисунок 4.30 — Интерполяция  $2 \times$ , модуляция =  $f_{DAC}/2$

Рисунок 4.31 — Интерполяция  $2 \times$ , модуляция =  $f_{DAC}/4$

Рисунок 4.32 — Интерполяция  $2 \times$ , модуляция =  $f_{DAC}/8$

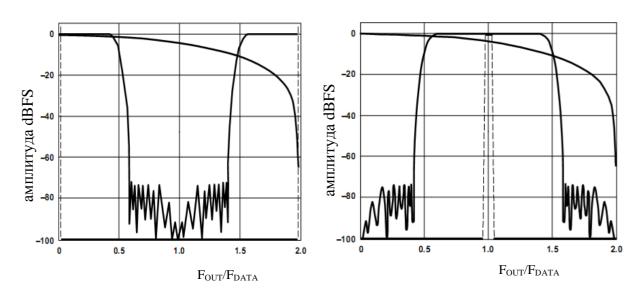

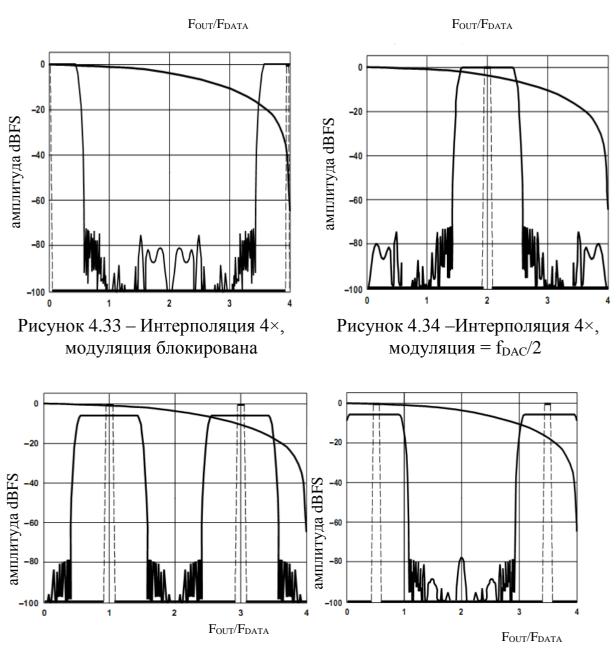

# 4.23 Модуляция, интерполяция 4 ×

Коэффициент интерполяции  $4 \times \text{ИС}$  1273HA044 устанавливается первым регистром управления, битами 7 и 6, установленными в состояние 10. Модуляция достигается поочередным умножением отсчетов на выходе фильтра-интерполятора на элементы последовательности (0, +1, 0, -1). На рисунках 4.33 - 4.36 изображена спектральная характеристика выхода ЦАП 1273HA044 с  $4 \times$ интерполяцией в различных режимах модуляции.

Рисунок 4.35 — Интерполяция  $4 \times$ , модуляция =  $f_{DAC}/4$

Рисунок 4.36 — Интерполяция  $4 \times$ , модуляция =  $f_{DAC}/8$

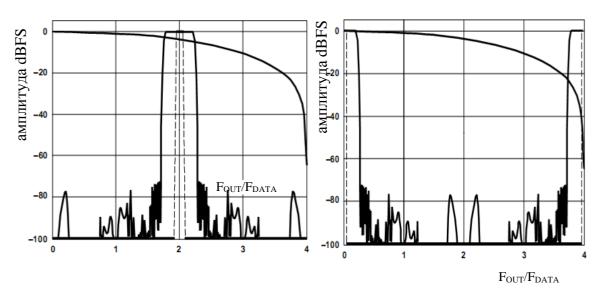

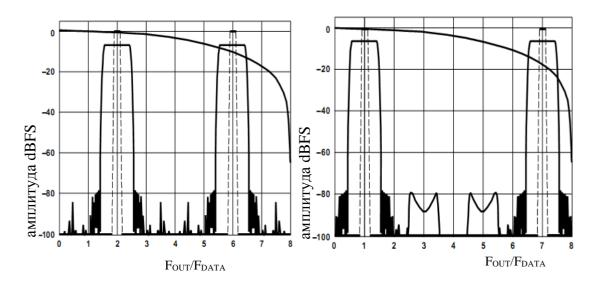

# 4.24 Модуляция, интерполяция 8 ×

Коэффициент интерполяции  $8 \times \text{ИС}$  1273HA044 устанавливается первым регистром управления, битами 7 и 6, установленными в состояние 11. Модуляция достигается поочередным умножением отсчетов на выходе фильтра-интерполятора последовательностью (0; +0,707; +1;

+0,707; 0; -0,707; -1; -0,707). На рисунках 4.37-4.40 изображена спектральная характеристика ЦАП 1273НА044 с  $8 \times$  интерполяцией в различных режимах модуляции. Анализируя рисунки можно видеть, что чем выше коэффициент интерполяции, тем проще восстанавливающие фильтры на выходе ЦАП.

Рисунок 4.37 – Интерполяция 8×, модуляция блокирована

Рисунок 4.38 — Интерполяция  $8 \times$  модуляция =  $f_{DAC}/2$

Рисунок 4.39 — Интерполяция  $8 \times$ , модуляция =  $f_{DAC}/4$

Рисунок 4.40 — Интерполяция  $8 \times$ , модуляция =  $f_{DAC}/8$

# 4.25 Нуль-дополнение

(Управляющий регистр 1, бит 3)

Как показано на рисунке 4.41, на верхней границе диапазона  $f_{DAC}$  происходит обнуление частотной характеристики на выходе ЦАП (после интерполяции, модуляции и восстановления ЦАП). Это происходит из-за присущего цифро-аналоговому преобразованию спада типа  $\sin(x)/x$ . В приложениях, где рабочий частотный спектр ниже  $f_{DAC}/2$ , это не создает проблем. Отметим, что при  $f_{DAC}/2$  затухание из-за  $\sin(x)/x$  составляет 4 дБ. В более широкополосных применениях (RF) этот спад может быть проблемой из-за увеличенной неравномерности амплитудной характеристики фильтра в рабочей полосе частот и уменьшения амплитуды сигнала.

Рассмотрим приложения, где цифровые данные ИС 1273HA044 представляют полосу около частоты  $f_{DAC}/4$  с шириной спектра  $f_{DAC}/10$ . Сигнал, восстановленный 1273HA044, в пределах своего спектра претерпевает изменение амплитуды только на 0,75 дБ. Однако, тот же самый сигнала на частоте  $3 \times f_{DAC}/4$  пострадает из-за неравномерности АЧХ на 3,93 дБ. Эта гармоника может быть удовлетворительным сигналом в режиме промежуточной частоты, при использовании одного из режимов модуляции ИС 1273HA044. Этот спад частотных спектров можно увидеть на рисунках 4.31-4.40, где эффект интерполяции и модуляции вполне очевиден.

Рисунок  $4.41 - Эффект нуль-дополнения ЦАП <math>\sin(x)/x$

Чтобы улучшить равномерность АЧХ в полосе спектра полезного сигнала, может быть включен режим нуль-дополнения установкой соответствующего бита управляющего регистра в состояние логической единицы. Эта опция увеличивает соотношение  $f_{DAC}/f_{DATA}$  в два раза, удваивая частоту выборки ЦАП и вставляя выборку, равную середине шкалы (т. е. 1000 0000 0000 0000, что эквивалентно выборке нулевого значения сигнала) после каждой выборки данных, исходящей от интерполирующего фильтра. Данная функция важна, поскольку затронет коэффициент делителя ФАПЧ, чтобы сохранить VCO в пределах его оптимального диапазона частот. Отметим, что нуль-дополнениевключается в цепь цифрового сигнала на выходе цифрового модулятора, перед ЦАП.

Результирующий эффект – увеличение частоты выборки выхода ЦАП в два раза с перемещением спада в передаточной функции  $\sin(x)/x$  ЦАП на удвоенную первоначальную частоту. На рисунке 4.41 очевидна потеря на 6 дБ в амплитуде на низких частотах.

Важно понять, что нуль-дополнение не изменяет положение спектра, а оказывает влиянте на амплитуду и равномерность в полосе пропускания. Например, неравномерность амплитуды в полосе пропускания в предыдущем примере на частоте  $3 \times f_{DATA}/4$  теперь улучшена до 0,59 дБ, в то время как уровень сигнала увеличился не намного: от -10,5 дБ до -8,1 дБ.

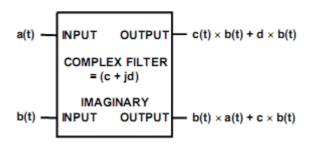

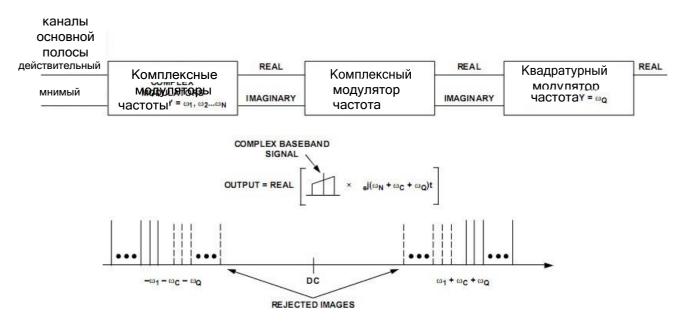

# 4.26 Модуляция (режим комплексного микширования)

(Управляющий регистр 1, бит 2)

В режиме комплексного микширования два цифровых модулятора ИС 1273НА044 объединены для обеспечения комплексной модуляционной функции. В соединении с внешним квадратурным модулятором комплексная модуляция может использоваться для реализации архитектуры передачи с подавленной боковой полосой. Функциякомплексной модуляции может быть запрограммирована для  $e^{+j\omega t}$  или  $e^{-j\omega t}$ , чтобы подавлять верхнюю или нижнюю боковую полосу. Как и в режиме реальной модуляции, частота модуляции  $\omega$  может быть запрограммирована через порт параллельного интерфейса SPI для  $f_{DAC}/2$ ,  $f_{DAC}/4$ , и  $f_{DAC}/8$ , где  $f_{DAC}$  – частота выборок ЦАП.

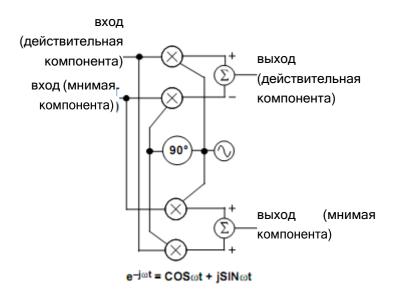

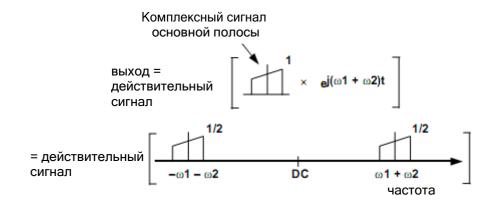

# 4.27 Операции на комплексных сигналах

Комплексные сигналы не могут быть реализованы вне компьютерного моделирования. Однако два канала данных, состоящие из действительных данных, могут быть определены как действительная и мнимая составляющие комплексного сигнала. Часто выбирают метод, когда I — действительный, а Q — мнимый информационные каналы. Используя определенную на рисунке 4.42 архитектуру, можно реализовать систему, оперирующую на комплексных сигналах и дающую комплексный (действительный и мнимый) выходной сигнал.

Если функция модуляции  $(e^{+j\omega t})$ . желательна комплексная соответствуют действительные составляющие системы И мнимые действительным и мнимым составляющим  $e^{+j\omega t}$  или  $\cos(\omega t)$  и  $\sin(\omega t)$ . Как показано на рисунке 4.42, комплексная функция модуляции может быть реализована применением этих компонентов к структуре, приведенной на рисунке 4.43.

Рисунок 4.42 – Реализация комплексной системы

Рисунок 4.43 – Реализация комплексного модулятора

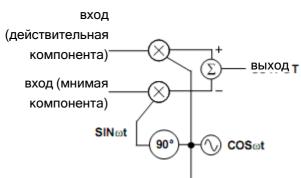

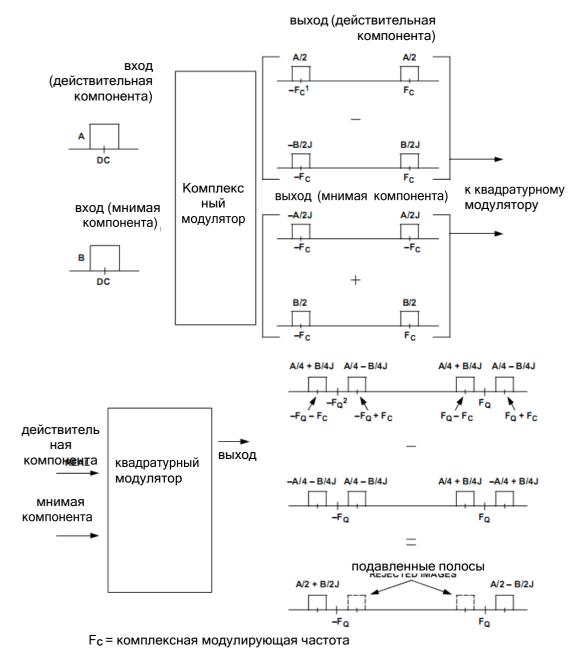

### 4.28 Комплексная модуляция и подавление боковой полосы

В традиционной передаче применяется двухступенчатое преобразование с повышением частоты, в котором сигнал основной полосы модулирован одной несущей к промежуточной частоте и затем модулируется во второй раз, передающей частотой. Хотя этот подход имеет несколько преимуществ, главный недостаток в том, что около передающей частоты создаются две боковые полосы. Необходима только одна полоса, другая полоса является зеркальной копией. Если нежелательная полоса не отфильтрована, обычно аналоговыми компонентами, то на ее передачу расходуется мощность и часть полосы пропускания, доступная в системе.

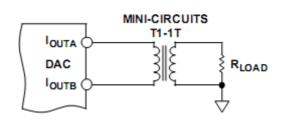

Более эффективный метод подавления нежелательного спектра может быть достигнут использованием комплексного модулятора с последующим квадратурным модулятором. На рисунке 4.44 приведена блок-схема квадратурного модулятора. Отметим, что фактически это половина комплексного модулятора: его действительный выход. Полное преобразование с повышением частоты представляет собой пару каскадов с комплексным преобразованием сигнала, действительный выход которой превращается в передаваемый сигнал.

Рисунок 4.44 – Квадратурный модулятор

Всё преобразование с повышением частоты от основной полосы частот к передающей частоте представлено на рисунке 4.45. Результирующий спектр, показанный на рисунке 4.46, представляет собой комплексные данные, состоящие из действительного и мнимого каналов основной полосы частот, модулированных ортогональными (косинус и отрицательный синус) несущими на передающей частоте. Важно помнить,

что в этом применении (два канала данных основной полосы частот) подавление боковой полосы не зависит от данных входных каналов микросхемы.

Фактически подавление зеркальной боковой полосы произойдет или в каком-то одном или в обоих активных каналах ИС 1273НА044. Заметим, что изменением знака синусоидального множителя в комплексном модуляторе могла бы быть подавлена верхняя боковая полоса с одновременным прохождением нижней боковой. Это легко сделать выбором  $e^{+j\omega t}$  (регистр 1, бит 1). В комплексной форме на рисунке 4.46 представлено двухступенчатое преобразование с повышением частоты комплексного сигнала основной полосы к несущей.

F<sub>Q</sub> = квадратурная модулирующая частота

Рисунок 4.45 — Двухступенчатое преобразование с повышением частоты и подавлением одной боковой полосы

Рисунок 4.46 – Двухступенчатое комплексное преобразование с повышением частоты

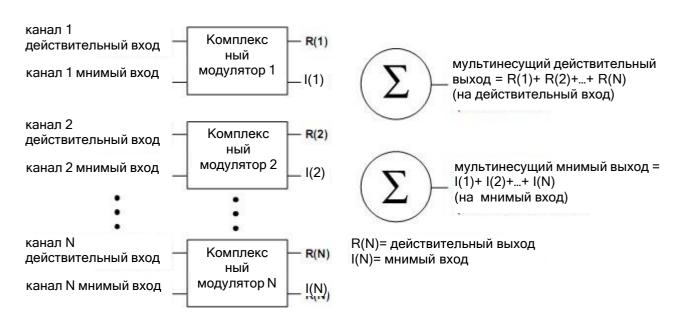

### 4.29 Подавление боковой полосы модулированных несущих

Как показано на рисунке 4.45 подавление зеркальной полосы может быть достигнуто подачей основной полосы частот на 1273НА044 и последующим 1273НА044 с квадратурной модуляцией. Чтобы обрабатывать несущих с возможностью подавления боковой полосы, множество необходимо каждую несущую комплексно модулировать. Как показано на рисунке 4.47, один или множество комплексных модуляторов могут быть использованы для синтеза комплексных несущих. Эти комплексные несущие суммируются и подаются на действительный и мнимый входы 1273НА044. Система, в которой множество широкополосных сигналов комплексно-модулированы и затем поданы на реальные и мнимые входы ИС 1273НА044, с последующим квадратурным модулятором, показана на рисунке 4.48, на котором также описываются передаточная характеристика этой системы и выходной спектр. Следует отметить подобие передаточных функций, приведенных на рисунках 4.48 и

4.46. На рисунке 4.48 показан дополнительный каскад комплексного модулятора для суммирования множества несущих на входах 1273НА044. Как и на рисунке 4.44, подавление боковой полосы не зависит от действительных или мнимых данных в основной полосе частот в любом канале. Подавление боковой полосы произойдет, если действительные или мнимые данные, или и те и другие, будут присутствовать в канале в основной полосе частот.

Важно помнить, что величина комплексного сигнала может быть выше в 1,414 раза величины его действительного или мнимого компонента.

Из-за увеличения амплитуды сигнала на 3 дБ действительные и мнимые входы на ИС 1273НА044 должны быть, по крайней мере, на 3 дБ ниже полного масштаба при работе с комплексным модулятором. Переполнение в комплексном модуляторе приведет к ощутимым искажениям на выходе ЦАП.

Рисунок 4.47 – Синтез комплексного сигнала на нескольких несущих

Рисунок 4.48 – Подавление боковой полосы с мультинесущим сигналом

Комплексная несущая, синтезируемая в цифровом модуляторе ИС 1273HA044, достигнута созданием двух реальных цифровых несущих,

сдвинутых по фазе на 90 °. Несущие не могут быть созданы модулятором, работающим на частоте  $f_{DAC}/2$ . По этой причине комплексная модуляция осуществляется только с коэффициентами модуляции  $f_{DAC}/4$  и  $f_{DAC}/8$ .

Области A и B на рисунках 4.49 - 4.54 являются результирующим комплексным сигналом, описанным ранее, когда комплексная модуляция в 1273НА044 осуществляется термом  $e^{+j\omega t}$ . Области C и D — результирующий комплексный сигнал, описанный ранее, с положительными частотными компонентами, когда комплексная модуляция в 1273НА044 осуществляется термом  $e^{-j\omega t}$ . Аналоговый квадратурный модулятор после ИС 1273НА044 по своей природе модулирует термом  $e^{+j\omega t}$ .

#### Область А

Область А является результатом преобразования с повышением в основной частоты комплексного сигнала полосе частот. рассматривается как комплексный сигнал, то только изображения вобласти А останутся. У комплексного сигнала А в цифровой области, состоящего только из положительных частотных компонентов, есть изображения в позитивных нечетных областях Найквиста (1, 3, 5...), то же самое есть и в отрицательных четных областях. Подавление помех от зеркального канала в любой области Найквиста станет более очевидным при использовании квадратурного модулятора. Изображения появятся на действительном и мнимом выводах ИС 1273НА044, так же как и на выводе квадратурного модулятора, на графике спектра которого в центре представлен гетеродин квадратурного модулятора , а в горизонтальном масштабе теперь представлено смещение от частоты гетеродина.

#### Область В

Область В комплексно сопряжена с областью А. Чтобы увидеть действительные и мнимые данные ЦАП 1273НА044, необходимо использовать анализатор спектра, тогда область В будет появляться в спектре. Однако, на выходе квадратурного модулятора, область В будет подавлена.

#### Область С

Область С является результатом преобразования с понижением частоты, поскольку несущая модуляции есть  $\mathbf{e}^{-\mathbf{j}\omega t}$ . Если рассматривается как комплексный сигнал, изображения останутся только в области С. Это

изображение появится на действительных и мнимых выводах микросхемы, так же как и на выводе квадратурного модулятора, на графике спектра которого в центре представлен гетеродин квадратурного модулятора, а в горизонтальном масштабе теперь представлено смещение от частоты гетеродина.

#### Область **D**

Область D комплексно сопряжена с областью С. Чтобы увидеть действительные и мнимые данные ЦАП 1273НА044, необходимо использовать анализатор спектра, тогда область D появится в спектре. Однако на выходе квадратурного модулятора область D будет подавлена.

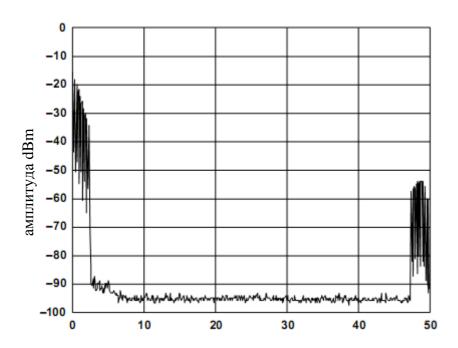

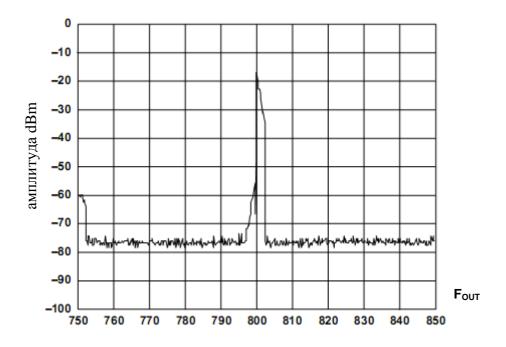

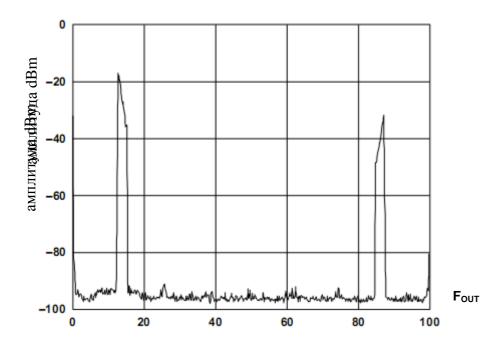

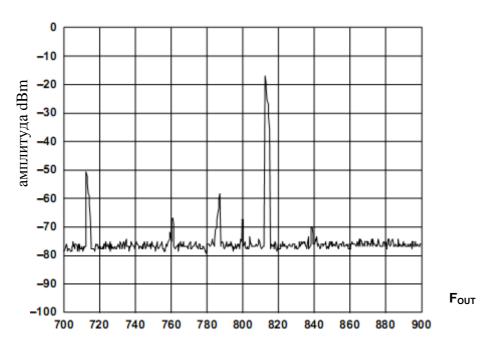

На рисунках 4.55 - 4.62 показан отклик ИС 1273HA044 и AD8345, заданный входным комплексным сигналом 1273HA044 и изображенный на рисунке 4.55. Результаты на этих графиках были получены со скоростью передачи данных 12,5 MSPS на входе ИС 1273HA044. При коэффициенте интерполяции  $4 \times$  или  $8 \times$  скорость выходных данных ЦАП 50 MSPS или 100 MSPS, соответственно. Как результат, верхний диапазон выходного спектра на этом графике является первой нулевой точкой спада  $\sin(x)/x$  и ассиметрия выходных изображений ЦАП (или зеркальных каналов) представляет спад по спектру  $\sin(x)/x$ . Внутренняя фазовая автоподстройка разрешена. В дополнение, для подавления изображений ЦАП используется фильтр нижних частот третьего порядка на 35 МГц.

Важный вывод можно сделать анализируя рисунки 4.57 и 4.59. На рисунке 4.57 представлена группа положительных частот модулированных +  $f_{DAC}/4$ , в то время как на рисунке 4.59 представлена группа отрицательных частот, модулированных -  $f_{DAC}/4$ . Анализируя действительные или мнимые выходы ИС 1273НА044, показанные на рисунках 4.57 и 4.59, можно заметить, что результаты выглядят идентично. Однако анализатор спектра не может показать фазовое соотношение этих сигналов. Различие по фазе между двумя сигналами становится очевидным, когда они приходят (проходят) на (через) квадратурный модулятор AD8345; результаты показаны на рисунках 4.58 и 4.60.

Рисунок 4.49 - Интерполяция  $2 \times$ , комплексная модуляция  $f_{DAC}/4$