# МИКРОСХЕМА ИНТЕГРАЛЬНАЯ 1273НА094

Руководство пользователя

# Содержание

| 1 Введение                                                            | . 3 |

|-----------------------------------------------------------------------|-----|

| 2 Назначение                                                          | . 4 |

| 2.1 Основные характеристики микросхемы                                | . 5 |

| 2.2 Конструктивные характеристики микросхемы                          | . 5 |

| 2.3 Электрические характеристики микросхемы                           | . 8 |

| 3 Структурная схема и описание работы микросхемы                      | 10  |

| 3.1 Порт ввода последовательных данных                                | 11  |

| 3.2 Схема автоматического делителя частоты главного тактового сигнала | 15  |

| 3.3 Описание регистров SPI                                            | 15  |

| 3.4 Регистры громкости правого и левого канала                        | 16  |

| 3.5 Выключение звука                                                  | 17  |

| 3.6 Регистр управления                                                | 18  |

| 3.7 Компенсация предыскажений                                         | 18  |

| 3.8 Сброс                                                             | 19  |

| 3.9 Информация по применению                                          | 20  |

#### 1 Введение

Развитие цифровой техники и цифровых методов обработки сигналов определило современные тенденции в разработке самых разнообразных систем, устройств и приборов. Значительную роль в этих тенденциях занимает аналого-цифровое и цифро-аналоговое преобразование.

Цифро-аналоговый преобразователь (ЦАП) — это устройство для перевода цифровых данных в аналоговый сигнал.

Микросхемы ЦАП нашли широкое применение в усилителях звука, аудиокодеках, системах обработки видео, системах распознавания данных, системах калибровки датчиков, измерительных устройствах, системах управления двигателями, системах распределения данных, цифровых потенциометрах, системах цифровой связи и т. д.

Настоящее техническое описание содержит описание принципа работы и технические характеристики интегральной микросхемы 1273HA094 и другие сведения, необходимые для обеспечения полного использования технических возможностей микросхемы ЦАП.

#### 2 Назначение

Микросхема 1273HA094 является стерео аудио цифро-аналоговым преобразователем содержащим: два канала ЦАП с дифференциальными выходами по напряжению, которые используют многоуровневую сигмадельта ( $\Sigma$ - $\Delta$ ) архитектуру; стерео аттенюатора и блока отключения звука. Управляющий последовательный порт SPI позволяет микроконтроллеру осуществлять регулировку громкости и других параметров.

Микросхема имеет простой, но гибкий входной последовательный интерфейс, обеспечивающий непосредственное подключение к микросхемам АЦП, ПЦОС, преобразователям частоты дискретизации и устройствам, поддерживающие стандарт передачи цифровых данных AES/EBU. Последовательный интерфейс может быть настроен в режим выравнивания данных по правому или левому краям, в режим совместимости с интерфейсами I<sup>2</sup>S и DSP. Микросхема поддерживает работу с 16, 18, 20 и 24-разрядными данными в дополнительном коде, которые передаются со старшего разряда. Для питания микросхемы требуется однополярный источник питания с напряжением 5 В.

Основные области применения микросхемы:

- профессиональные аудио DVD, CD устройства;

- домашние кинотеатры, автомобильные аудио системы;

- музыкальные сэмплеры, цифровые микшеры, цифровые процессоры аудио эффектов.

#### 2.1 Основные характеристики микросхемы

Основные характеристики ИС 1273НА094:

- напряжение питания 5,0 В;

- поддержка 16/18/20/24-разрядных данных;

- поддержка широкого диапазона частот дискретизации, включая 32 кГц, 44,1 кГц, 48 кГц, 88,2 кГц, 96 кГц и 192 кГц;

- многоуровневый сигма-дельта преобразователь;

- дифференциальный выход ЦАП;

- встроенный регулятор уровня громкости звука с отсутствием щелчков;

- аппаратное и программное выключение звука с отсутствием щелчков;

- управление через SPI интерфейс;

- цифровая компенсация предыскажений для частот дискретизации 32 кГц, 44,1 кГц, 48 кГц.

#### 2.2 Конструктивные характеристики микросхемы

Микросхема выполнена в 28-выводном металлокерамическом корпусе 4119.28-1.

Масса микросхемы – не более 3,0 г.

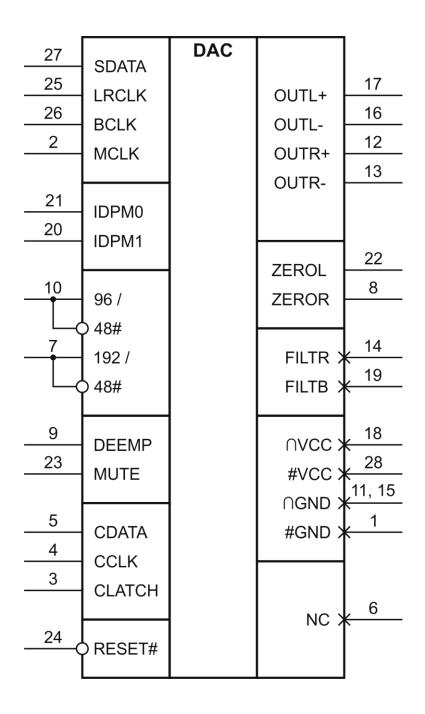

Условное графическое обозначение микросхемы приведено на рисунке 2.1.

Функциональное назначение выводов приведено в таблице 2.1.

Рисунок 2.1 – Условное графическое обозначение микросхемы 1273HA094

Таблица 2.1 – Функциональное назначение выводов микросхемы 1273HA094

| 12/311/10 |             |                                                                              | 1      |

|-----------|-------------|------------------------------------------------------------------------------|--------|

| Номер     | Обозначение | Функциональное назначение                                                    | Тип    |

| вывода    | вывода      |                                                                              | вывода |

| 1         | #GND        | Цифровая земля                                                               | -      |

| 2         | MCLK        | Главный тактовый сигнал                                                      | I      |

| 3         | CLATCH      | Сигнал записи данных в регистры управления по SPI                            | I      |

| 4         | CCLK        | Тактовый сигнал управления по SPI                                            | I      |

| 5         | CDATA       | Сигнал входных данных управления по SPI                                      | I      |

| 6         | NC          | Не используется                                                              | -      |

| 7         | 192/48#     | Аппаратный сигнал выбора частоты дискретизации 192 кГц или 48 кГц            | I      |

| 8         | ZEROR       | Сигнал «флаг нуля правого канала»                                            | О      |

| 9         | DEEMP       | Сигнал включения компенсации предыскажений                                   | I      |

| 10        | 96/48#      | Аппаратный сигнал выбора частоты дискретизации 96 кГц или 48 кГц             | I      |

| 11, 15    | ∩GND        | Аналоговая земля                                                             | -      |

| 12        | OUTR+       | Аналоговый выход положительного полюса правого канала                        | О      |

| 13        | OUTR-       | Аналоговый выход отрицательного полюса правого канала                        | О      |

| 14        | FILTR       | Подключение внешнего фильтрующего конденсатора источника опорного напряжения | -      |

| 16        | OUTL-       | Аналоговый выход отрицательного полюса левого канала                         | О      |

| 17        | OUTL+       | Аналоговый выход положительного полюса левого канала                         | О      |

| 18        | ∩VCC        | Вывод питания аналоговой части                                               | _      |

| 19        | FILTB       | Подключение фильтрующего конденсатора                                        | -      |

| 20        | IDPM1       | Сигнал установки режима работы последовательного интерфейса, порт 1          | I      |

| 21        | IDPM0       | Сигнал установки режима работы последовательного интерфейса, порт 0          | I      |

| 22        | ZEROL       | Сигнал «флаг нуля левого канала»                                             | О      |

| 23        | MUTE        | Сигнал выключения звука                                                      | I      |

| 24        | RESET#      | Сигнал сброса                                                                | I      |

| 25        | LRCLK       | Сигнал стробирования последовательных аудио данных левого/правого канала     | I      |

| 26        | BCLK        | Тактовый битовый сигнал аудио данных                                         | I      |

| 27        | SDATA       | Сигнал последовательных аудио данных,                                        |        |

|           |             | поступающих со старшего разряда                                              | I      |

| 28        | #VCC        | Вывод питания цифровой части                                                 | -      |

|           |             | графе «Тип вывода»: I – вход, О – выход.                                     | I      |

|           |             | 1 1 17 17                                                                    |        |

## 2.3 Электрические характеристики микросхемы

Электрические характеристики микросхем 1273НА094 при приемке и поставке приведены в таблице 2.2.

Значения предельно допустимых электрических режимов эксплуатации в диапазоне рабочих температур приведены в таблице 2.3.

Термины, определения, сокращения и буквенные обозначения параметров – по ОСТ В 11 0998-99, ГОСТ Р 574351-2017 и ГОСТ Р 57441-2017.

Термины, определения и буквенные обозначения параметров, неустановленные действующими стандартами, представлены в приложении A.

Таблица 2.2 – Значения электрических параметров микросхемы 1273НА094

при приемке и поставке

|                                                             | Буквенное   | Нор   |       | Темпера-    |

|-------------------------------------------------------------|-------------|-------|-------|-------------|

| Наименование параметра,                                     | обозначе-   | парам | 1     | тура        |

| единица измерения, режим измерения                          | ние         | не    | не    | среды, °С   |

|                                                             | параметра   | менее | более |             |

| 1                                                           | 2           | 3     | 4     | 5           |

| 1 Выходное напряжение низкого уровня по                     |             |       |       |             |

| выводам ZEROL, ZEROR, B,                                    | $U_{OL}$    | _     | 0,4   |             |

| $U_{CC1} = U_{CC2} = 4,5 \text{ B}, I_{OL} = 1 \text{ MA}$  |             |       |       | _           |

| 2 Выходное напряжение высокого уровня по                    |             |       |       |             |

| выводам ZEROL, ZEROR, B,                                    | $U_{OH}$    | 2,0   | _     |             |

| $U_{CC1} = U_{CC2} = 4,5 \text{ B}, I_{OH} = -1 \text{ MA}$ |             |       |       | _           |

| 3 Входной ток низкого уровня по выводам SDATA,              |             |       |       |             |

| LRCLK, BCLK, MCLK, IDPM0, IDPM1, 96/48#,                    |             |       |       |             |

| 192/48#, DEEMP, MUTE, CDATA, CCLK, CLATCH,                  | $ m I_{IL}$ | -10   | _     |             |

| RESET#, мкA,                                                |             |       |       |             |

| $U_{CC1} = U_{CC2} = 5.5 \text{ B}, U_{IL} = 0 \text{ B}$   |             |       |       |             |

| 4 Входной ток высокого уровня по выводам                    |             |       |       | $-60 \pm 3$ |

| SDATA, LRCLK, BCLK, MCLK, IDPM0, IDPM1,                     |             |       |       | $25 \pm 10$ |

| 96/48#, 192/48#, DEEMP, MUTE, CDATA, CCLK,                  | $ m I_{IH}$ | _     | 10    | $85 \pm 3$  |

| CLATCH, RESET#, мкА,                                        |             |       |       |             |

| $U_{CC1} = U_{CC2} = 5.5 \text{ B}, U_{IH} = U_{CC2}$       |             |       |       |             |

| 5 Динамический ток потребления от источника                 |             |       |       |             |

| $U_{CC1}$ , $MA$ ,                                          | $I_{OCC1}$  | _     | 55    |             |

| $U_{CC1} = 5,5 B, f_{CI\_MCLK} = 24,576 MГц, f_s = 48 кГц$  |             |       |       |             |

| 6 Динамический ток потребления от источника                 |             |       |       |             |

| $U_{CC2}$ , $MA$ ,                                          | $I_{OCC2}$  | _     | 45    |             |

| $U_{CC2} = 5,5 B, f_{CI\_MCLK} = 24,576 MГц, f_s = 48 кГц$  |             |       |       | _           |

| 7 Погрешность усиления характеристики, % от                 |             |       |       |             |

| полной шкалы,                                               | $E_{G}$     | -10   | 10    |             |

| $U_{CC1} = U_{CC2} = 5.0 B$                                 |             |       |       |             |

# Окончание таблицы 2.2

| 1                                                                                       | 2  | 3 | 4 | 5           |

|-----------------------------------------------------------------------------------------|----|---|---|-------------|

| 8 Функциональный контроль,                                                              |    |   |   | $-60 \pm 3$ |

| $U_{CC1} = U_{CC2} = (4,5;5,5) \text{ B, } f_{CI\_MCLK} = 49,152 \text{ M}\Gamma_{II},$ | ΦК | _ | _ | $25 \pm 10$ |

| $f_s = (32; 48; 192) к \Gamma ц$                                                        |    |   |   | $85 \pm 3$  |

Примечание — При измерении динамических токов потребления  $f_{\text{CI\_MCLK}} = f_s \times 512 = 48 \times 512 = 24576$  кГц = 24,576 МГц (в режиме Direct).

Таблица 2.3 – Предельно допустимые и предельные режимы эксплуатации микросхемы 1273HA094

| Наименование параметра режима,                                                                                                                       | Буквенное<br>обозначение | Предельно<br>допустимый<br>режим |                  | Предельный<br>режим |                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------|------------------|---------------------|-----------------|

| единица измерения                                                                                                                                    | параметра                | не<br>менее                      | не<br>более      | не<br>менее         | не более        |

| <ul><li>1 Напряжение питания по выводу<br/>∩VCC, В</li></ul>                                                                                         | U <sub>CC1</sub>         | 4,5                              | 5,5              | -0,3                | 6,0             |

| 2 Напряжение питания по выводу #VCC, В                                                                                                               | $U_{CC2}$                | 4,5                              | 5,5              | -0,3                | 6,0             |

| 3 Входное напряжение низкого уровня по выводам SDATA, LRCLK, BCLK, MCLK, IDPM0, IDPM1, 96/48#, 192/48#, DEEMP, MUTE, CDATA, CCLK, CLATCH, RESET#, B  | $ m U_{IL}$              | 0                                | 0,8              | -0,3                | _               |

| 4 Входное напряжение высокого уровня по выводам SDATA, LRCLK, BCLK, MCLK, IDPM0, IDPM1, 96/48#, 192/48#, DEEMP, MUTE, CDATA, CCLK, CLATCH, RESET#, B | U <sub>IH</sub>          | 2,2                              | U <sub>CC2</sub> |                     | $U_{CC2} + 0.3$ |

| 5 Выходной ток низкого уровня по выводам ZEROL, ZEROR, мА                                                                                            | $I_{OL}$                 |                                  | 1                | _                   | -               |

| 6 Выходной ток высокого уровня по выводам ZEROL, ZEROR, мА                                                                                           | I <sub>OH</sub>          | -1                               | _                | _                   | _               |

| 7 Частота следования импульсов тактовых сигналов MCLK, МГц                                                                                           | $f_{CI\_MCLK}$           | _                                | 49,152           | _                   | _               |

| 8 Частота выборки, кГц                                                                                                                               | fs                       | 32                               | 192              | _                   | _               |

Примечание – Время работы в одном из предельных режимов должно быть не более 5 с.

#### 3 Структурная схема и описание работы микросхемы

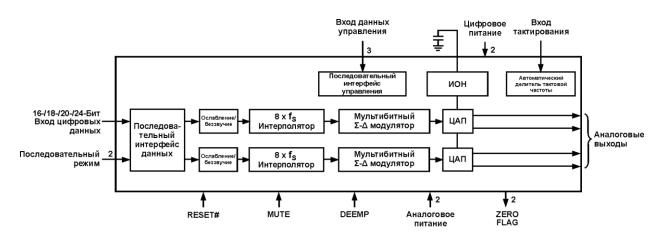

Микросхема 1273НА094 — это однокристальная звуковоспроизводящая стерео система. Она состоит из последовательного порта данных, стерео аттенюатора с возможностью отключения звука, цифровых фильтров, сигмадельта преобразователя и аналоговой дифференциальной выходной схемы. Микросхема также имеет последовательный интерфейс управления SPI. Структурная схема микросхемы приведена на рисунке 3.1.

Рисунок 3.1 – Структурная схема микросхемы 1273НА094

Принятые по последовательному порту данные, поступают на аттенюатор и цифровые фильтры-интерполяторы. После этого ускоренный поток данных поступает на сигма-дельта преобразователь, с выхода которого сигнал поступает на аналоговую дифференциальную схему, осуществляющую восстановление и усиление сигнала.

1273HA094 Последовательный порт аудио данных микросхемы поддерживает работу с частотами дискретизации данных 32 кГц, 44,1 кГц, 48 кГц, 88,2 кГц, 96 кГц и 192 кГц и разрядностью данных 16, 18, 20, 24 бита. данные, Последовательный порт принимает представленные дополнительном коде, начиная со старшего разряда. Данные левого и правого канала принимаются по очереди, начиная с левого. Интерфейс поддерживает работу в четырех режимах приема данных: выравнивание по правому краю, выравнивание по левому краю, совместимость с  ${\rm I}^2{\rm S}$  и DSP. Режим приема данных можно выбрать путем установки битов 5:4 в регистре управления или заданием определенных уровней на выводах IDPM0, IDPM1. Последовательный интерфейс управления SPI служит для установки режима работы микросхемы и уровня громкости каждого канала. Микросхема содержит три регистра: регистр громкости левого канала, регистр громкости

правого канала и регистр управления. При записи данных в регистры по SPI последовательно передается 16 бит данных, начиная со старшего разряда. Два младших бита служат адресом для выбора одного из трех регистров, а старшие 14 бит записываются в соответствующий регистр.

Стерео аттенюатор обеспечивает плавное изменение уровня громкости от предыдущего до нового значения, в том числе при отключении и включении звука. Благодаря этому, во время воспроизведения не возникает звуковых щелчков. Выключение звука можно осуществить путем подачи высокого логического уровня на вывод микросхемы МUTE или путем установки бита 6 в регистре управления. После включения звука уровень громкости плавно вернется к установленным в регистрах громкости значениям.

Сброс 1273HA094 можно осуществить аппаратным способом с помощью внешнего сигнала. При использовании внешнего сигнала сброса все внутренние регистры устанавливаются в начальное состояние.

#### 3.1 Порт ввода последовательных данных

использовании последовательный интерфейс микросхемы 1273НА094 служит для приема данных в дополнительном коде, поступающих со старшего разряда. Данные для левого канала всегда предшествуют данным правого канала. Режим работы последовательного может быть установлен с помощью внешних сигналов интерфейса IDPM0 IDPM1 управления режимом (вывод 21) (вывод 20) (см. таблицу 3.1) или путем установки битов 4 и 5 регистра управления по SPI. Для выбора режима с помощью внешних сигналов требуется, чтобы биты выбора режима регистра управления были установлены в 0 (значение по умолчанию, устанавливается в момент включения питания). Для установки режима работы последовательного интерфейса по SPI требуется, чтобы внешние сигналы управления были подключены к земле.

При изменении режима работы последовательного интерфейса рекомендуется выключать звук (см. п. 3.5).

Таблица 3.1 – Режимы работы порта ввода последовательных данных

| IDPM1 (вывод 20) | IDPM0 (вывод 21) | Режим работы последовательного       |

|------------------|------------------|--------------------------------------|

|                  |                  | порта данных                         |

| 0                | 0                | Режим выравнивания по правому        |

|                  |                  | краю                                 |

| 0                | 1                | Режим совместимости I <sup>2</sup> S |

| 1                | 0                | Режим выравнивания по левому         |

|                  |                  | краю                                 |

| 1                | 1                | Режим совместимости с DSP            |

Во всех режимах передачи, кроме режима выравнивания по правому краю, последовательный порт позволяет работать с любым количеством бит до 24. Лишние биты не приводят к ошибке, и отбрасываются. В режиме выравнивания по правому краю используют биты 8 и 9 регистра управления для выбора разрядности кодового слова 16, 20 или 24 бита. Разрядность по умолчанию, устанавливающаяся при включении питания — 24 бита. Когда интерфейс управления SPI не используется, выводы CLATCH (вывод 3), СССК (вывод 4), CDATA (вывод 5) подтянуты к низкому логическому уровню.

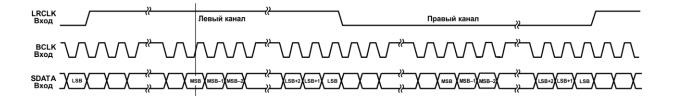

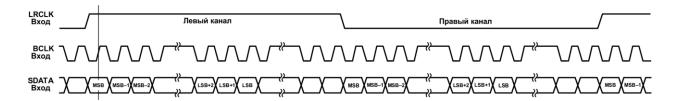

Рисунок 3.2 — Временная диаграмма сигналов последовательного интерфейса данных в режиме выравнивания по правому краю

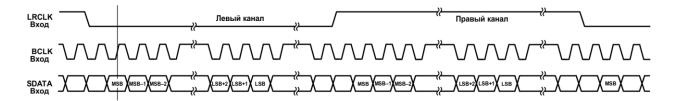

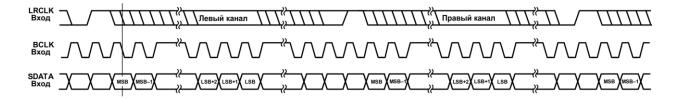

Рисунок 3.3 — Временная диаграмма сигналов последовательного интерфейса данных в режиме совместимости  ${\bf I}^2{\bf S}$

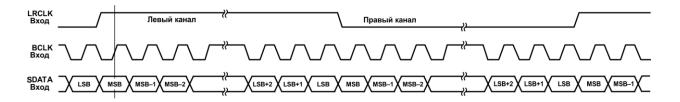

Рисунок 3.4 — Временная диаграмма сигналов последовательного интерфейса данных в режиме выравнивания по левому краю

Рисунок 3.5 — Временная диаграмма сигналов последовательного интерфейса данных в режиме совместимости с DSP

Рисунок 3.6 – Временная диаграмма сигналов последовательного интерфейса в уплотненном режиме

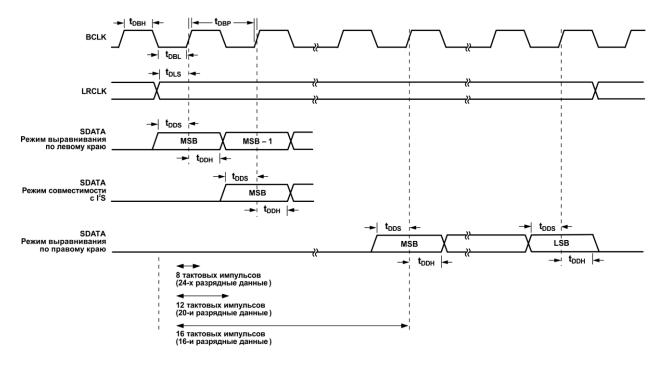

Рисунок 3.7 — Временные характеристики последовательного интерфейса данных

На рисунке 3.2 представлен режим выравнивания данных по правому краю (16 бит). Сигнал LRCLK имеет высокий логический уровень для приема данных левого канала и низкий логический уровень — для правого канала. Данные записываются по переднему фронту сигнала BCLK.

При нормальной работе для приема одного кадра данных требуется 64 такта (32 такта для половины кадра). Когда установлена разрядность кодового слова 24 бита (биты 8 и 9 регистра управления по SPI установлены в 0:0), последовательный порт принимает данные, начиная с восьмого такта после переключения сигнала LRCLK. Когда установлена разрядность кодового слова 20 бит, данные принимаются, начиная с 12 такта. В 16-разрядном режиме данные принимаются с 16 такта. Эти задержки не зависят от числа тактов кадра данных, таким образом, возможен прием данных в любом вышеупомянутом формате. Соответствующие временные диаграммы представлены на рисунке 3.7.

На рисунке 3.3 представлен режим  $I^2S$ . Сигнал LRCLK имеет низкий логический уровень для передачи данных левого канала и высокий логический уровень — для правого канала. Данные записываются по переднему фронту сигнала BCLK. Задержка перед записью старшего разряда данных, выравненных по левому краю, составляет один такт BCLK после переключения сигнала LRCLK. Режим  $I^2S$  позволяет принимать данные с разрядностью до 24 бит.

На рисунке 3.4 показан режим выравнивания данных по левому краю. Сигнал LRCLK имеет высокий логический уровень для передачи данных левого канала и низкий логический уровень — для правого канала. Данные записываются по переднему фронту сигнала BCLK. Запись старшего разряда данных, выравненных по левому краю, происходит без задержки после переключения сигнала LRCLK. Режим выравнивания по левому краю позволяет принимать данные с разрядностью до 24 бит; число тактов BCLK для передачи кадра данных может составлять от удвоенного значения разрядности слова данных до 64 тактов.

На рисунке 3.5 показан режим последовательного интерфейса, совместимый с DSP. На вход LRCLK необходимо подать импульс высокого логического уровня с длительностью не менее одного периода тактового сигнала перед записью данных левого канала со старшего разряда. Перед записью старшего разряда данных правого канала необходимо снова подать на LRCLK импульс высокого логического уровня с длительностью не менее одного периода тактового сигнала. Данные записываются по заднему фронту сигнала BCLK. Режим последовательного интерфейса DSP позволяет принимать данные с разрядностью до 24 бит.

В данном режиме ПЦОС отвечает за то, чтобы данные левого канала были переданы при первом импульсе LRCLK; далее синхронизация поддерживается с этого момента.

Микросхема 1273НА094 поддерживает уплотненный режим с тактовой частотой сигнала BCLK 32 × fs. В таком режиме C3P выровнен относительно переключения LRCLK, а M3P выровнен относительно противоположного переключения LRCLK. Сигнал LRCLK имеет высокий логический уровень для передачи данных левого канала и низкий логический уровень — для правого канала. Данные записываются по переднему фронту сигнала BCLK. Уплотненный режим может быть использован, когда запрограммирован режим с выравниванием по левому краю или с выравниванием по правому краю. Уплотненный режим представлен на рисунке 3.6.

# 3.2 Схема автоматического делителя частоты главного тактового сигнала

Микросхема 1273НА094 имеет схему, которая автоматически определяет отношение между частотой главного тактового сигнала и частотой поступающих последовательно данных и устанавливает нужный коэффициент деления частоты для работы интерполирующего фильтра и модулятора. Возможные частоты для каждого режима представлены в таблице 3.2. Главный тактовый сигнал должен быть синхронизирован с сигналом LRCLK; но отношение фазы главного тактового сигнала и LRCLK не критично.

Таблица 3.2 - Возможные частоты главного тактового сигнала и внутренние тактовые частоты сигма-дельта модулятора

| Режим  | Возможные частоты главного тактового                                                                                        | Номинальная   | Внутренняя      |

|--------|-----------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|

|        | сигнала                                                                                                                     | частота       | тактовая        |

|        |                                                                                                                             | дискретизации | частота         |

|        |                                                                                                                             | входного      | сигма-дельта    |

|        |                                                                                                                             | сигнала, кГц  | модулятора      |

| INT 8x | $256 \times \text{fs}$ , $384 \times \text{fs}$ , $512 \times \text{fs}$ , $768 \times \text{fs}$ , $1024 \times \text{fs}$ | 48            | $128 \times fs$ |

| INT 4x | $128 \times \text{fs}$ , $192 \times \text{fs}$ , $256 \times \text{fs}$ , $384 \times \text{fs}$ , $512 \times \text{fs}$  | 96            | $64 \times fs$  |

| INT 2x | $64 \times \text{fs}$ , $96 \times \text{fs}$ , $128 \times \text{fs}$ , $192 \times \text{fs}$ , $256 \times \text{fs}$    | 192           | $32 \times fs$  |

# 3.3 Описание регистров **SPI**

Интерфейс SPI служит для гибкого управления многими параметрами микросхемы. Управление осуществляется с помощью трех регистров: регистра громкости левого канала, регистра громкости правого канала и

регистра управления. За каждый цикл записи данных в регистры по SPI последовательно передается 16 бит, начиная со старшего разряда. Два младших бита (таблица 3.3) служат для выбора одного из трех регистров, а 14 старших записываются в соответствующий регистр.

| Таблица 3.3 - Регистры ИС 1 | 2/3HA094 |

|-----------------------------|----------|

|-----------------------------|----------|

| Бит 1 | Бит 0 | Регистр                  |

|-------|-------|--------------------------|

| 0     | 0     | Громкость левого канала  |

| 1     | 0     | Громкость правого канала |

| 0     | 1     | Регистр управления       |

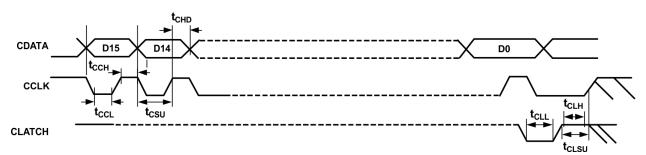

Тактовый сигнал ССLК интерфейса SPI служит для захвата данных. Поступающие данные переключаются по заднему фронту сигнала ССLК. После 16 периодов сигнала ССLК сигнал СLATCH должен переключиться в высокий логический уровень, чтобы загрузить полученные данные в 1273HA094.

Временная диаграмма сигналов последовательного интерфейса управления показана на рисунке 3.8, а временные характеристики SPI представлены в таблице 3.4.

Рисунок 3.3 — Временная диаграмма сигналов последовательного интерфейса управления

Таблица 3.4 – Временные характеристики SPI

| Параметр           | Описание параметра                                         | Значение            |

|--------------------|------------------------------------------------------------|---------------------|

| $t_{CCH}$          | Длительность импульса CCLK при высоком логическом уровне   | 40 нс               |

| $t_{CCL}$          | Длительность импульса CCLK при низком логическом уровне    | 40 нс               |

| $t_{CSU}$          | Время установки сигнала CDATA                              | 10 нс               |

| $t_{CHD}$          | Время удержания сигнала CDATA                              | 10 нс               |

| $t_{\mathrm{CLL}}$ | Длительность импульса CLATCH при низком логическом уровне  | 10 нс               |

| $t_{CLH}$          | Длительность импульса CLATCH при высоком логическом уровне | 10 нс               |

| $t_{CLSU}$         | Время установки сигнала CLATCH                             | $4 \times t_{MCLK}$ |

# 3.4 Регистры громкости правого и левого канала

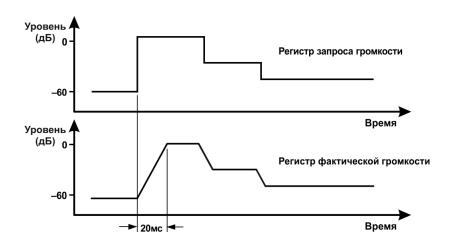

При записи данных в правый и левый регистры громкости происходит автоматическая плавная установка уровня громкости без щелчков. Значение старших 10 бит регистров громкости увеличивается на 1 с частотой

дискретизации. Младшие 4 бита не загружаются в схему плавной установки уровня громкости и оказывают действие мгновенно. Плавная установка в худшем случае потребует около 20 мс при постепенном изменении громкости более чем на 60 дБ. На рисунке 3.9 показан график изменения уровня громкости во времени.

14-разрядное значение уровня громкости умножается на отсчеты сигнала, таким образом, характер изменения громкости линейный. Значение уровня громкости имеет формат без знака (то есть максимальному уровню громкости соответствует двоичное значение 11 1111 1111 1111).

Рисунок 3.9 – Плавная регулировка громкости

# 3.5 Выключение звука

В ИС 1273НА094 предусмотрено два способа выключения звука на аналоговых выходах. Первый способ – путем установки высокого логического уровня сигнала МUТЕ (вывод 23), при этом звук на левом и правом канале будет выключен. Второй способ – путем установки mute-бита в регистре управления (бит 6) в высокий логический уровень. Когда включается звук, уровень громкости плавно возвращается к значению, установленному в регистре громкости.

#### 3.6 Регистр управления

В таблице 3.5 представлены функции регистра управления.

Таблица 3.5 – Функции регистра управления

| Номер<br>бита | Функция                                                                                                                                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11            | Режим INT 2x, выполняется функция лог. ИЛИ с 7 выводом (192/48#); по умолчанию = $0$                                                                                                                                                          |

| 10            | Режим INT 4х, выполняется функция лог. ИЛИ с 10 выводом (96/48#); по умолчанию = $0$                                                                                                                                                          |

| 9:8           | Разрядность слова данных в режиме выравнивания по правому краю $0:0 = 24$ бит $0:1 = 20$ бит $1:0 = 16$ бит По умолчанию $0:0$                                                                                                                |

| 7             | Сброс; по умолчанию = 0                                                                                                                                                                                                                       |

| 6             | Программное выключение звука, выполняется функция лог. ИЛИ с 23 выводом                                                                                                                                                                       |

| 5:4           | Режим работы последовательного интерфейса, выполняется функция лог. ИЛИ с внешними сигналами IDPM1:IDPM0 соответственно $0:0=$ выравнивание по правому краю $0:1=I^2S$ $1:0=$ выравнивание по левому краю $1:1=$ режим DSP По умолчанию $0:0$ |

| 3:2           | Выбор фильтра компенсации предыскажений  0:0 = фильтр выключен  0:1 = фильтр для 44,1 кГц  1:0 = фильтр для 32 кГц  1:1 = фильтр для 48 кГц По умолчанию 0:0                                                                                  |

## 3.7 Компенсация предыскажений

ИС 1273НА094 имеет встроенный фильтр-компенсатор предыскажений, который может использоваться при воспроизведении СD. Возможна компенсация предыскажений с помощью трех частотных характеристик, которые соответствуют частотам дискретизации 32 кГц, 44,1 кГц, 48 кГц. Внешний сигнал DEEMP (9 вывод) включает фильтр-компенсатор для частоты дискретизации 44,1 кГц. Другие фильтры могут быть выбраны путем записи 2 и 3 бита регистра управления. Если для выбора фильтра будет использоваться SPI, то вывод DEEMP должен быть подтянут к низкому логическому уровню.

#### 3.8 Сброс

Сброс ИС 1273НА094 можно осуществить аппаратным способом с помощью внешнего сигнала (RESET#, вывод 24). Когда сигнал сброса становится активным, нормальная работа ИС 1273НА094 приостанавливается, на выходах устанавливается значение, соответствующее середине шкалы. Сброс 1273НА094 необходимо выполнять всегда при включении питания. Сигнал RESET# должен иметь активный уровень в течение 64 периодов главного тактового сигнала. При переключении RESET# в неактивное состояние, нормальное функционирование продолжается после задержки времени, равной групповой задержке, плюс три периода сигнала МСLК.

При использовании внешнего сигнала сброса все внутренние регистры и регистры управления по SPI устанавливаются в начальное состояние, когда сигнал RESET# имеет низкий логический уровень. Когда RESET# переключается в высокий логический уровень, устанавливается нормальный режим работы с настройками по умолчанию.

#### 3.9 Информация по применению

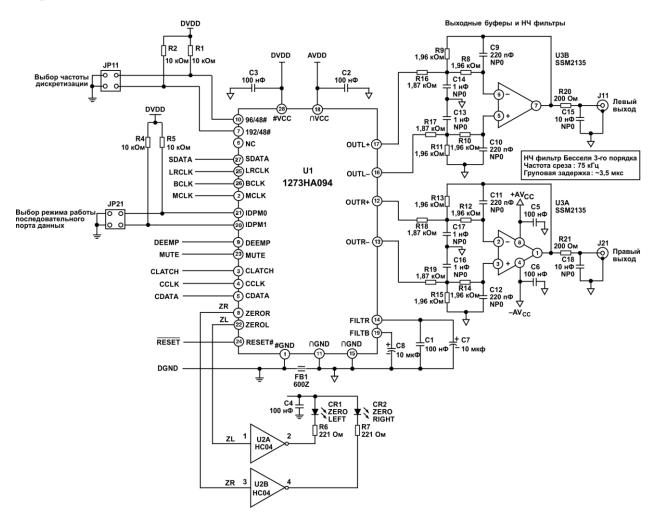

Схема применения микросхемы 1273НА094 в стерео режиме показана на рисунке 3.10.

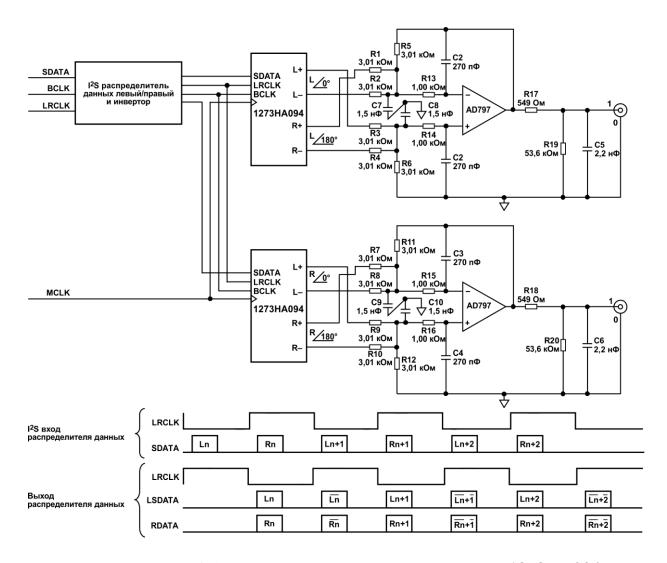

Схема применения микросхемы 1273НА094 в моно режиме приведена на рисунке 3.11.

Рисунок 3.10 – Схема применения микросхемы 1273HA094 в стерео режиме

Рисунок 3.11 – Схема применения микросхемы 1273HA094 в моно режиме