# МИКРОСХЕМА ИНТЕГРАЛЬНАЯ К1921ВГ015

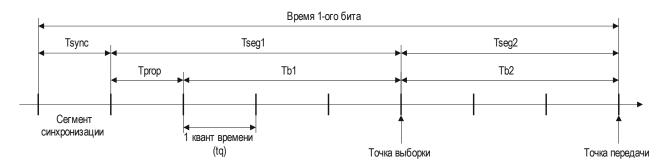

Руководство пользователя

от 05.09.2025

**К1921ВГ015** — ультра низко-потребляющий микроконтроллер RISC-V архитектуры с 1Мб Flash памяти, 256 Кб (+64Кб) ОЗУ, ADC, CMP, CRYPTO, TRNG, SPI, QSPI, UART, I2C, CAN, AntiTAMPER, WakeUp.

#### Особенности

- Ультра низкое потребление:

- напряжение питания:

1,62 B 3,60B;

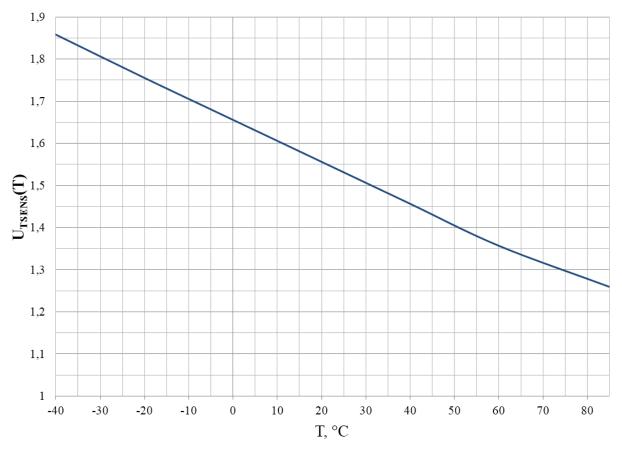

- температурный диапазон:

(-40 85) °C;

- до 8 мкА в режиме POWERDOWN (GPR, RTC, внутренний RCосциллятор, 3 WAKEUP);

- до 190 мкА в режиме STOP (GPR, RTC, внутренний RC-осциллятор, 3 WAKEUP, SRAM1, CMP);

- до 500 мкА / МГц в режиме RUN;

- до 40 мкс время выхода из режима IDLE;

- до 1800 мкс время выхода из режимов STOP и POWEROFF.

#### • Сброс:

- ультранизкопотребляющий POR;

- Ядро: RISC-V 32bit CPU

- система команд: RV32IMFCN\_ZBA\_ZBB\_ZBC\_ZBS;

- от 32 КГц до 50 МГц;

- 1.35 DMIPS/MHz (Dhrystone 2.1)

#### • Тактовые сигналы:

- внутренний осциллятор HSE для подключения внешнего резонатора от 2 МГц до 30 МГц;

- внутренний RC генератор HSI:

1МГц;

- внутренний RC генератор LSI (RTC): 32 КГц;

- внутренний осциллятор LSE для подключения внешнего резонатора 32768 Гц;

- системная PLL: до 50 МГц.

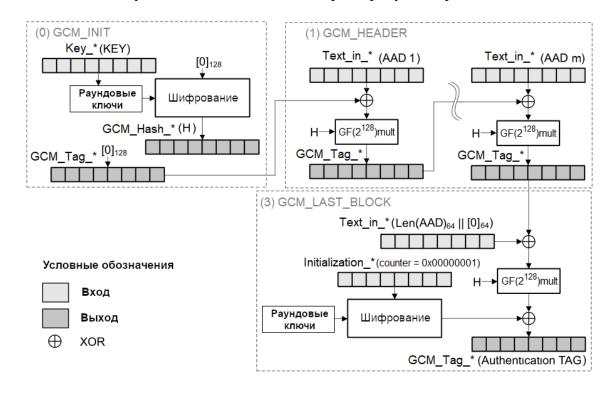

- CRYPTO: AES-128; AES-256, Кузнечик, Магма.

- HASH: SHA-1, SHA-224, SHA-256, MD5.

- 2 CRC, 128 бит уникальный ID.

- До 48 выводов I/O.

- Память:

- 2 Кб Кэш инструкций;

- 1 Мб Flash памяти;

- 256 Кб памяти ОЗУ0;

- 64 Кб памяти ОЗУ1 в батарейном домене;

- 64 байта регистров GPR.

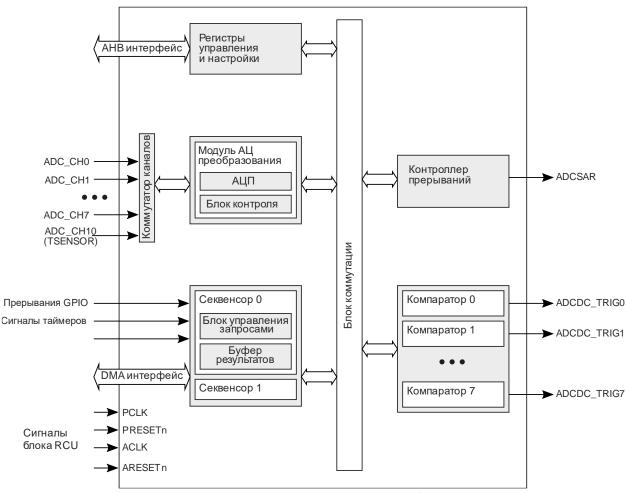

- Аналоговая периферия:

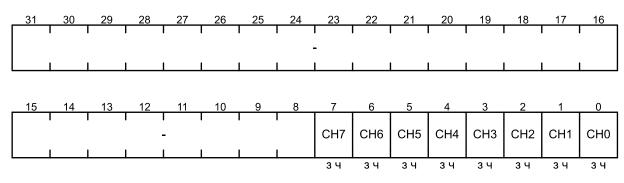

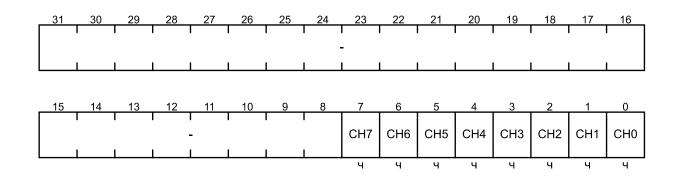

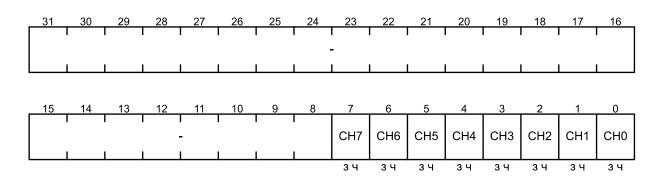

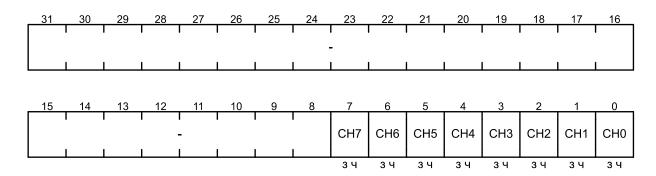

- 8-канальный 12-разрядный быстродействующий АЦП с режимами цифрового компаратора;

- 8-канальный 16-разрядный сигмадельта АЦП;

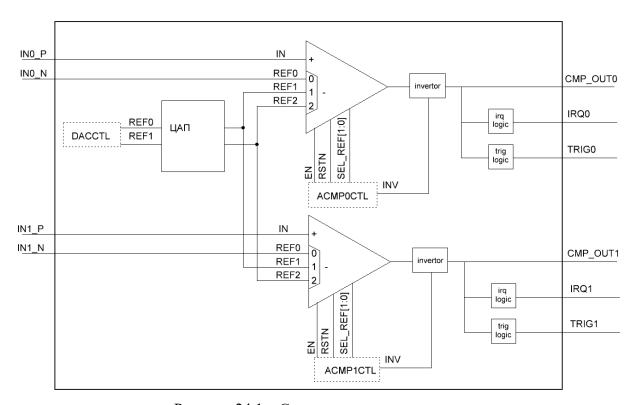

- два аналоговых компаратора.

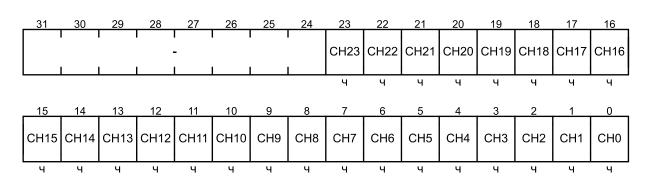

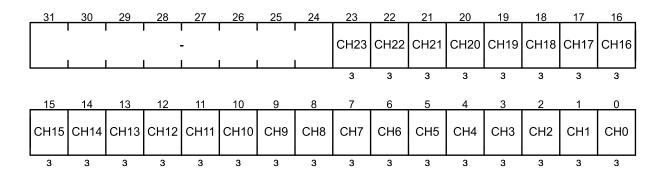

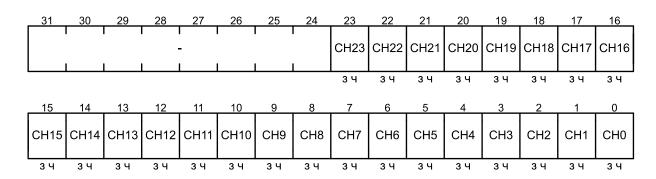

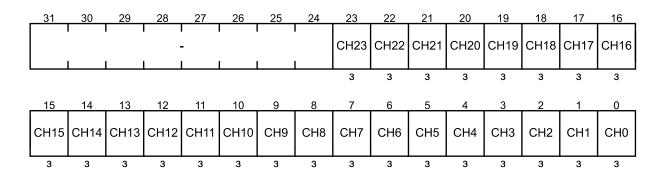

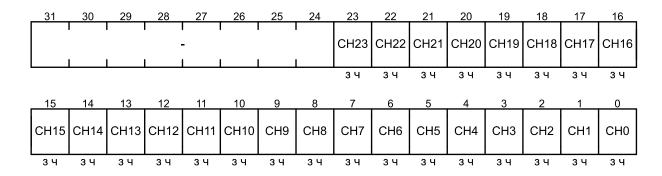

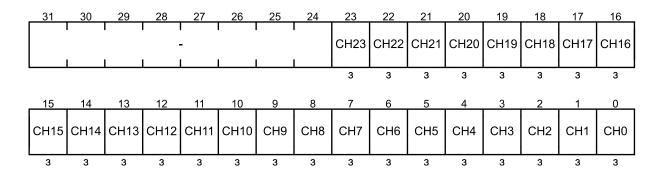

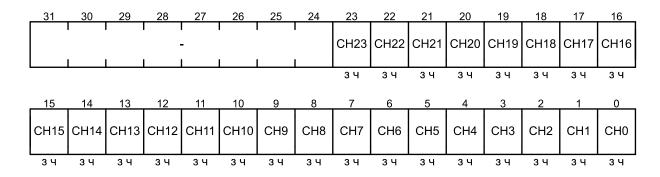

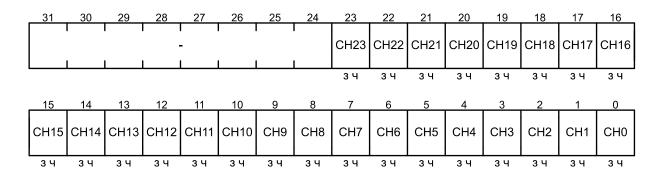

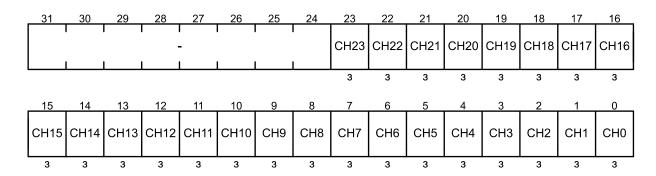

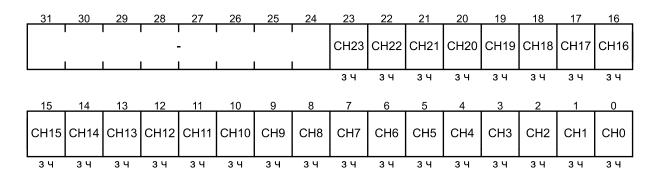

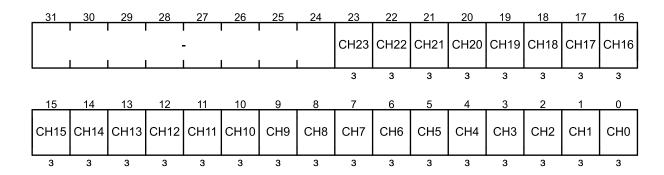

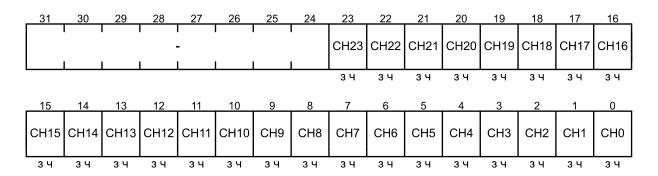

- Контроллер DMA: 24 канала.

- Контроллеры интерфейсов:

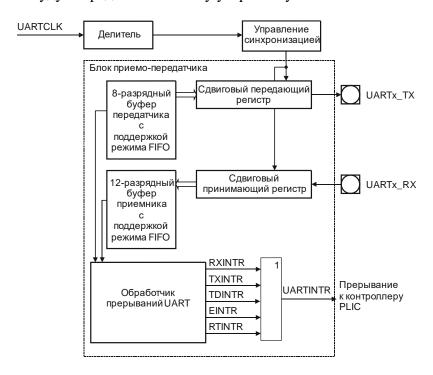

- пять приемопередатчиков UART;

- CAN 2.0b;

- USB 2.0 FullSpeed (Device);

- один контроллер I2C;

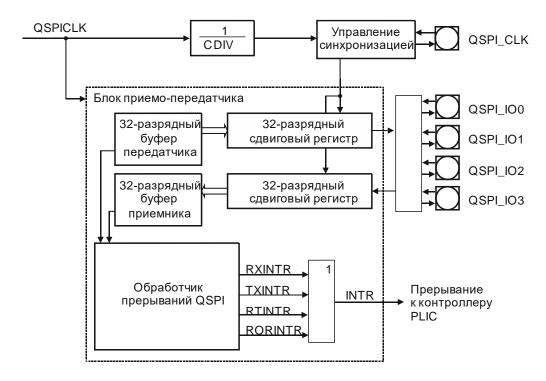

- один контроллер QSPI;

- два контроллера SPI.

- 6 таймеров: один 32-разрядный, три 16-разрядных, два сторожевых таймера (один независимый сторожевой таймер).

- Интерфейс отладки: JTAG.

- Корпус: LQFP100

## Содержание

| Введение                                             |    |

|------------------------------------------------------|----|

| 1 Область применения и особенности микроконтроллера  | 7  |

| 2 Краткое техническое описание микроконтроллера      |    |

| 2.1 Функциональные параметры                         | 8  |

| 2.2 Электрические параметры                          |    |

| 3 Архитектура изделия                                |    |

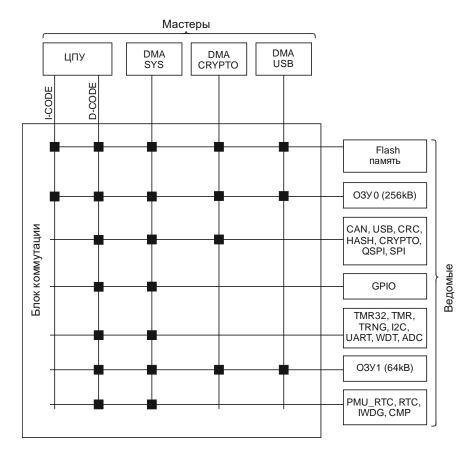

| 3.1 Блок коммутации микроконтроллера                 | 22 |

| 4 Блок управления сбросом и синхронизацией RCU       |    |

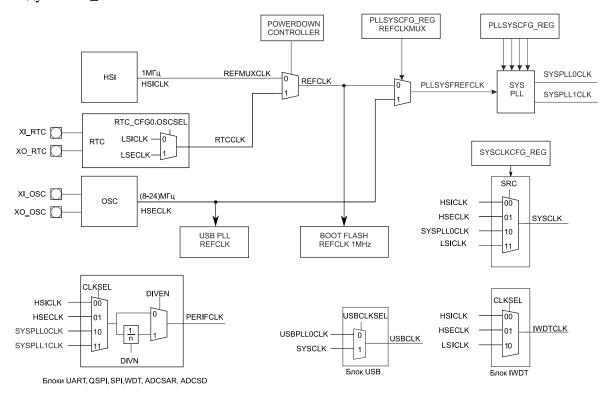

| 4.1 Общая система тактирования                       |    |

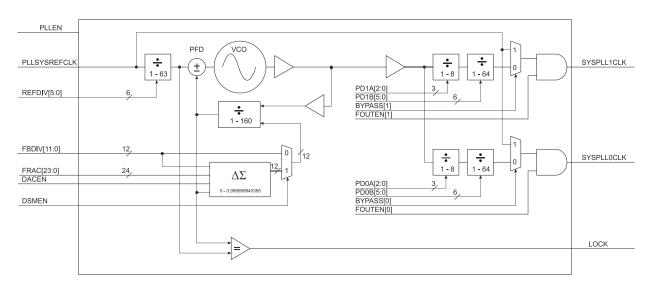

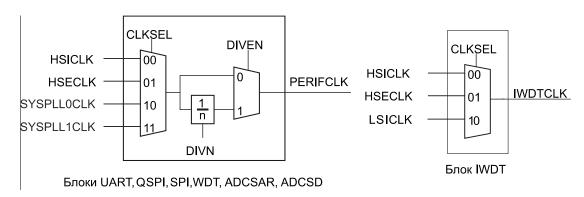

| 4.2 Синтезатор частоты PLL                           |    |

| 4.3 RC генератор HSI                                 |    |

| 4.4 Система слежения за тактовыми сигналами          |    |

| 4.5 Сигналы сброса                                   |    |

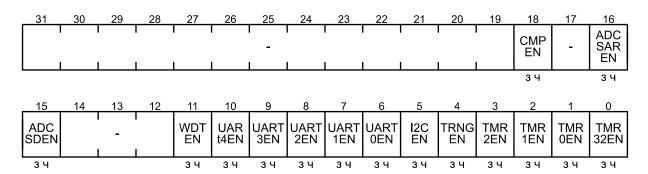

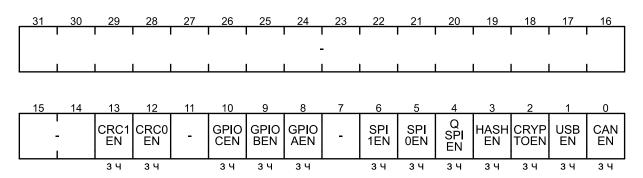

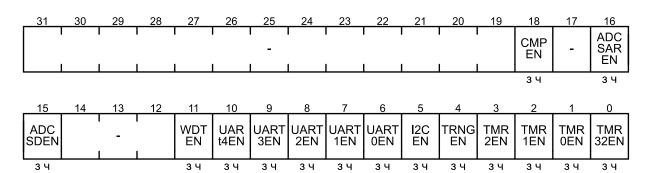

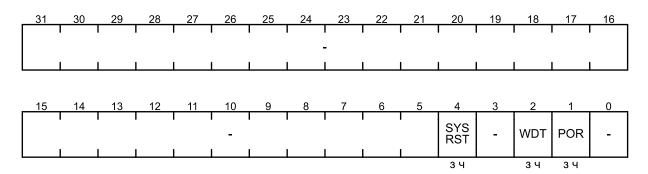

| 4.6 Тактирование и сброс периферийных блоков         | 27 |

| 5 Блок управления энергопотреблением РМU             |    |

| 5.1 Расширенный контроллер питания АРС               |    |

| 5.2 Управление энергопотреблением батарейного домена |    |

| 5.3 Настройка регистров для режимов работы с WFI     |    |

| 6 Организация памяти                                 |    |

| 7 Контроллер Flash-памяти                            |    |

| 7.1 Flash-память                                     |    |

| 7.2 Сервисный сброс всей Flash-памяти                |    |

| 8 Микропроцессорное ядро CloudBEAR                   |    |

| 8.1 Система команд                                   |    |

| 9 Контроллер прерываний                              |    |

| 9.1 Локальный контроллер прерываний (CLINT)          |    |

| 9.2 Контроллер обработки внешних прерываний (PLIC)   |    |

| 9.3 Обзор функционирования                           |    |

| 9.4 Конфигурация прерываний                          |    |

| 9.5 Программная модель обработки внешних прерываний  |    |

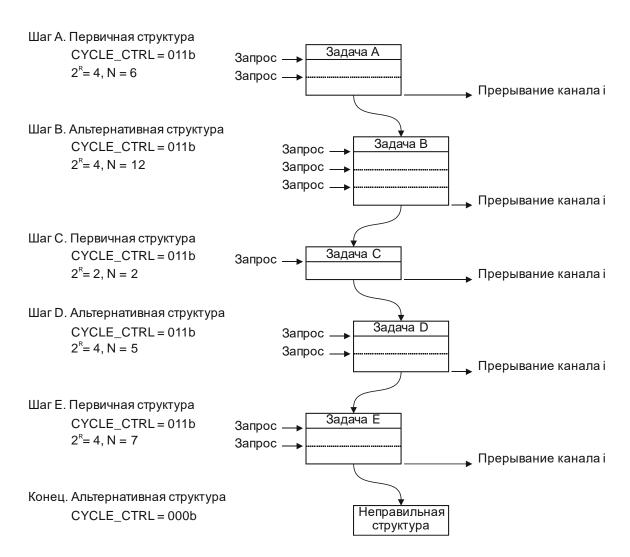

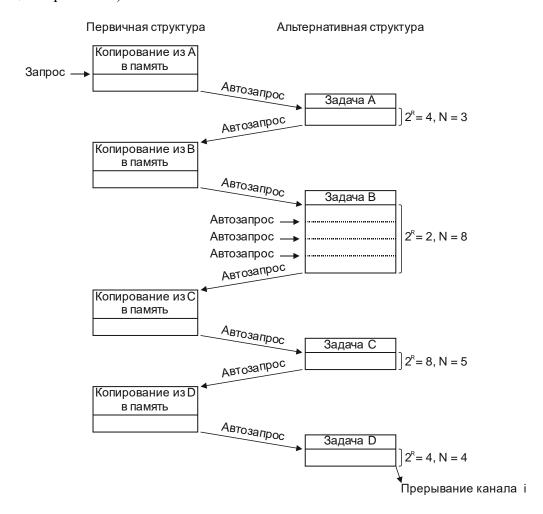

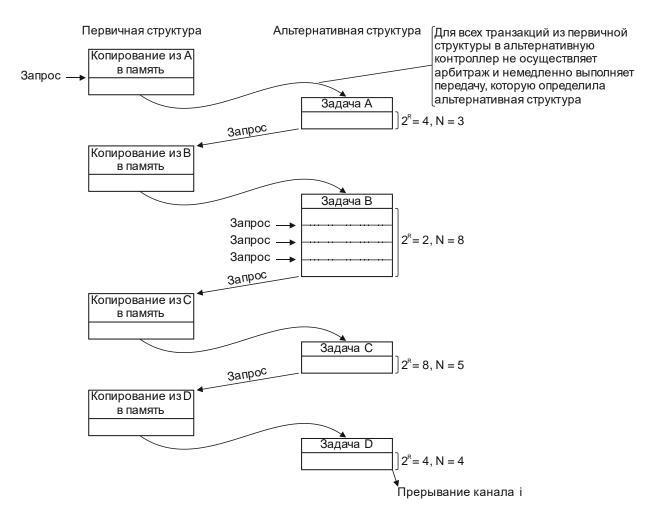

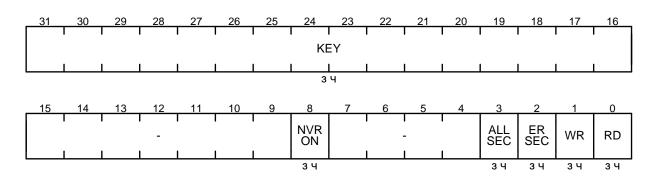

| 10 Контроллер прямого доступа к памяти DMA           |    |

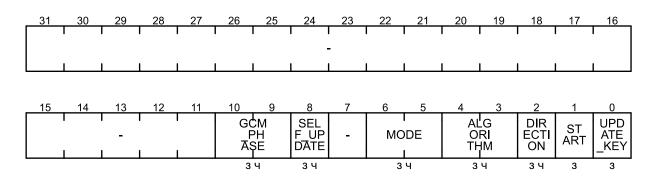

| 10.1 Программное управление контроллером DMA         |    |

| 10.2 Правила обмена данными                          |    |

| 10.3 Правила арбитража                               |    |

| 10.4 Типы циклов                                     |    |

| 10.5 Циклический режим                               |    |

| 10.6 Индикация ошибок                                |    |

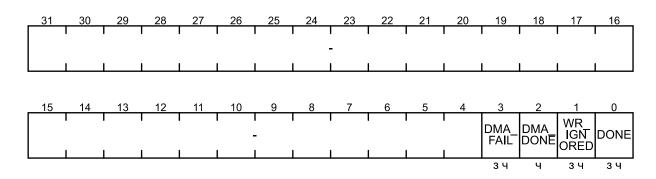

| 10.7 Прерывания                                      |    |

| 11 Порты ввода-вывода                                |    |

| 11.1 Функционирование порта                          |    |

| 11.2 Режим альтернативных функций                    |    |

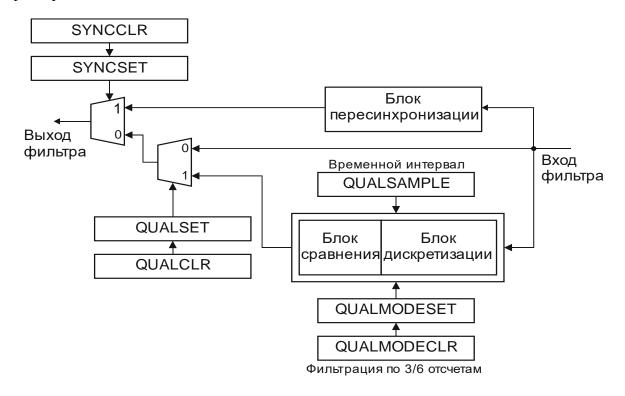

| 11.3 Входные фильтры                                 |    |

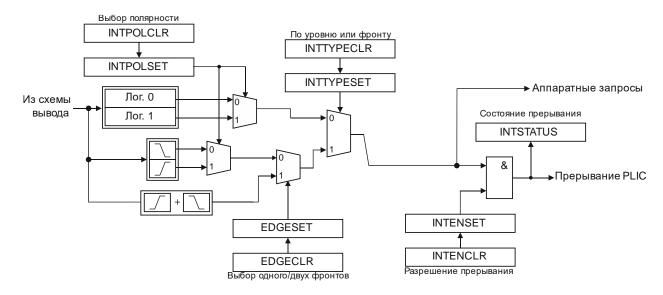

| 11.4 Прерывания                                      |    |

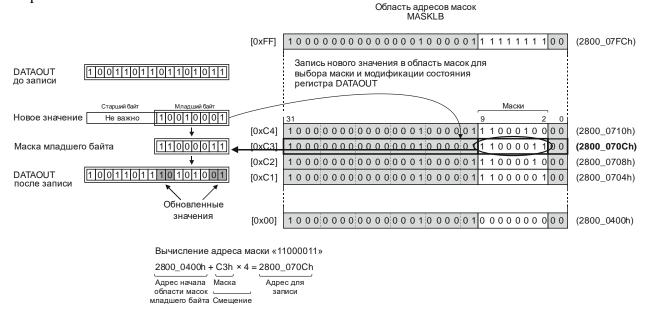

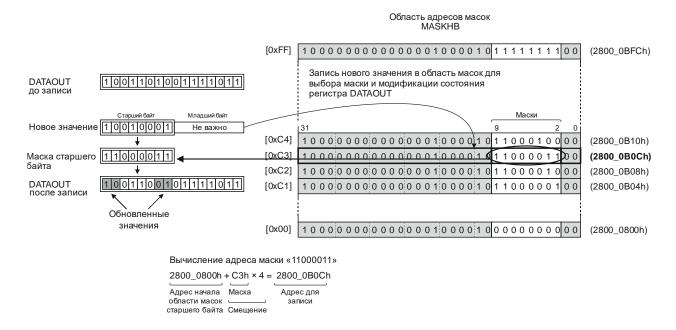

| 11.5 Генерация аппаратных запросов                   |    |

| 11.6 Механизм блокировки конфигурации                |    |

| 11.0 Механизм олокировки конфигурации                |    |

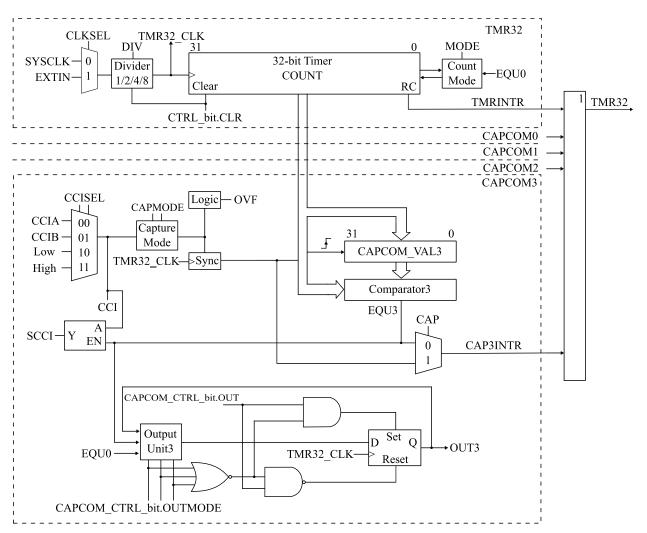

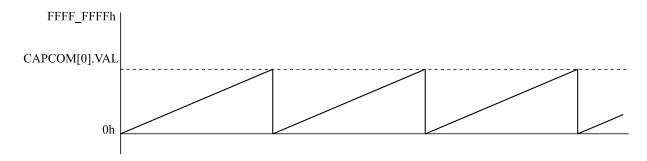

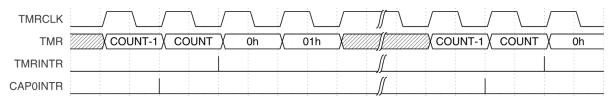

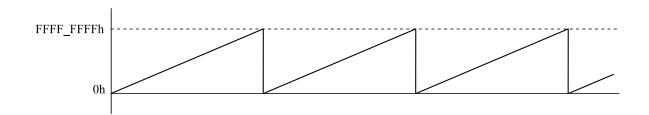

| 12 Таймер TMR32                                      |    |

| 12.1 Функционирование таймера                        |    |

| 12.1 Функционирование таимера                        |    |

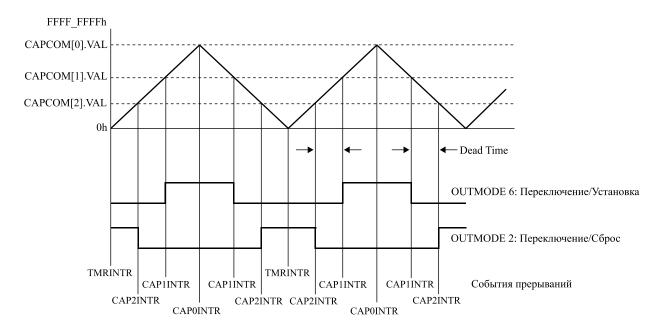

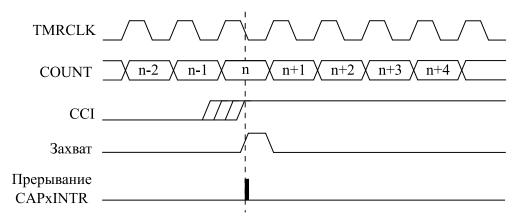

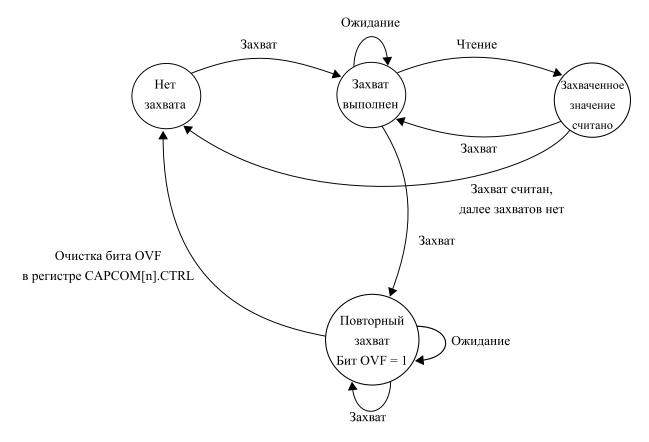

| 12.3 Блоки захвата/сравнения                         |    |

| 12.5 Ditokii 500Duta opaniotiin                      |    |

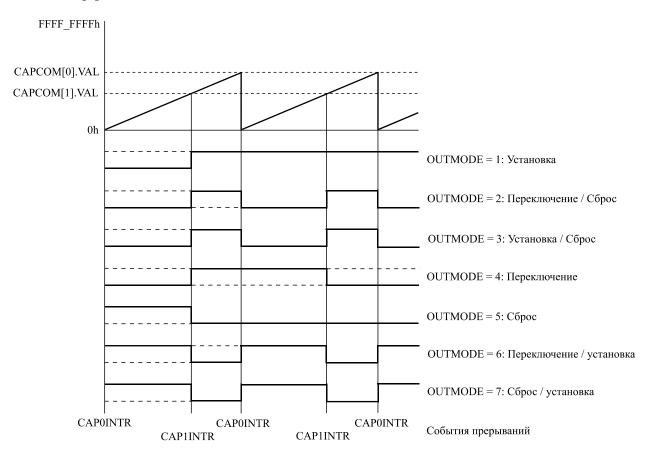

|     | 12.4 Выходной модуль                                         | 87  |

|-----|--------------------------------------------------------------|-----|

|     | 12.5 Прерывания таймера                                      | 90  |

|     | 12.6 Взаимодействие с DMA                                    | 91  |

|     | 12.7 Взаимодействие с АЦП                                    | 91  |

| 13  | Таймеры ТМR                                                  | 92  |

|     | 13.1 Функционирование таймера                                | 93  |

|     | 13.2 Режимы счёта                                            |     |

|     | 13.3 Блоки захвата/сравнения                                 | 97  |

|     | 13.4 Выходной модуль                                         |     |

|     | 13.5 Прерывания таймера                                      |     |

|     | 13.6 Взаимодействие с DMA                                    |     |

|     | 13.7 Взаимодействие с АЦП                                    |     |

| 14  | Блок подсчёта циклического избыточного кода (CRC)            |     |

|     | 14.1 Особенности блока CRC                                   |     |

|     | 14.2 Функции блока CRC                                       |     |

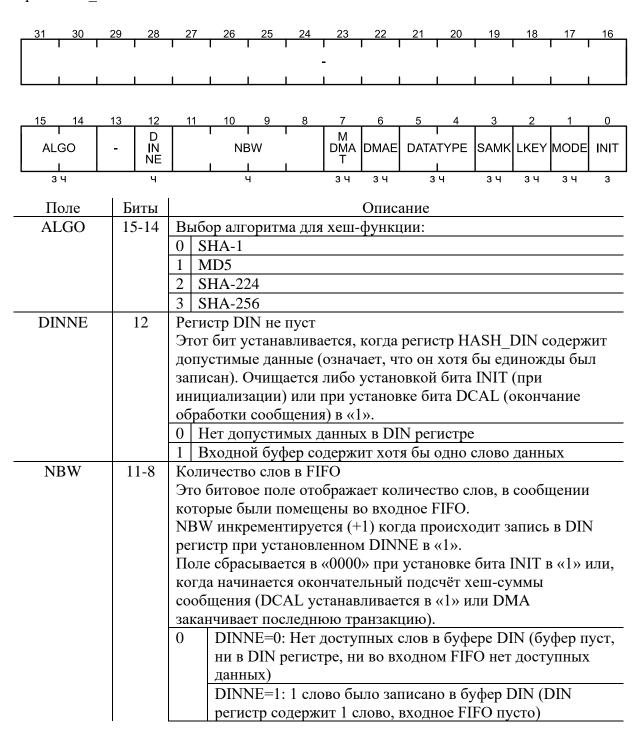

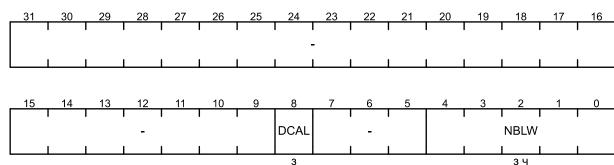

| 15  | Хеш-процессор (НАЅН)                                         |     |

|     | 15.1 Функционирование хеш-процессора                         |     |

|     | 15.2 Основные особенности.                                   |     |

|     | 15.3 Описание хеш процессора                                 |     |

|     | 15.4 Длительность обработки                                  |     |

|     | 15.5 Типы данных                                             |     |

|     | 15.6 Вычисление хеш-суммы сообщения                          |     |

|     | 15.7 Автоматическое заполнение сообщения                     |     |

|     | 15.8 Вычисление хеш-функции                                  |     |

|     | 15.9 Вычисление НМАС                                         |     |

|     | 15.10 Переключение контекста                                 |     |

|     | 15.11 Прерывания                                             |     |

| 16  | Блок криптографии                                            |     |

| 10  | 16.1 Общие положения                                         |     |

|     | •                                                            |     |

|     | 16.2 Структура блока криптографии                            |     |

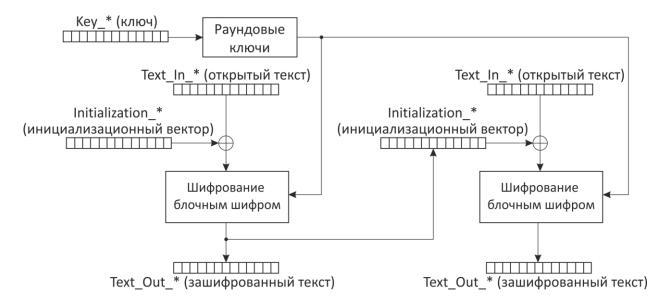

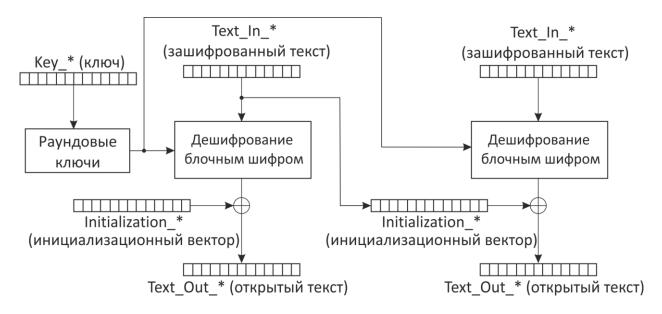

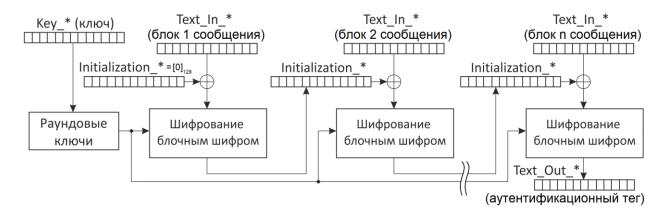

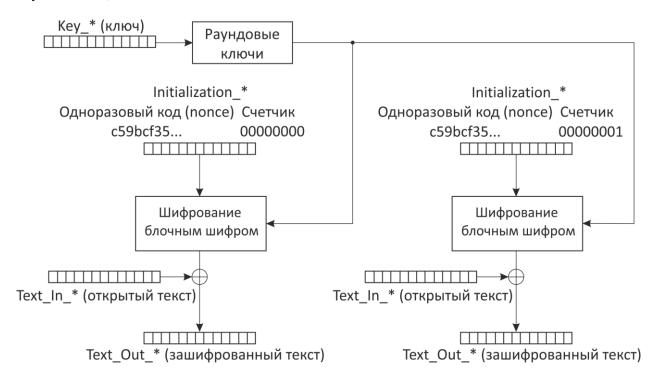

|     | 16.3 Режимы выполнения криптографических операций            |     |

|     | 16.4 Режимы работы                                           |     |

|     | 16.5 Экстренное прекращение выполнения операции              |     |

|     | 16.6 Производительность                                      |     |

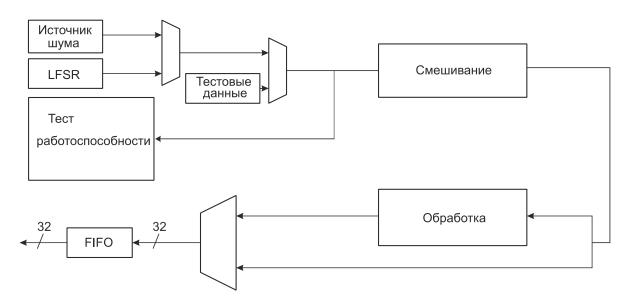

| I / | Блок генератора случайных чисел                              |     |

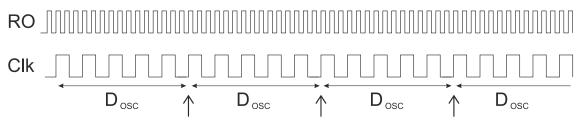

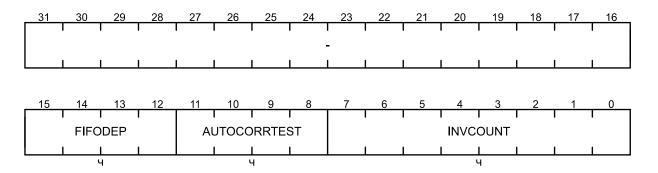

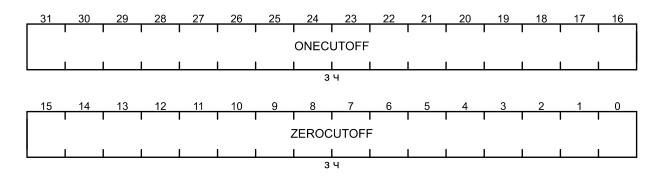

|     | 17.1 Источник энтропии                                       |     |

|     | 17.2 Процесс дискретизации                                   |     |

|     | 17.3 Непрерывное тестирование                                |     |

|     | 17.4 Тест на количество повторений                           |     |

|     | 17.5 Тест на подсчет пропорций (окно 512-недвоичных выборок) |     |

|     | 17.6 Тест корреляции                                         |     |

|     | 17.7 Тест на подсчёт авто-корреляции                         |     |

|     | 17.8 Тест при запуске                                        |     |

|     | 17.9 Смешивание XOR                                          |     |

|     | 17.10 Обработка                                              |     |

|     | 17.11 FIFO                                                   |     |

|     | 17.12 LFSR                                                   |     |

|     | 17.13 Прерывания                                             |     |

|     | 17.14 Программирование ИГСЧ                                  |     |

|     | 17.15 Производительность                                     |     |

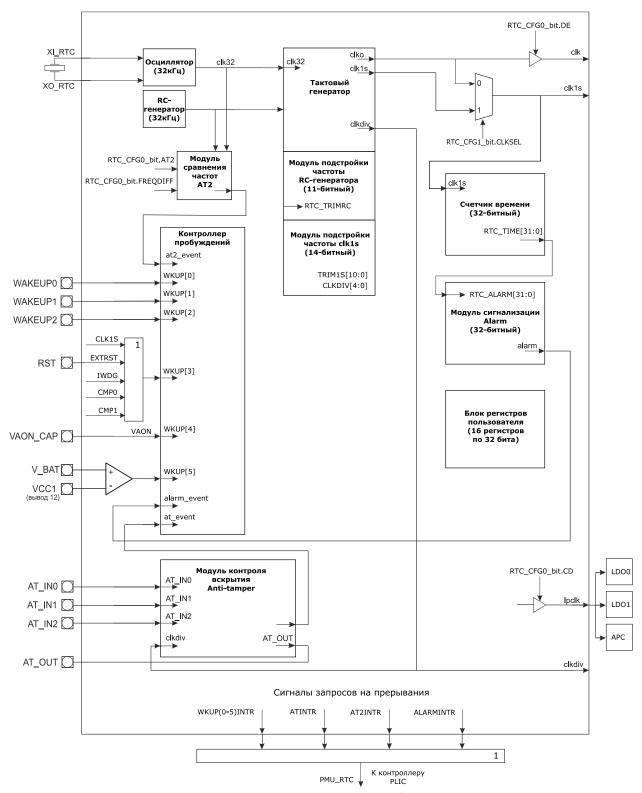

|     | Часы реального времени RTC                                   | 144 |

|     | 18.1 Особенности                                             | 146 |

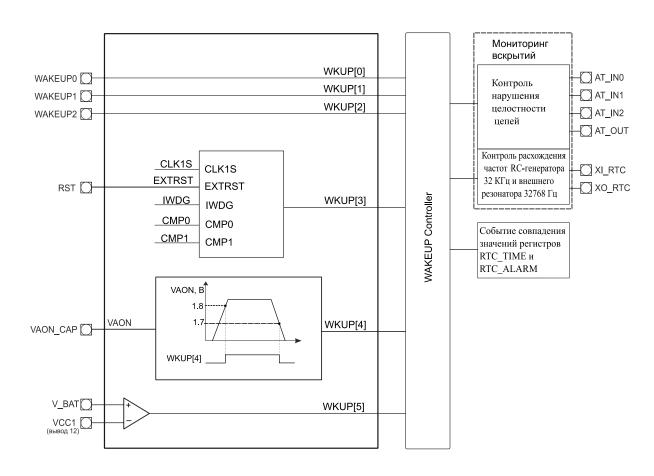

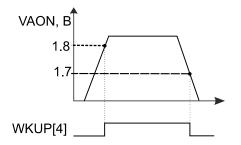

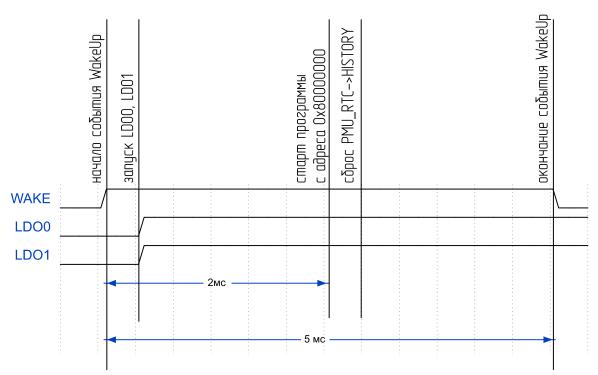

| 18.2 Контроллер пробужде                | ения WAKE                                         | 146 |

|-----------------------------------------|---------------------------------------------------|-----|

| 18.3 Мониторинг вскрыти                 | й                                                 | 149 |

| 18.4 Калибровка сигнала с               | односекундным периодом                            | 150 |

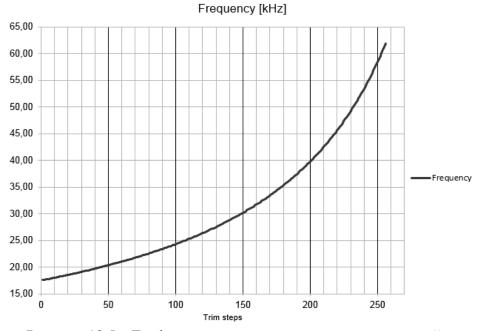

| 18.5 Калибровка тактового               | о сигнала RC-генератора                           | 151 |

|                                         | ключению и трассировке сигналов на печатной плате |     |

|                                         | й                                                 |     |

|                                         |                                                   |     |

|                                         | таймер IWDT                                       |     |

|                                         | ного приближения                                  |     |

|                                         |                                                   |     |

|                                         |                                                   |     |

| ,                                       | 0                                                 |     |

|                                         |                                                   |     |

|                                         | измерения                                         |     |

|                                         | 19.11.pe111.h                                     |     |

| ± ±                                     | ка АЦП                                            |     |

|                                         | I                                                 |     |

|                                         | апряжения                                         |     |

| <u> </u>                                | илитель                                           |     |

|                                         | яя                                                |     |

| • • •                                   |                                                   |     |

|                                         | ія АЦП                                            |     |

| 1 10                                    | 7111                                              |     |

| * *                                     |                                                   |     |

|                                         | аратора                                           |     |

|                                         | аратора                                           |     |

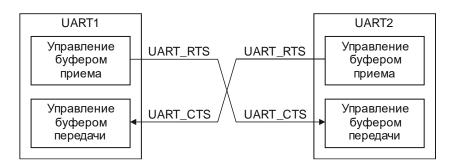

| 1 1                                     | пока UART                                         |     |

| · -                                     | IUNA UANT                                         |     |

|                                         | оступа к памяти                                   |     |

|                                         | оступа к памяти                                   |     |

| * *                                     |                                                   |     |

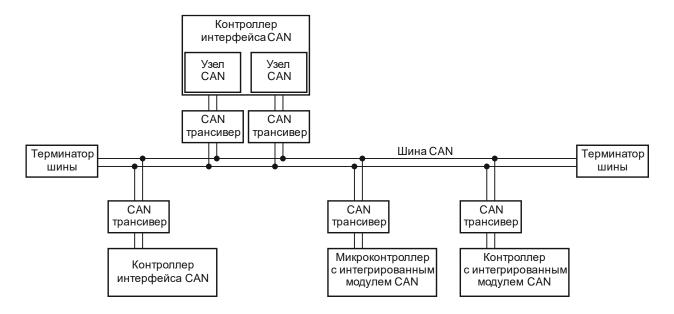

|                                         | AN 2.0b                                           |     |

| 1 1 11                                  | AIN 2.00                                          |     |

| 1                                       |                                                   |     |

|                                         | нирование контроллера CAN                         |     |

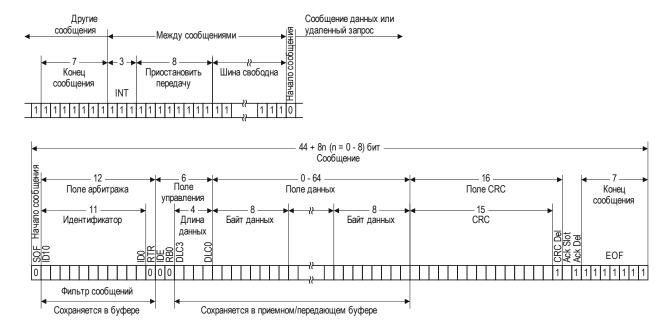

|                                         |                                                   |     |

|                                         |                                                   |     |

|                                         | бщений                                            |     |

|                                         | ий                                                |     |

|                                         |                                                   |     |

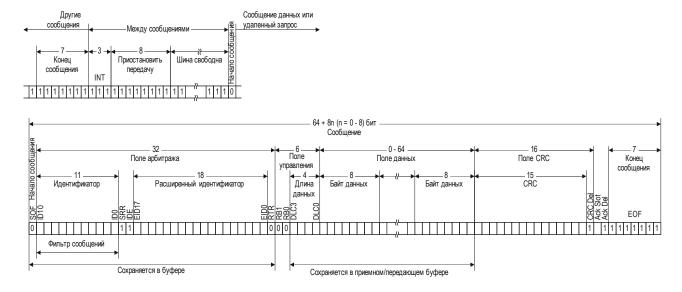

|                                         | имы передачи                                      |     |

| - · · · · · · · · · · · · · · · · · · · | тов сообщений                                     |     |

|                                         | ~ ~                                               |     |

|                                         | ов сообщений                                      |     |

|                                         | контроллера СА                                    |     |

|                                         | ости передачи 1Мбит/с                             |     |

|                                         | C                                                 |     |

|                                         |                                                   |     |

|                                         | сание                                             |     |

|                                         | кционирование                                     |     |

|                                         | SPI                                               |     |

|                                         | pa QSPI                                           |     |

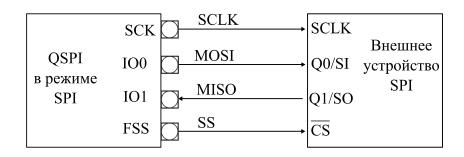

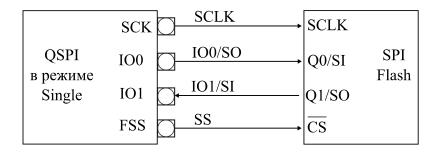

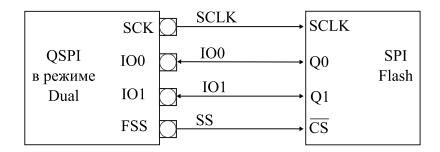

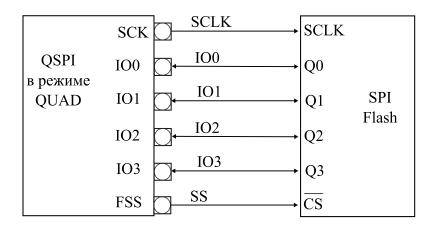

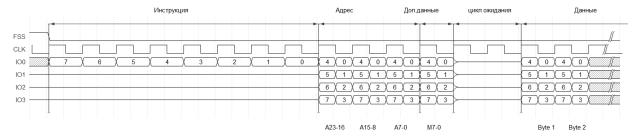

| 28.2 Режим работы SPI                   |                                                   | 264 |

| 28.3 Последовательность команд QSPI                                   | 265 |

|-----------------------------------------------------------------------|-----|

| 28.4 Режимы протокола интерфейса сигнала QSPI                         |     |

| 28.5 Программирование QSPI                                            |     |

| 28.6 Бит занятости QSPI и функция прерывания                          | 270 |

| 28.7 Поведение сигнала FSS                                            |     |

| 28.8 Прерывания QSPI                                                  | 270 |

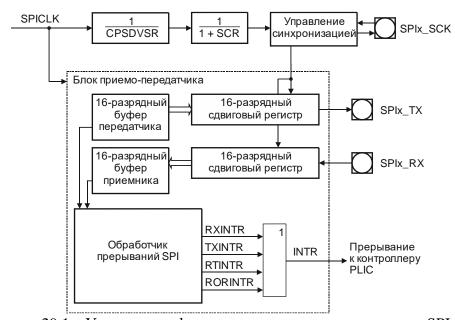

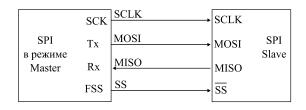

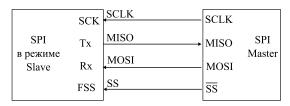

| 29 Контроллер интерфейса SPI                                          |     |

| 29.1 Структура контроллера SPI                                        |     |

| 29.2 Интерфейс прямого доступа к памяти                               |     |

| 29.3 Функционирование                                                 |     |

| 29.4 Прерывания                                                       |     |

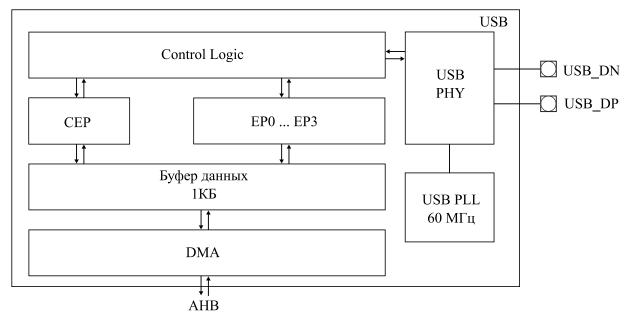

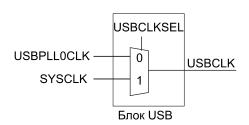

| 30 Контроллер интерфейса USB FullSpeed                                | 279 |

| 30.1 Функции устройства                                               |     |

| 30.2 Работа устройства                                                |     |

| 30.3 Рекомендации по программированию                                 | 282 |

| 31 Программно-аппаратные средства отладки                             | 284 |

| Заключение                                                            | 285 |

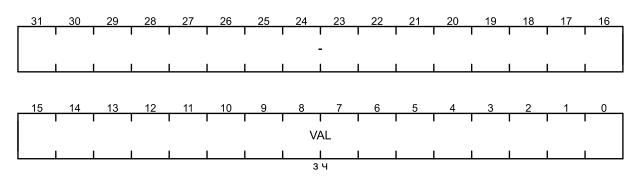

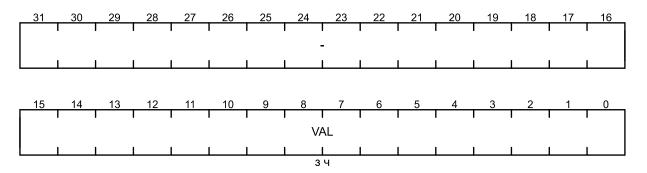

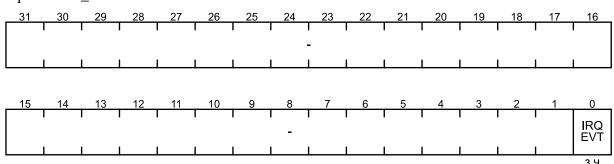

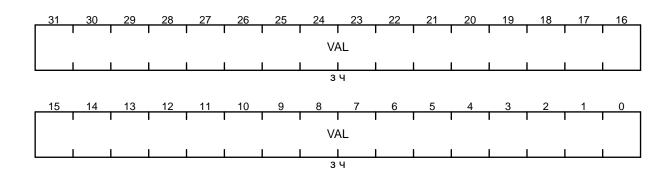

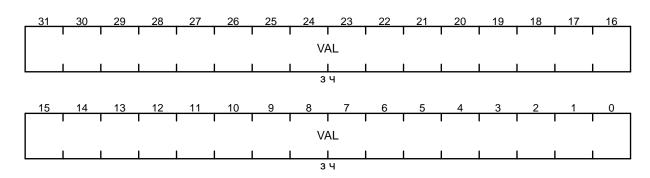

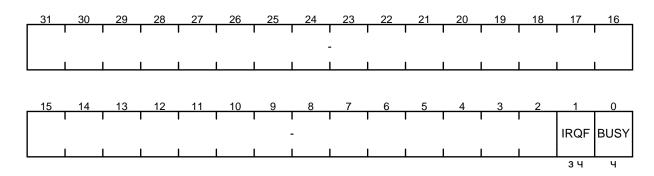

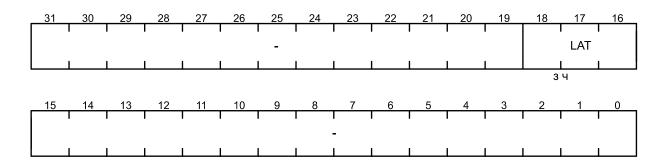

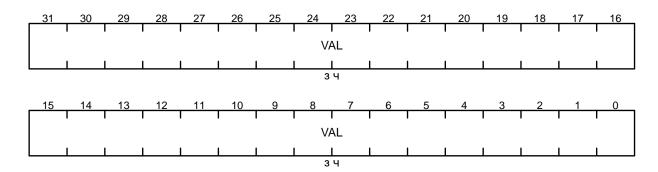

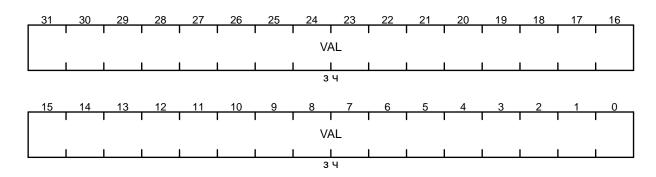

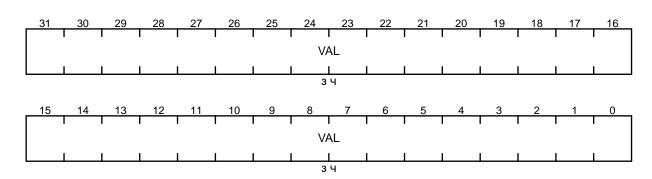

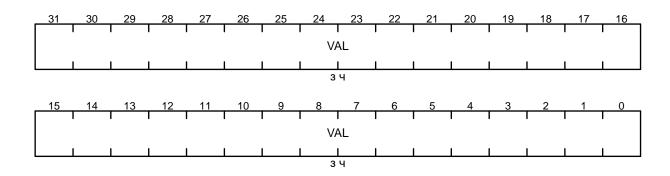

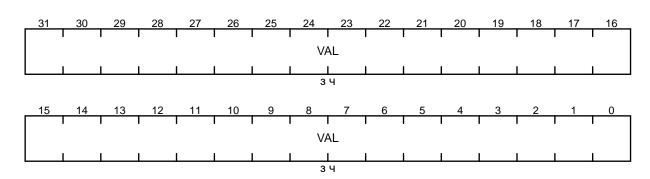

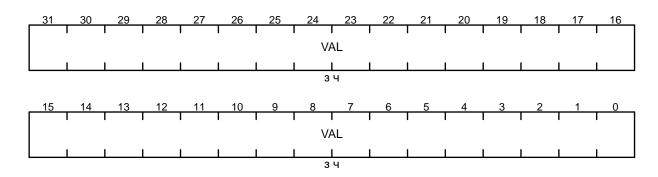

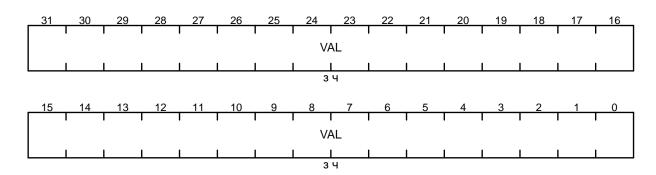

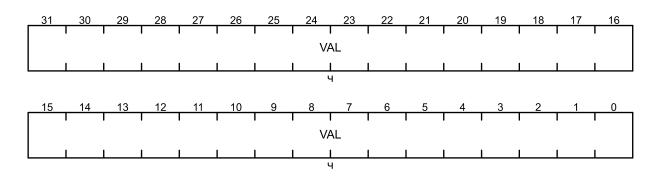

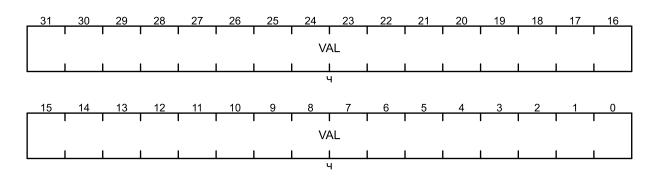

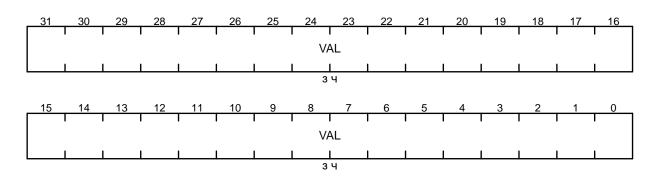

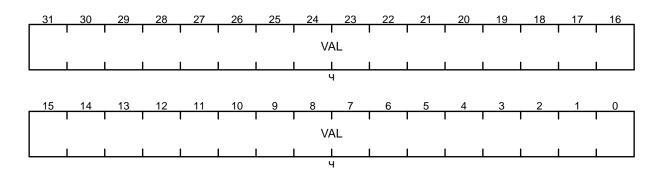

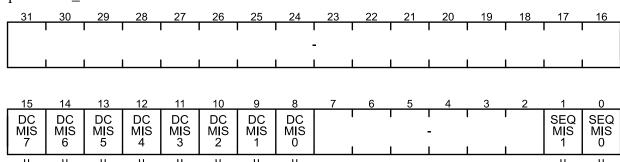

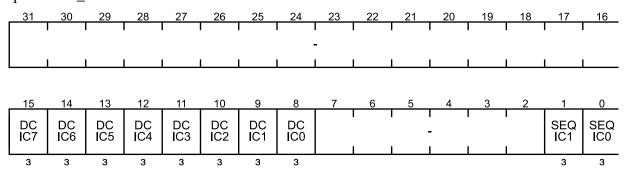

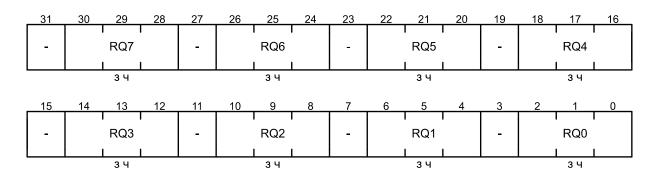

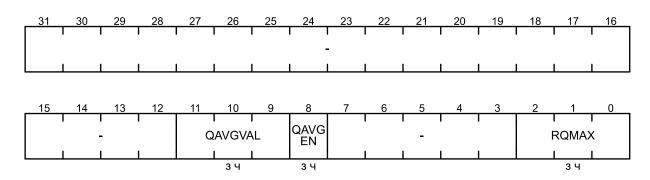

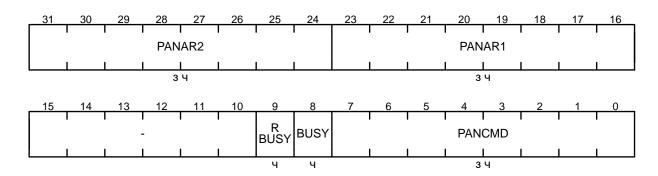

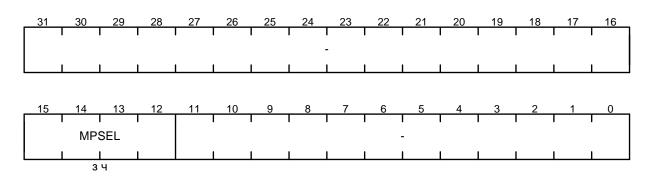

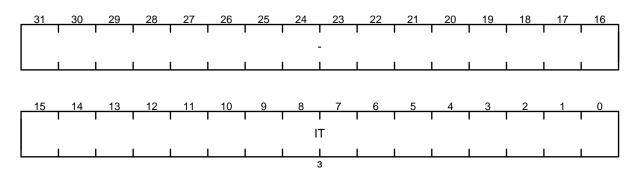

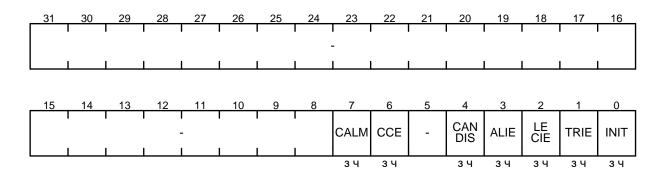

| Приложение А (обязательное) Регистры микроконтроллера                 | 286 |

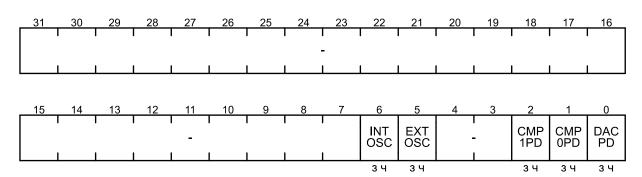

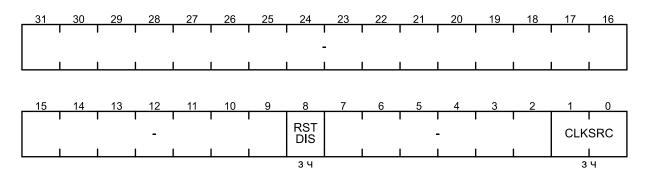

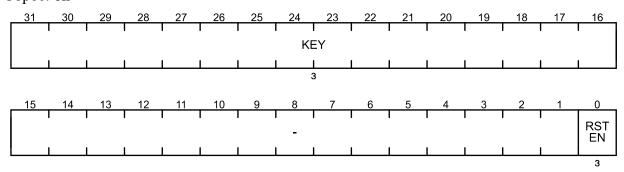

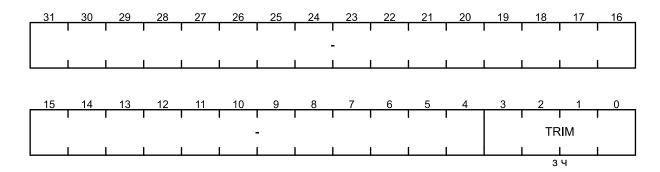

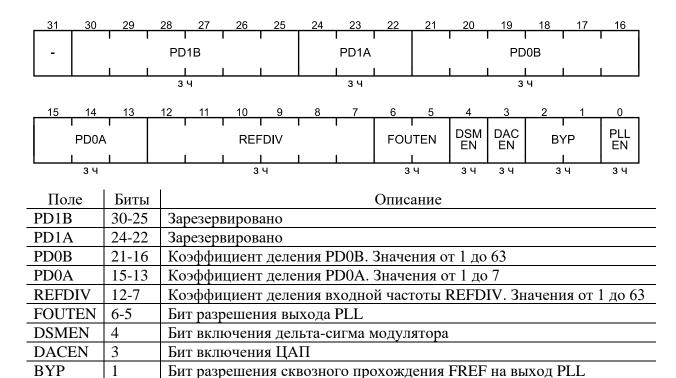

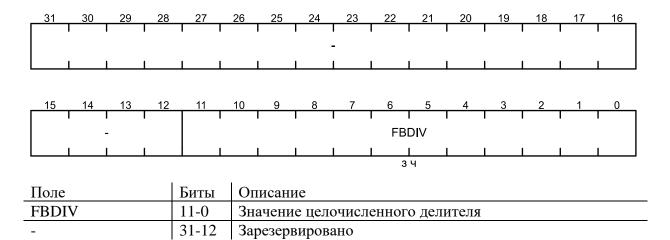

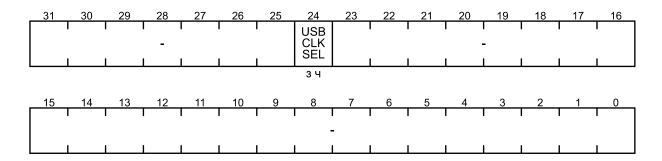

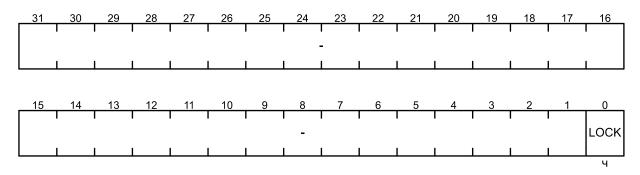

| А.1 Регистры блока управления сбросом и синхронизацией RCU            | 286 |

| А.2 Регистры блока управления энергопотреблением PMUSYS               | 305 |

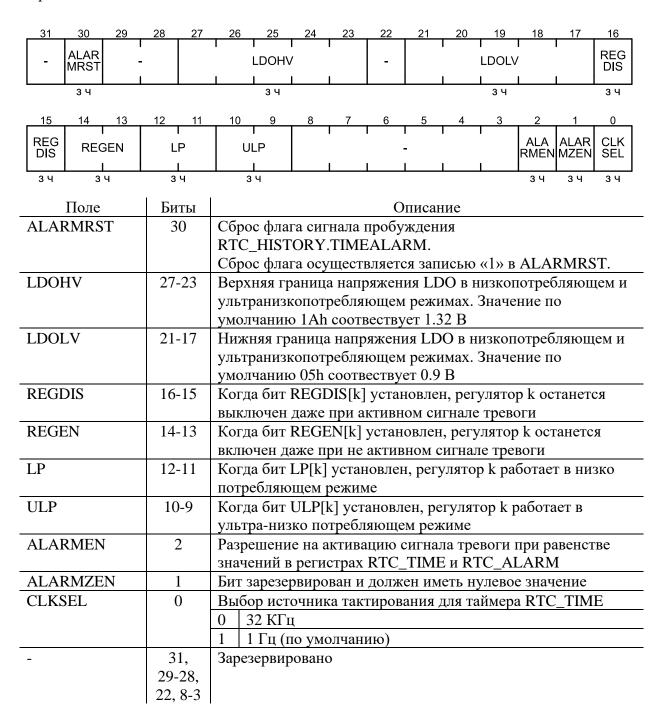

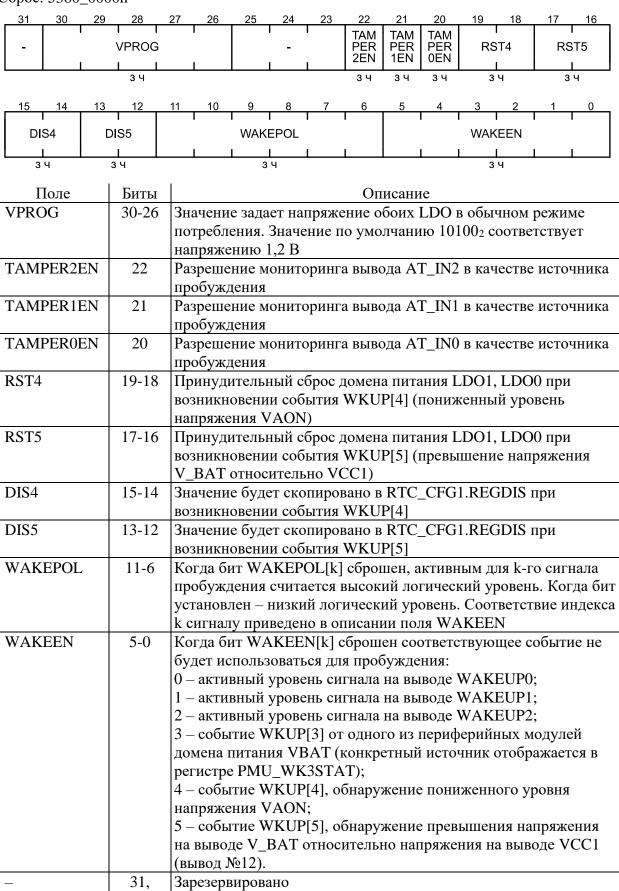

| А.3 Регистры блока управления энергопотреблением PMURTC               | 310 |

| А.4 Регистры контроллера Flash-памяти                                 |     |

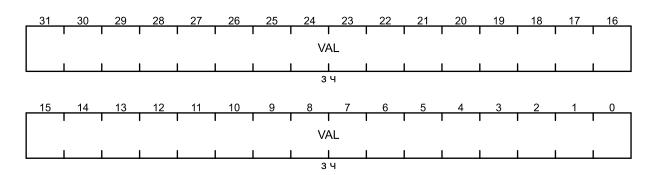

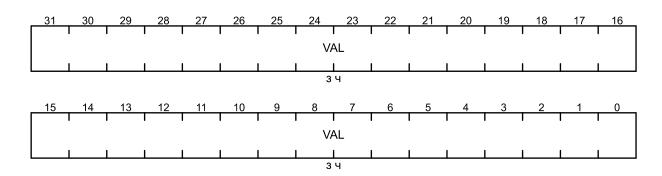

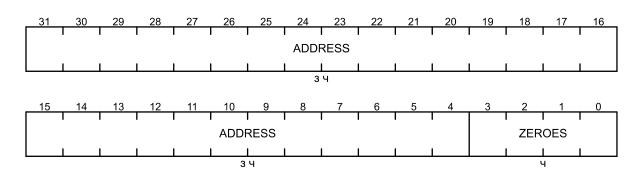

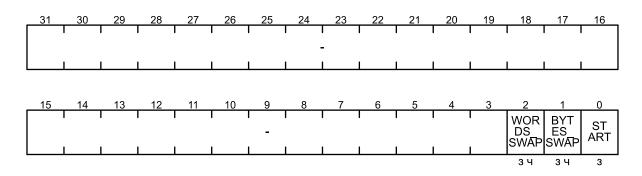

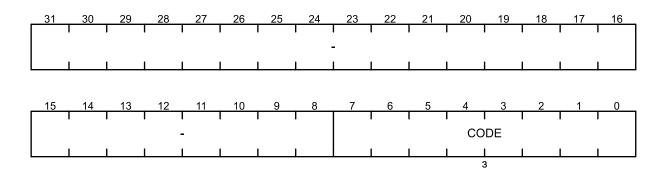

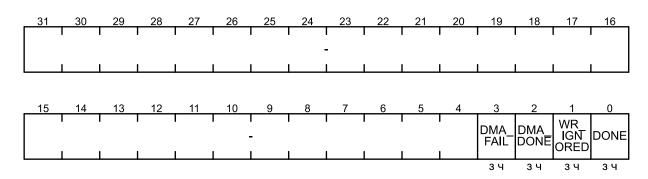

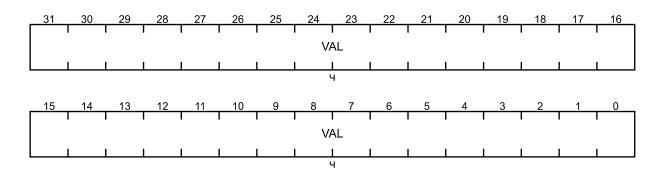

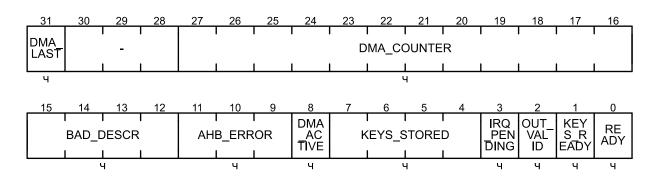

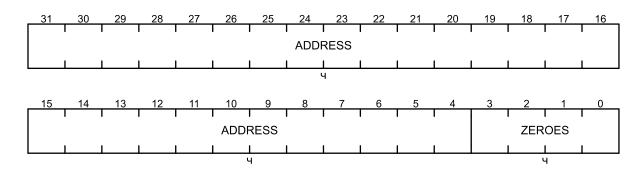

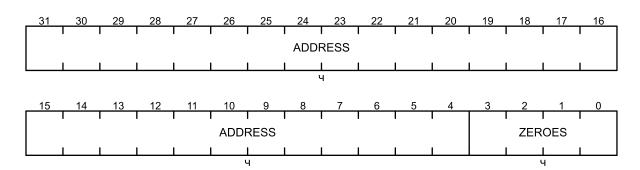

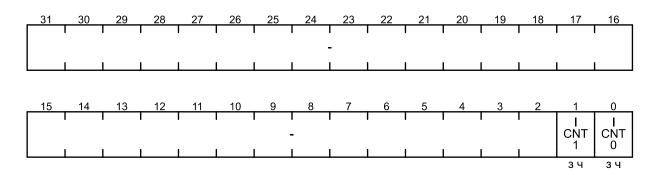

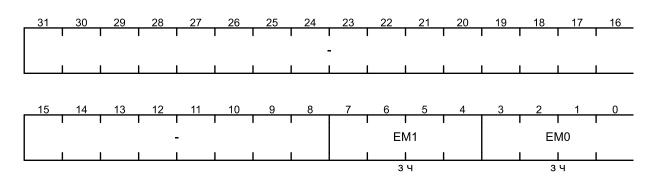

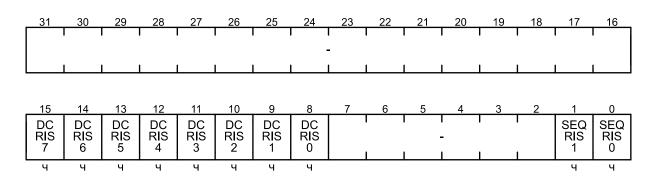

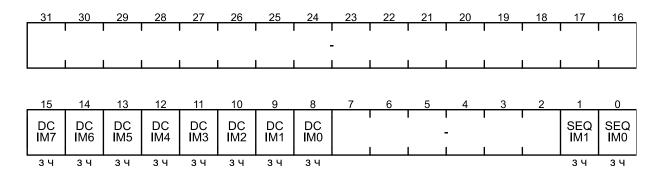

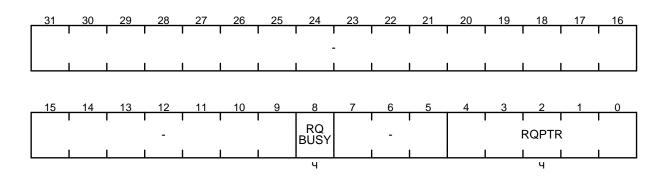

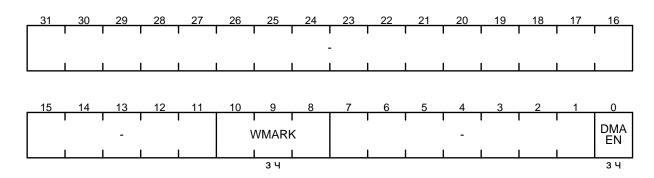

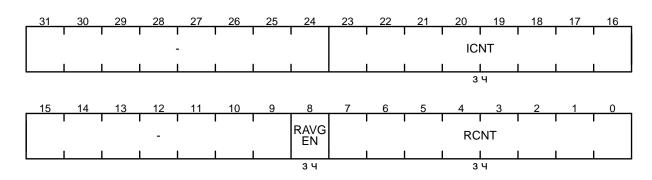

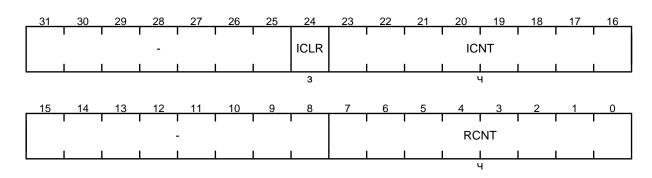

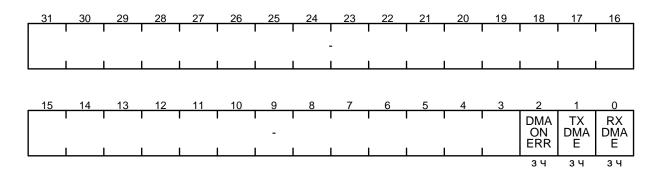

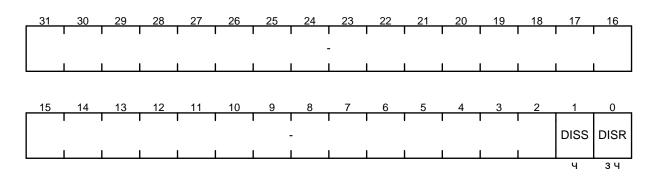

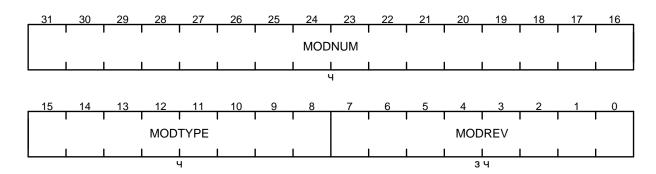

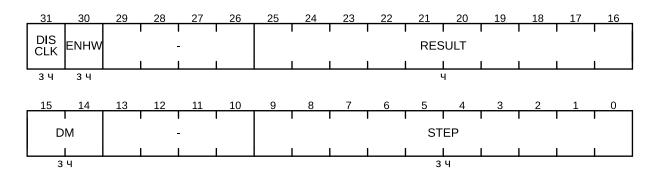

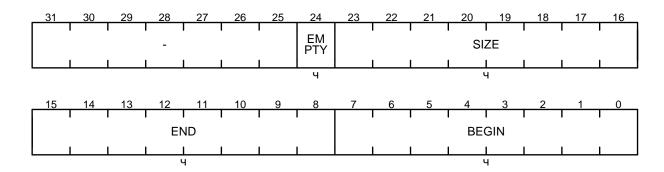

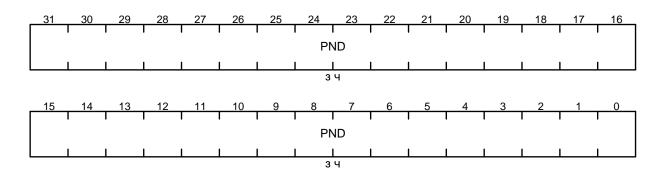

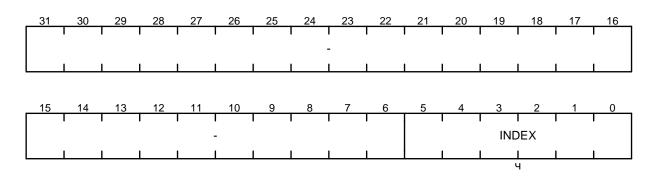

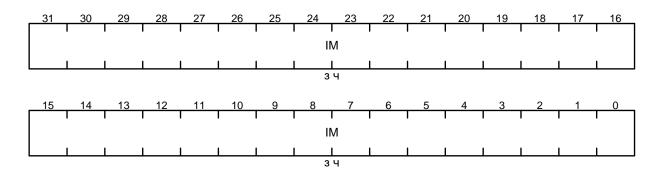

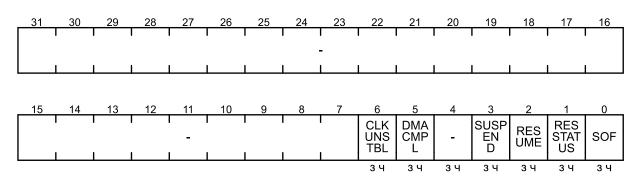

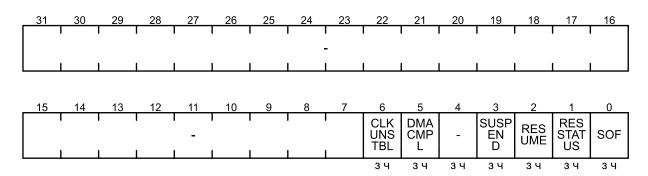

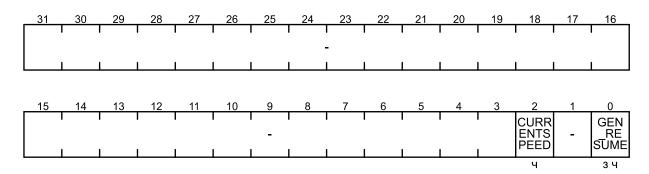

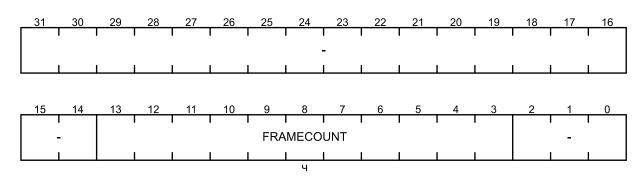

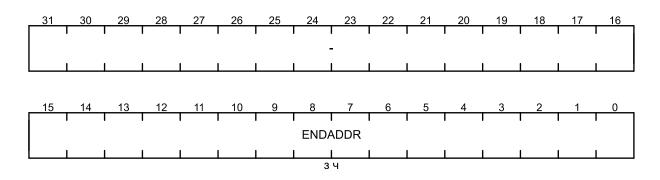

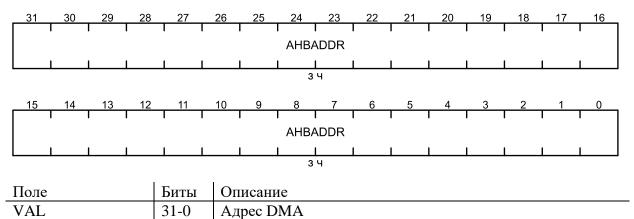

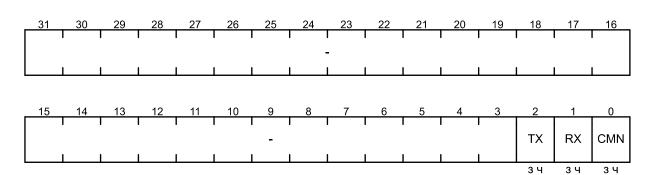

| А.5 Регистры контроллера прямого доступа к памяти DMA                 | 335 |

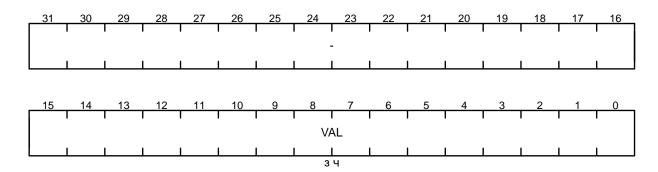

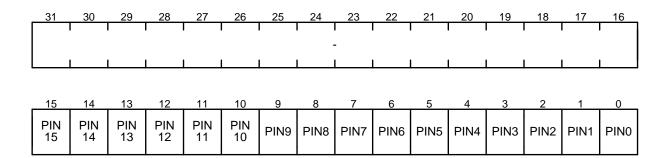

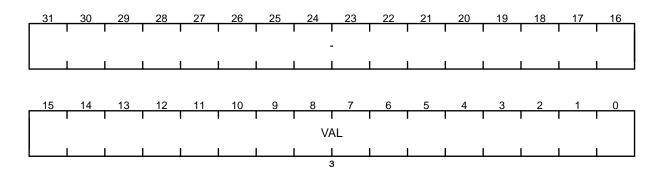

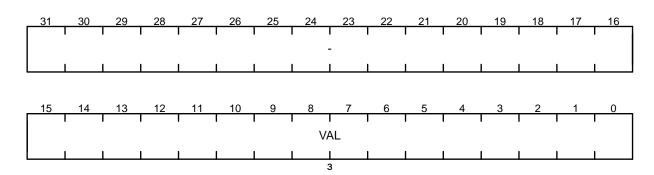

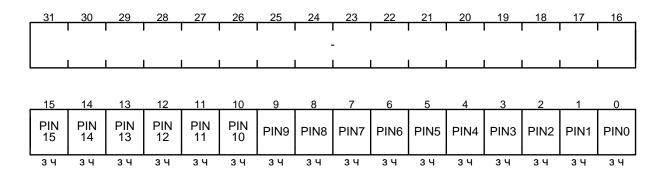

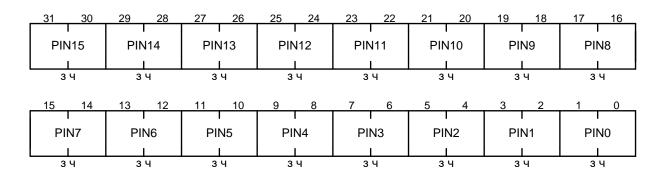

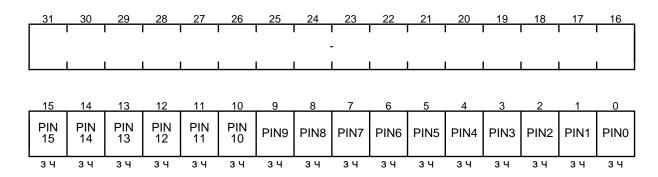

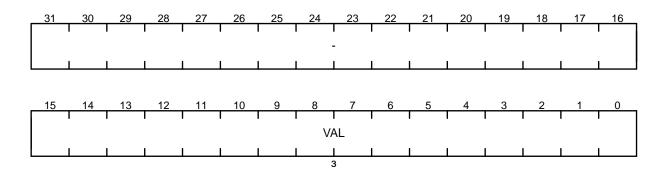

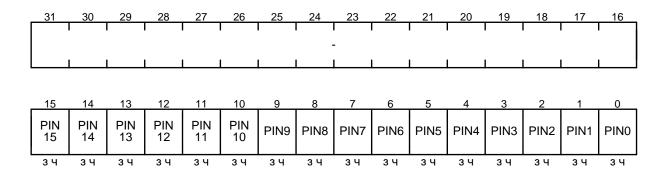

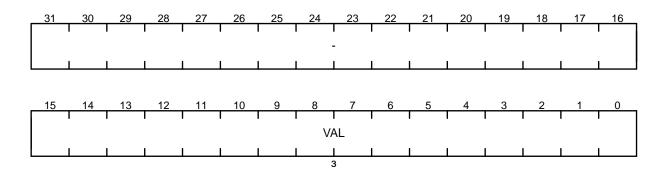

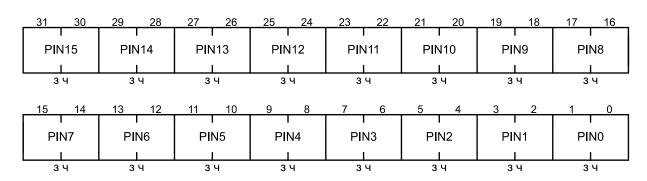

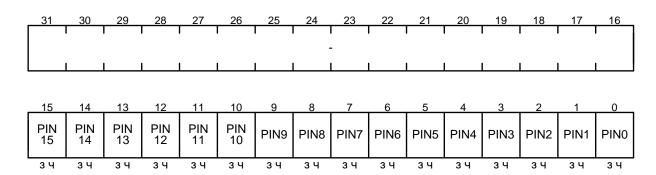

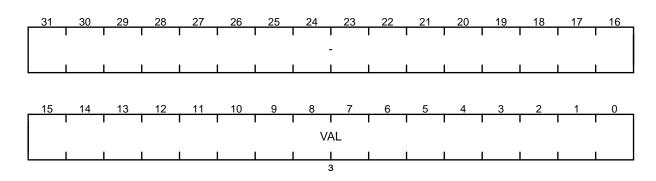

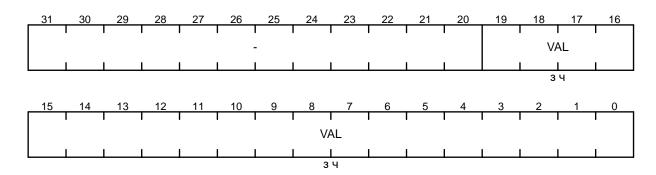

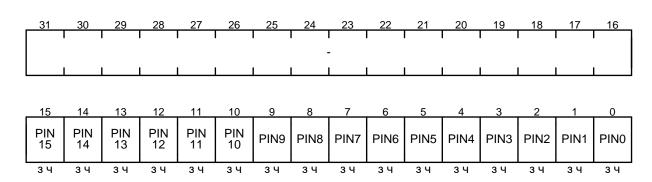

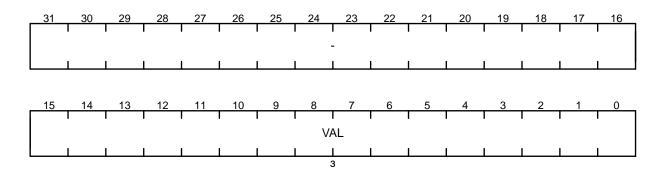

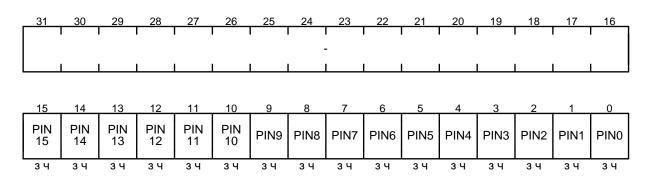

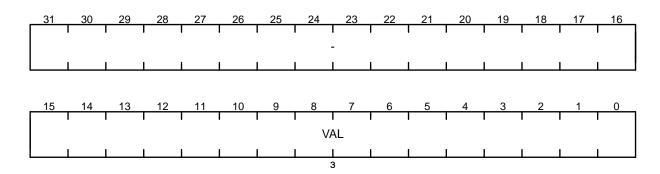

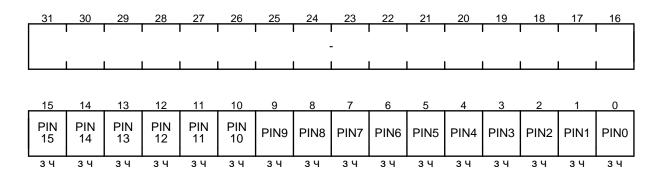

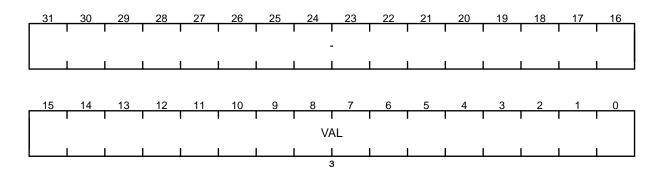

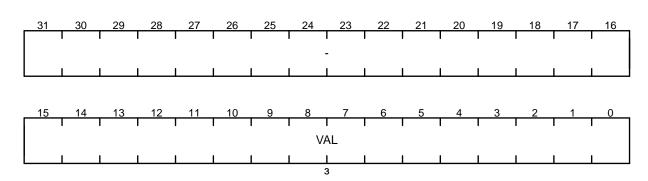

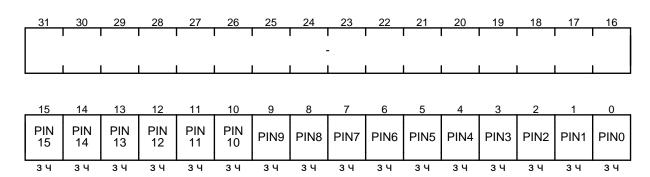

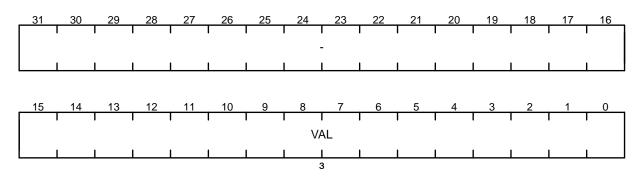

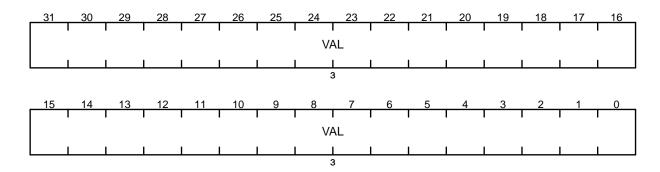

| А.6 Регистры портов ввода-вывода                                      | 347 |

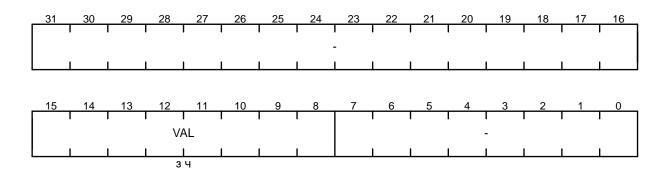

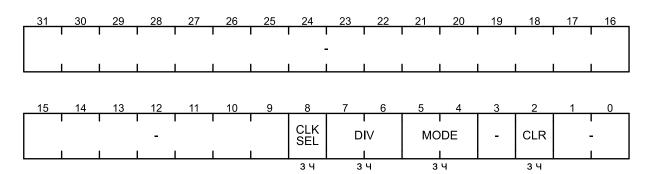

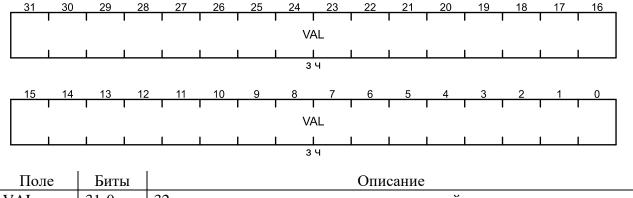

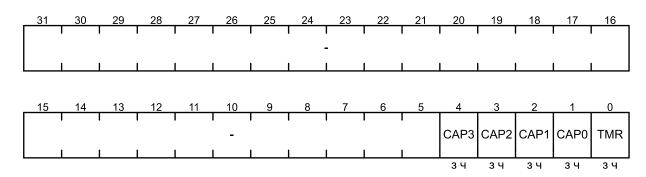

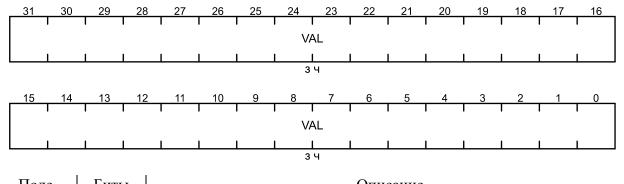

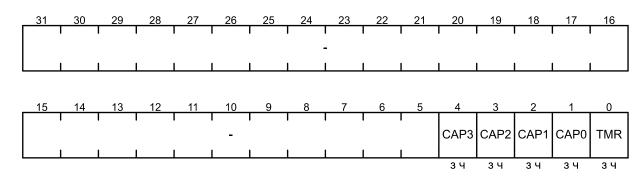

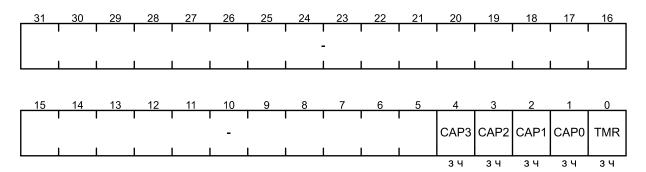

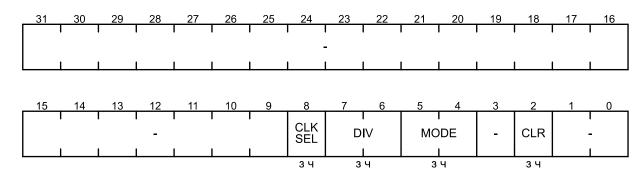

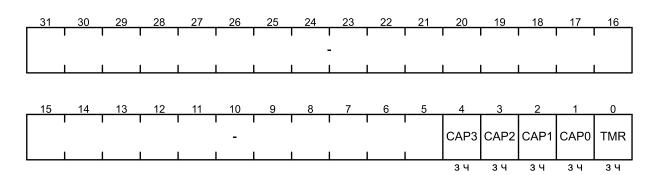

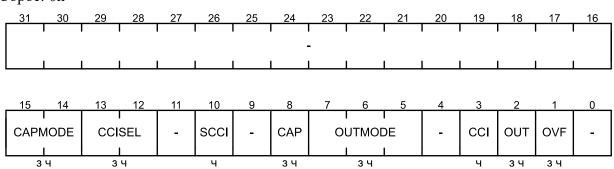

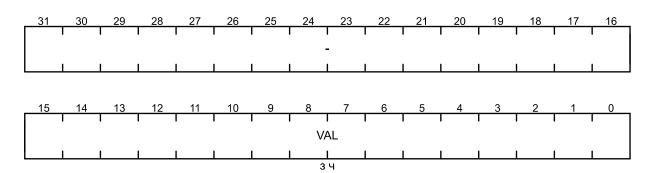

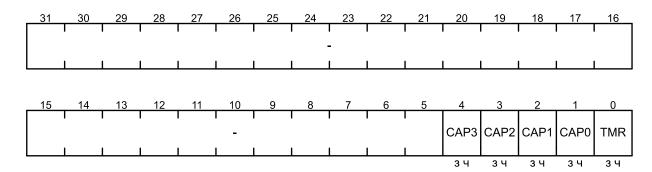

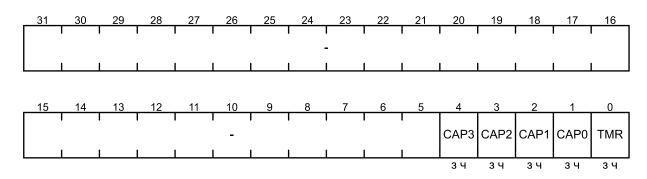

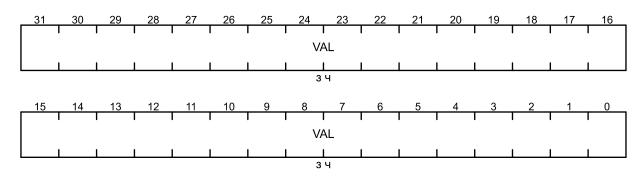

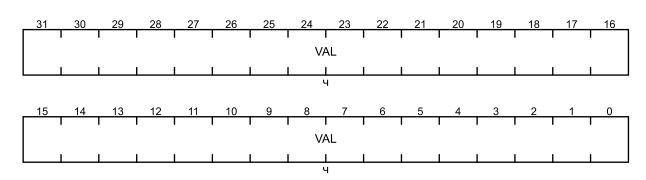

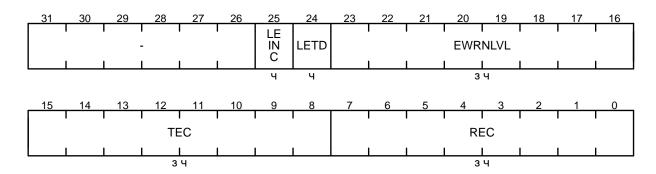

| А.7 Регистры 32-разрядного таймера TMR32                              |     |

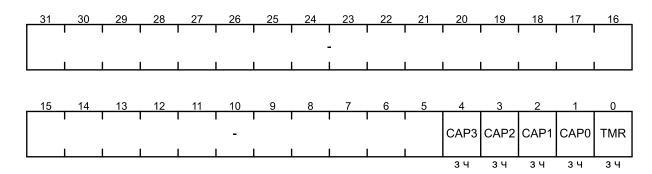

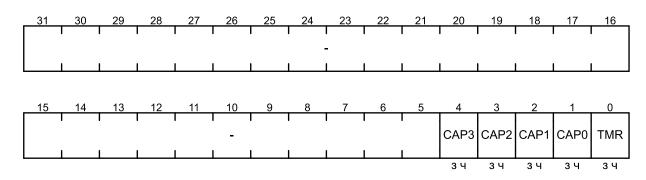

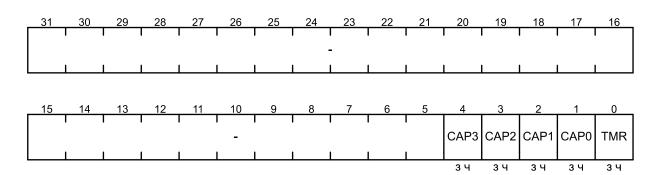

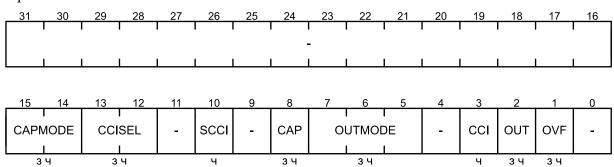

| А.8 Регистры 16-разрядного таймера TMR                                |     |

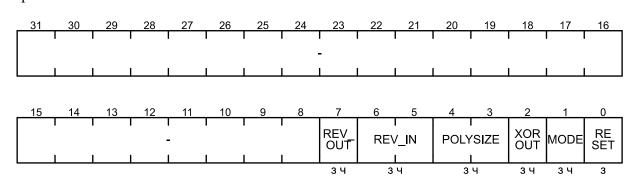

| А.9 Регистры блока подсчета циклического избыточного кода CRC         |     |

| А.10 Регистры блока HASH                                              |     |

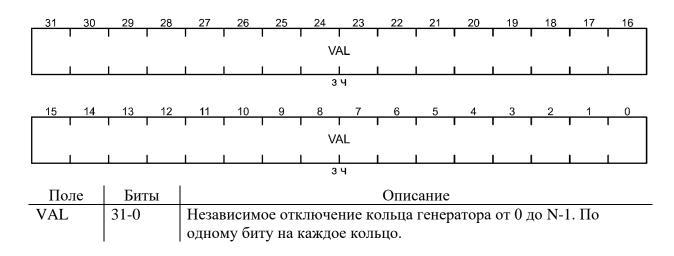

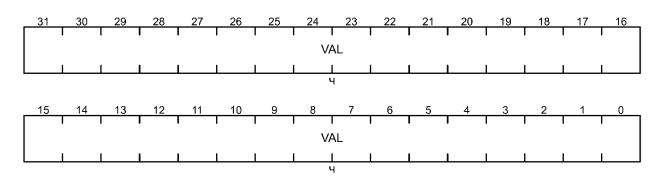

| А.11 Регистры генератора случайных чисел ИГСЧ                         | 391 |

| А.12 Регистры блока CRYPTO                                            |     |

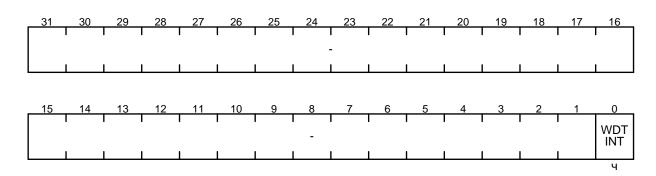

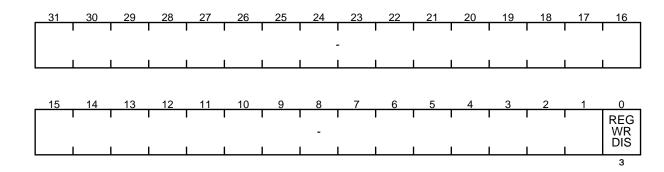

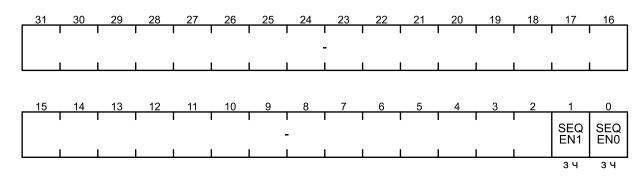

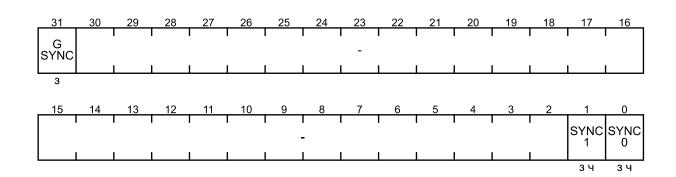

| А.13 Регистры сторожевых таймеров WDT и IWDT                          |     |

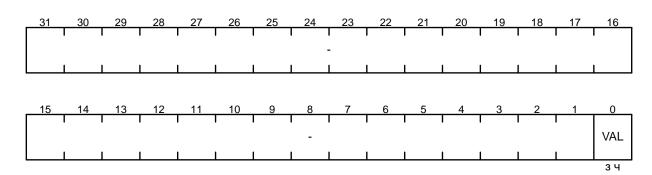

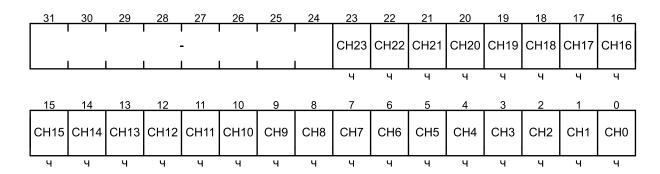

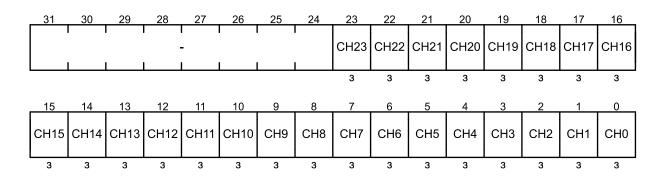

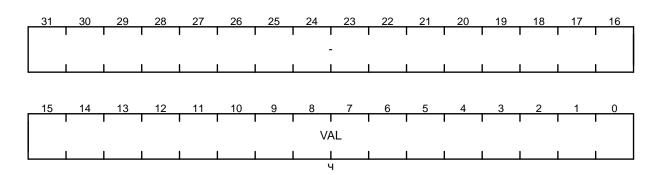

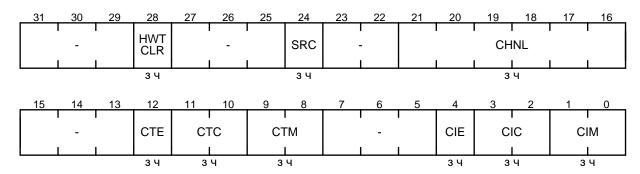

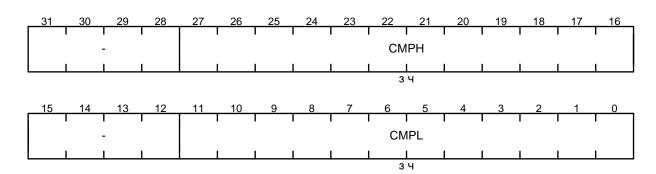

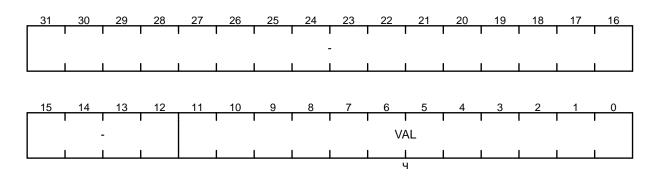

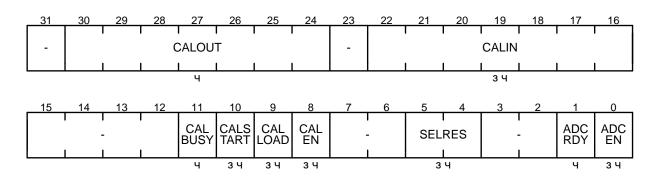

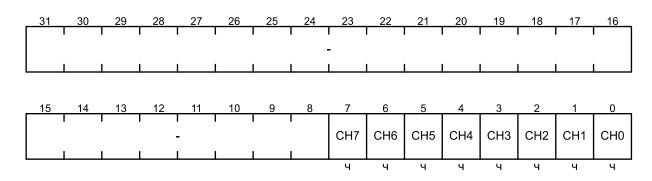

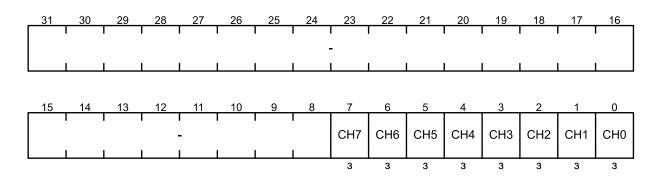

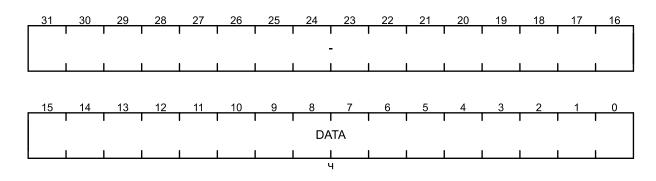

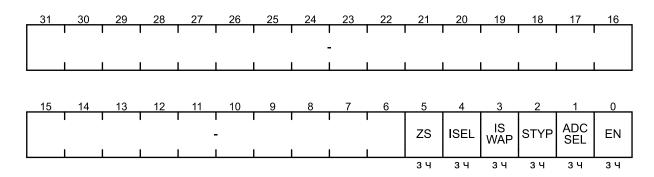

| А.14 Регистры блока АЦП последовательного приближения                 |     |

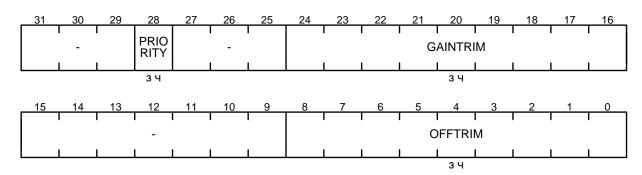

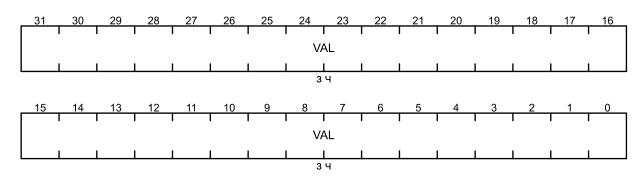

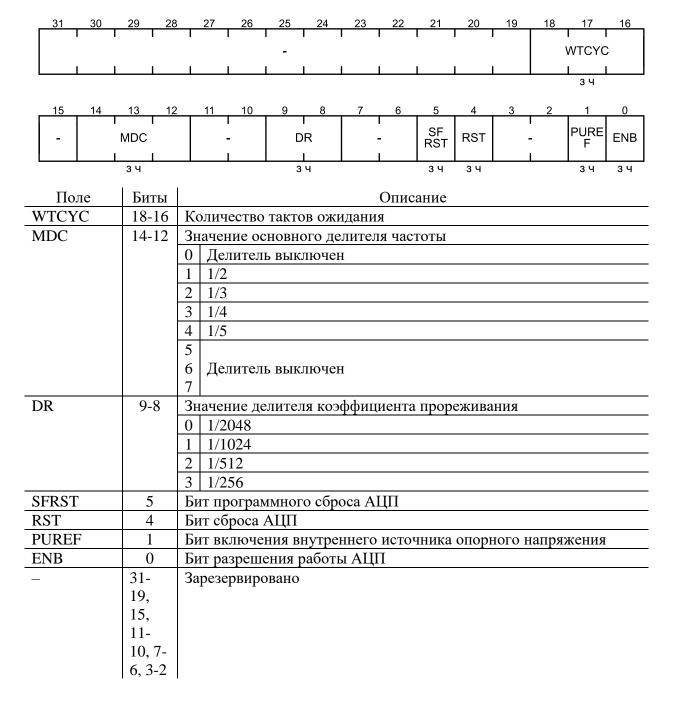

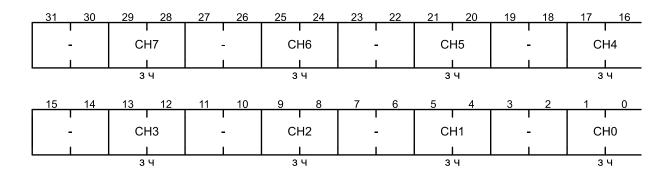

| А.15 Регистры сигма-дельта АЦП                                        |     |

| А.16 Регистры управления датчиком температуры                         |     |

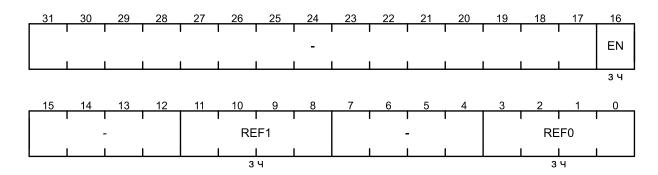

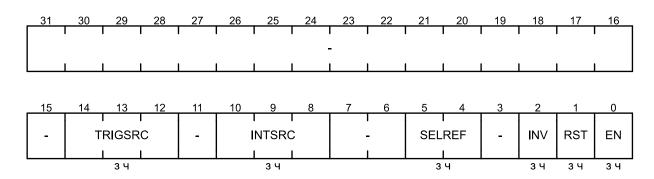

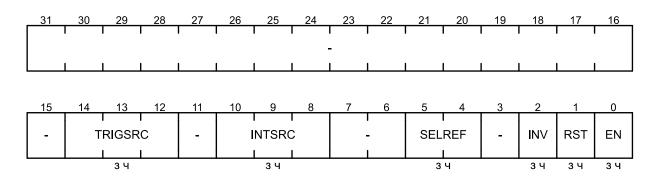

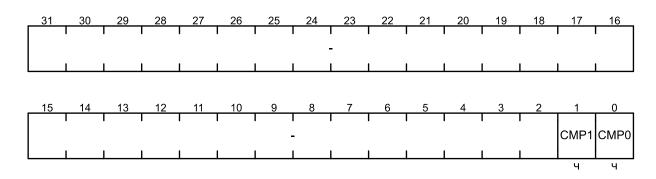

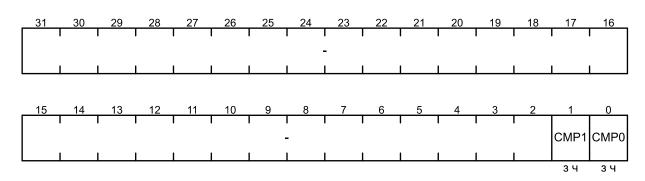

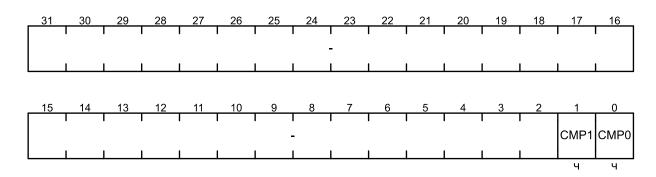

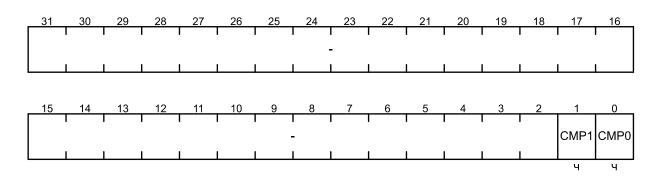

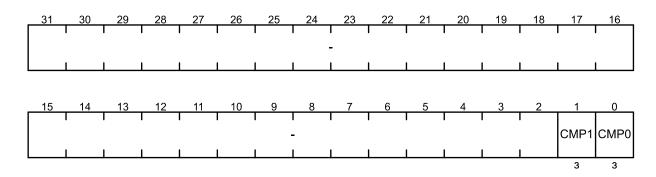

| А.17 Регистры управления аналоговым компаратором                      |     |

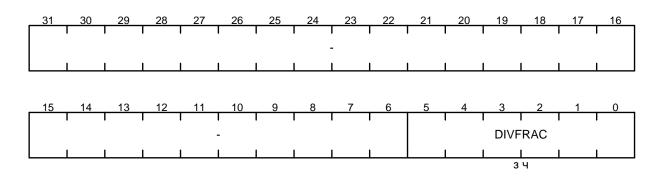

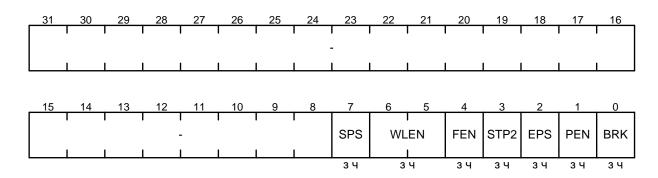

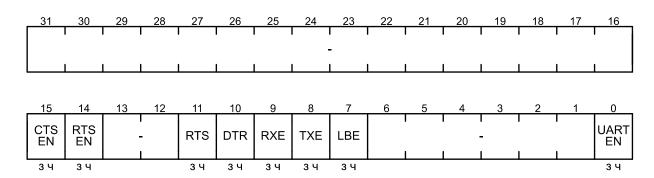

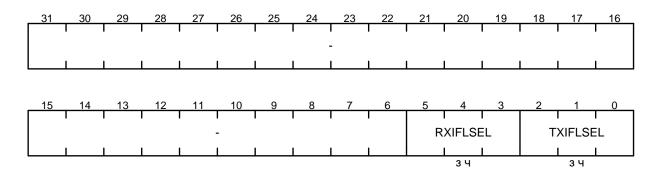

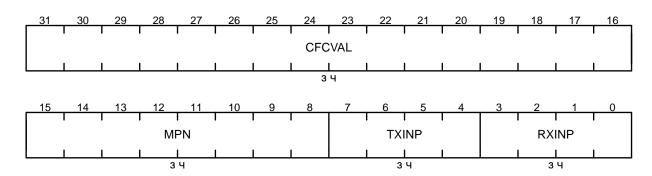

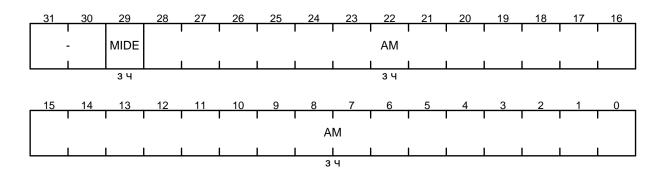

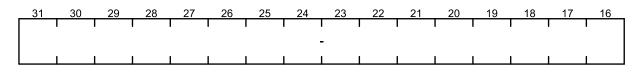

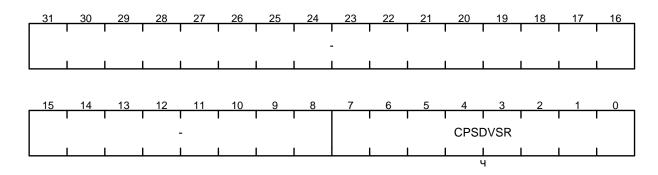

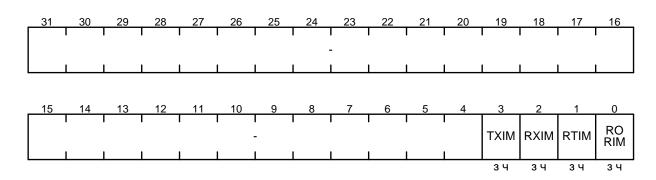

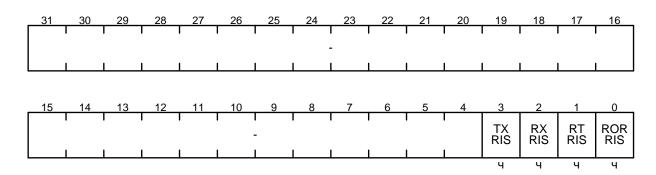

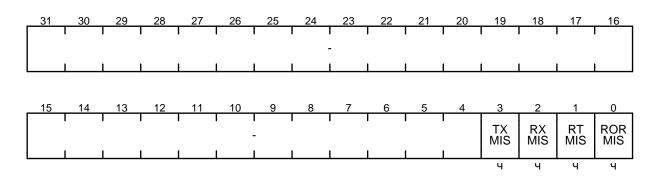

| А.18 Регистры приемопередатчика UART                                  |     |

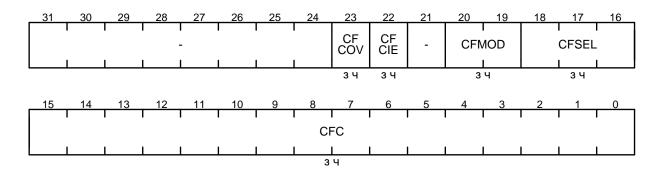

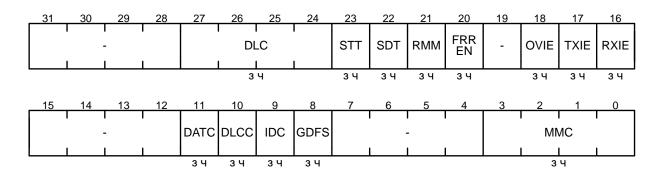

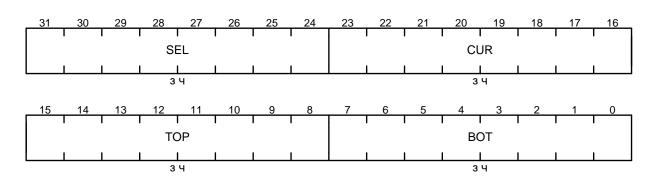

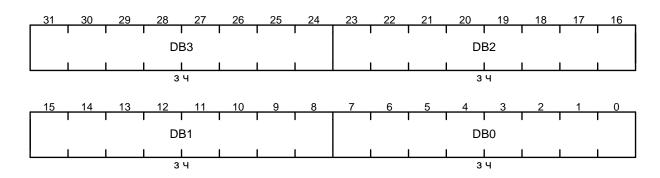

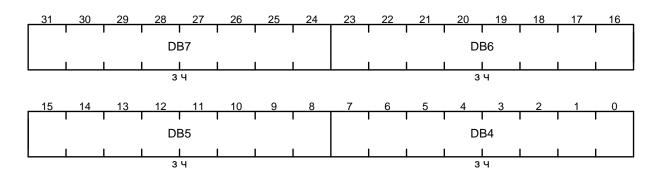

| А.19 Регистры контроллера интерфейса CAN 2.0b                         |     |

| А.20 Регистры контроллера интерфейса I2С                              |     |

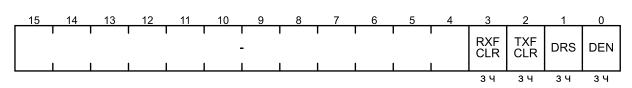

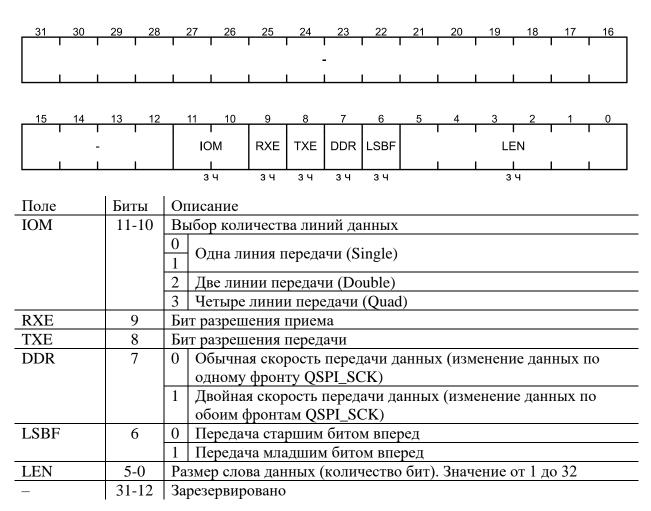

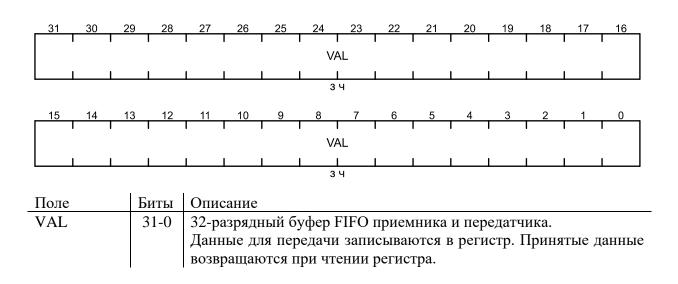

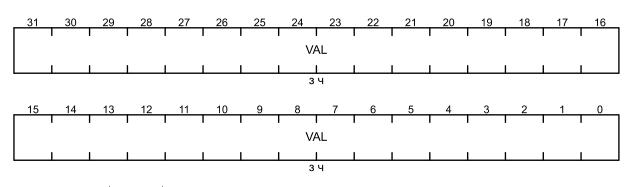

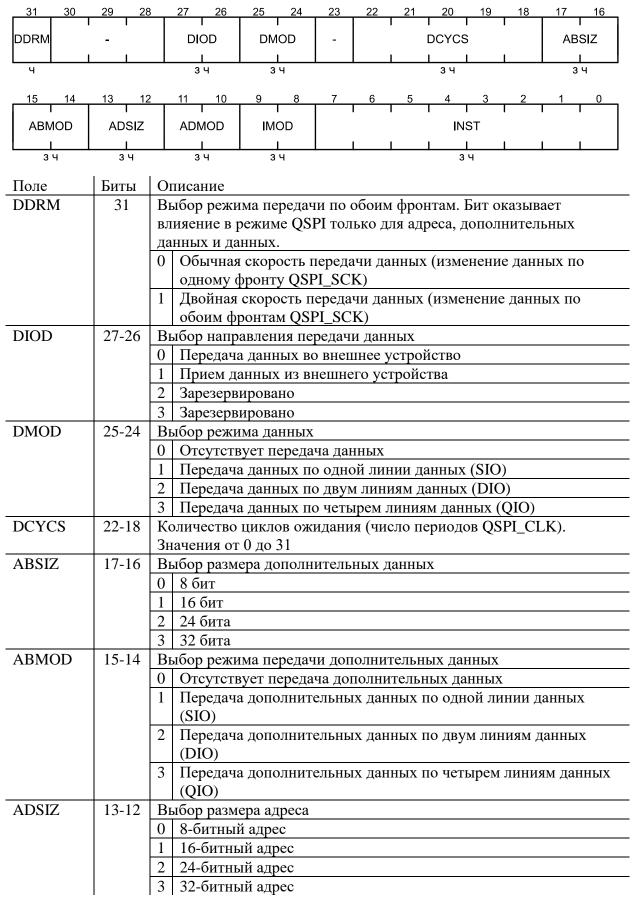

| А.21 Регистры контроллера интерфейса QSPI                             |     |

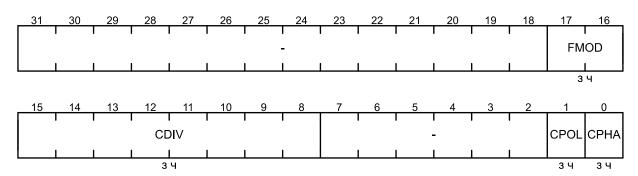

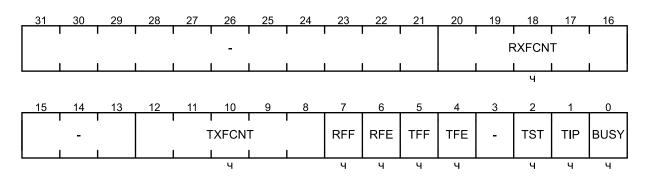

| А.22 Регистры контроллера интерфейса SPI                              |     |

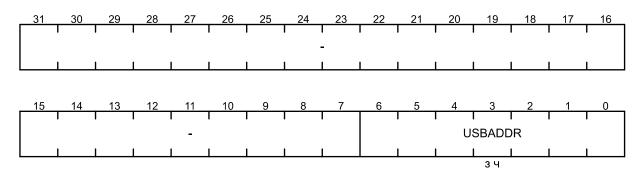

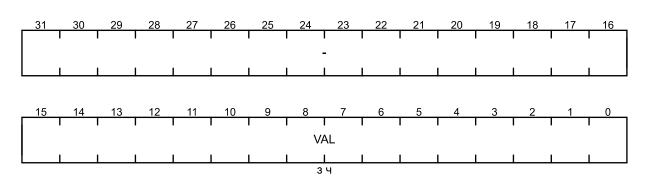

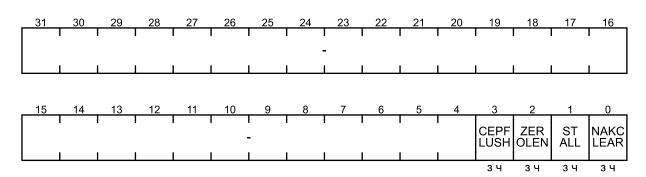

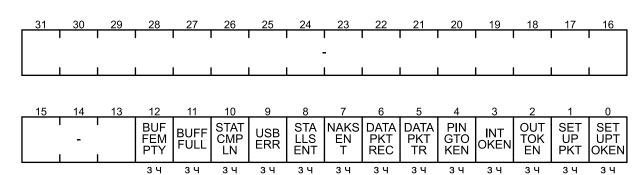

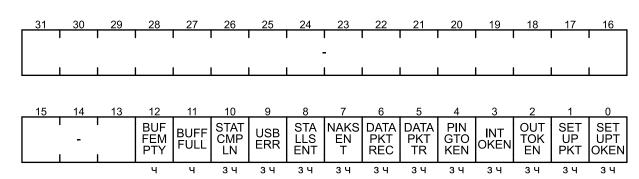

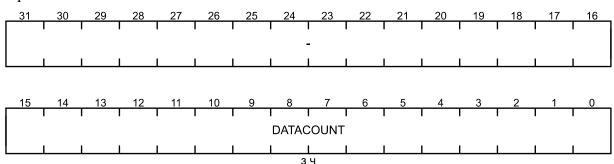

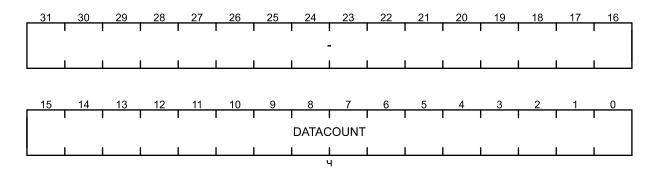

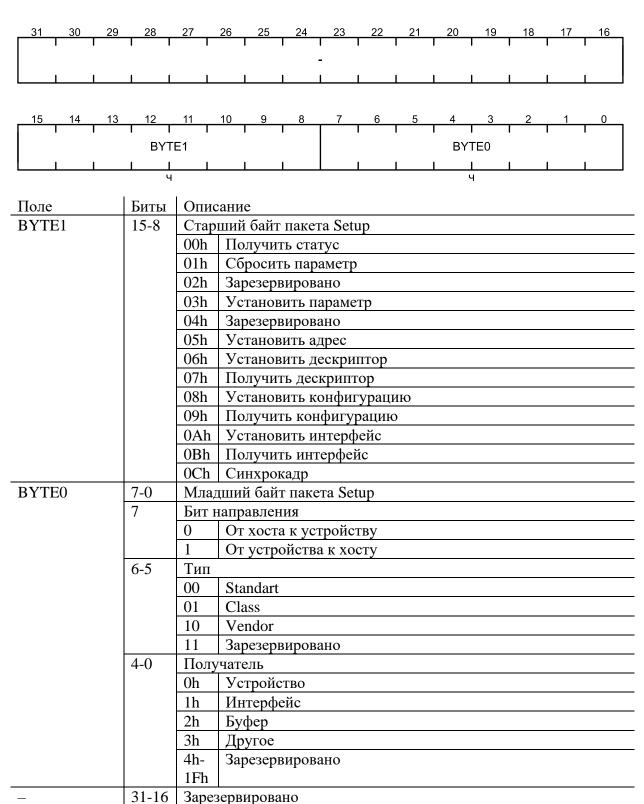

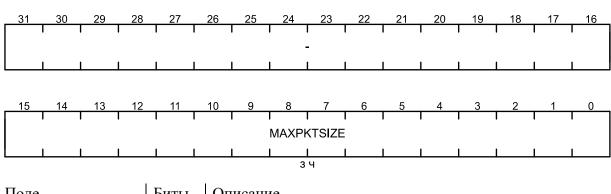

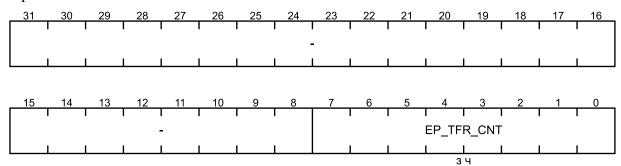

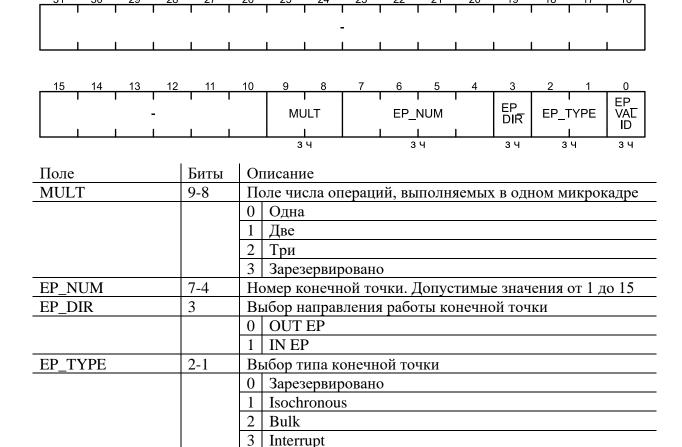

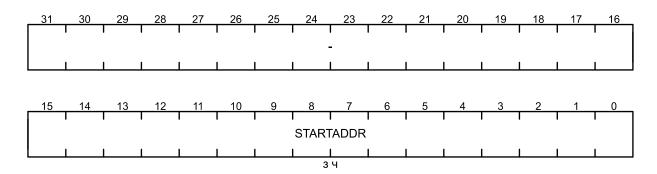

| А.23 Регистры контроллера интерфейса USB                              |     |

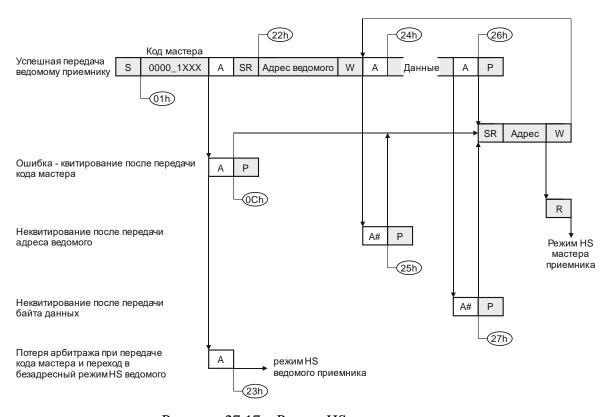

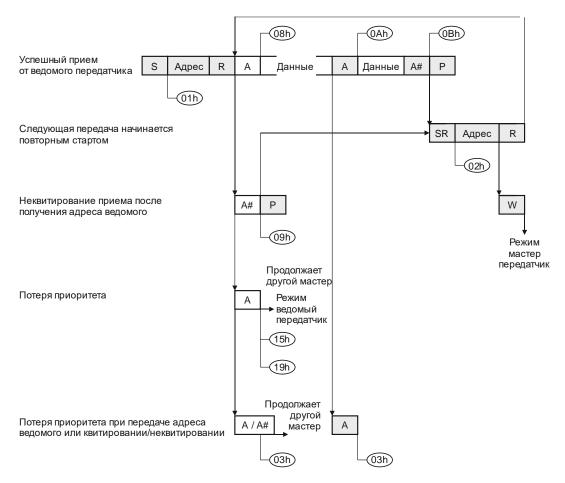

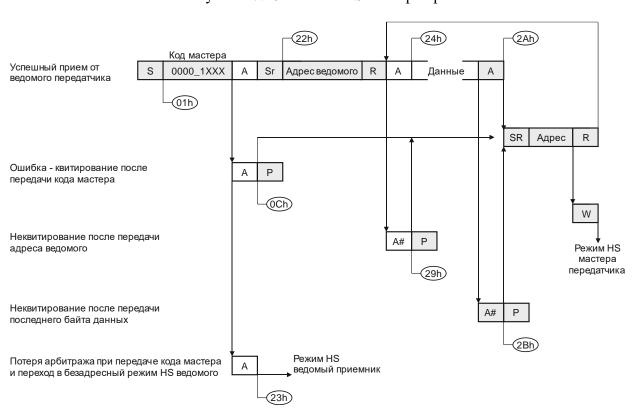

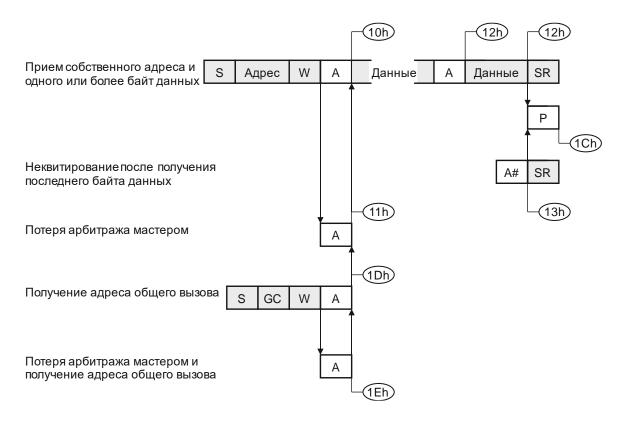

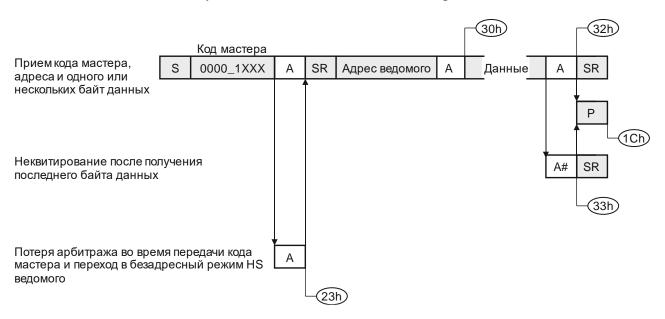

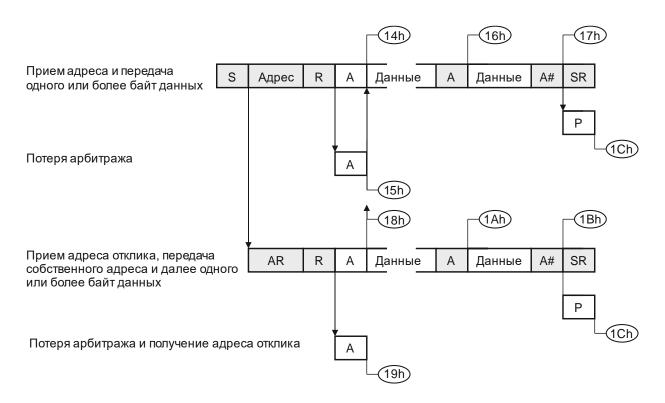

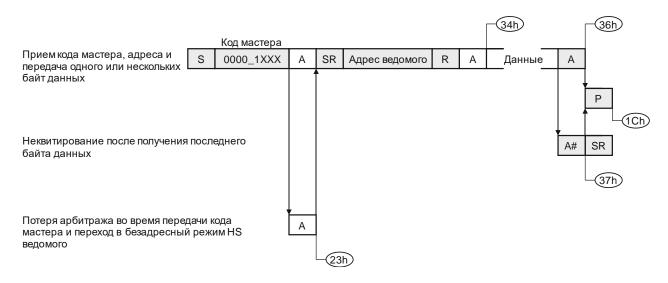

| Приложение Б (обязательное) Коды состояний функционирования блока I2С |     |

| Приложение В (обязательное) Токи потребления микроконтроллера         |     |

| Приложение Г (обязательное) Назначение выводов в корпусе              |     |

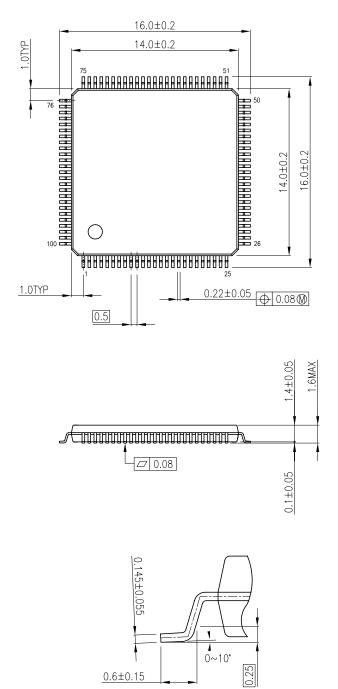

| Приложение Д (обязательное) Габаритный чертеж корпуса LQFP100         | 552 |

#### Введение

Микросхема К1921ВГ015 представляет собой СБИС 32-разрядного микроконтроллера на базе ядра RISC-V, предназначенного для промышленных и приложений, включая потребительских системы дистанционного мониторинга, контрольно-измерительные приборы, системы автоматизации производственных процессов, автомобильную электронику, а также устройства с батарейным питанием.

В состав микроконтроллера входит широкий набор цифровой и аналоговой периферии, поэтому, он может применяться в различных системах цифровой обработки сигналов, в том числе, требующих точных аналогово-цифровых преобразований, в системах управления и сбора информации.

Микросхема выполняется в корпусе LQFP100, а также в бескорпусном исполнении.

Условное обозначение микросхемы в бескорпусном исполнении – К1921ВГ01Н.

В настоящем техническом описании приведено описание архитектуры, функционального построения и периферии микроконтроллера К1921ВГ015 и К1921ВГ01Н.

Техническое описание может служить практическим руководством по применению микроконтроллера для разработчиков систем на его основе и программистов.

## 1 Область применения и особенности микроконтроллера

Сфера применения микросхемы К1921ВГ015 довольно широка: средства измерений, связи, наблюдения, безопасности, автоматизация производства, энергетики, промышленности, различных систем, работающих от батарейного питания.

В состав микросхемы К1921ВГ015 входят: блоки АЦП сигма-дельта, АЦП последовательного приближения с интерфейсом к контроллеру прямого доступа к памяти, модуль захвата/сравнения, блоки кодирования информации, блок RTC, два блока ОЗУ на 256 кБ и 64 кБ, блок контроля вскрытия и др.

Микроконтроллер содержит домен батарейного питания, в который входят периферийные блоки: RTC, аналоговые компараторы, блок контроля вскрытия, дополнительное ОЗУ 64 КБ, независимый сторожевой таймер. Периферийные блоки, входящие в состав домена батарейного питания, позволяют осуществлять контроль вскрытия корпуса системы, отсчитывать временные промежутки и сохранять информацию при отсутствии основного питания.

Разработанный микроконтроллер имеет встроенную Flash-память программ объемом 1 Мбайт, которую можно использовать для хранения и загрузки пользовательского программного обеспечения.

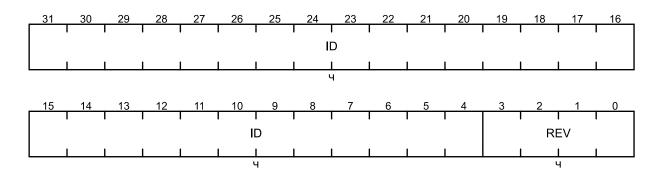

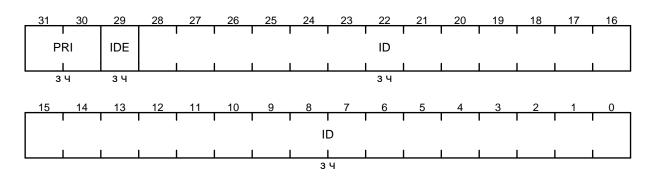

Каждый микроконтроллер содержит уникальный идентификационный номер ID, состоящий из 128 бит.

Система тактирования микроконтроллера позволяет использовать различные источники тактового сигнала, что позволяет расширить набор применений и решаемых задач пользователя. Существует возможность гибкой настройки тактовых сигналов для блоков периферии.

Для снижения энергопотребления микросхемы предусмотрена возможность отключения тактовых сигналов отдельных блоков периферии в случае, если они не используются пользователем. При переходе процессора в режим пониженного энергопотребления возможно отключение тактового сигнала ядра (команда WFI), а также возможность выбора периферийных блоков, которые будут отключены/включены при переходе/выходе из данного режима.

## 2 Краткое техническое описание микроконтроллера

## 2.1 Функциональные параметры

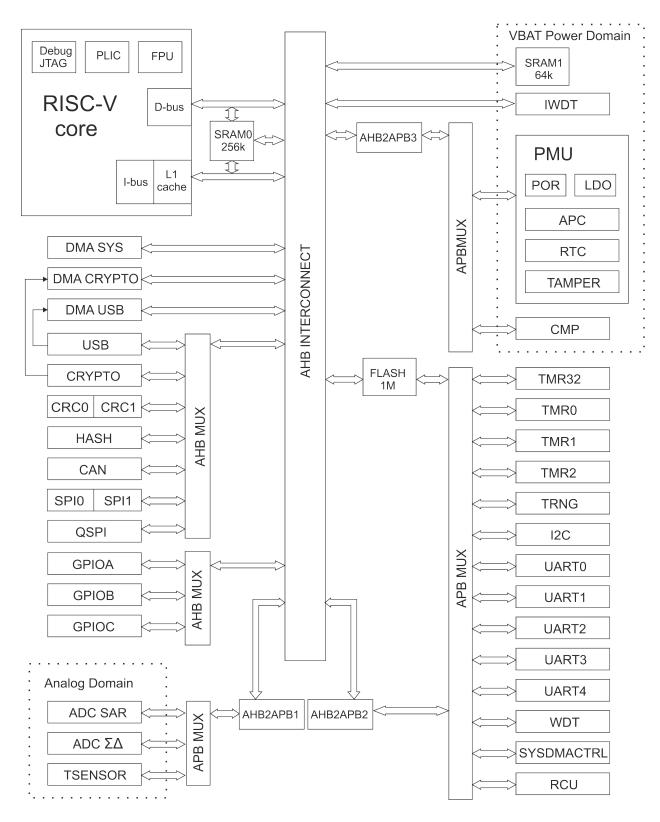

Структурная схема микроконтроллера показана на рисунке 2.1.

Рисунок 2.1 – Структурная схема микроконтроллера

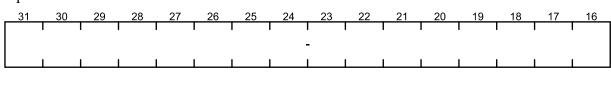

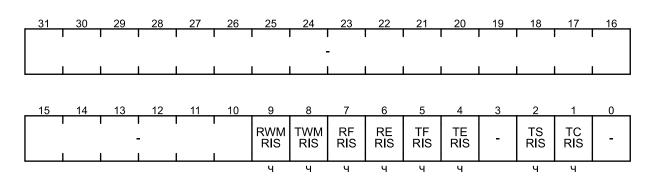

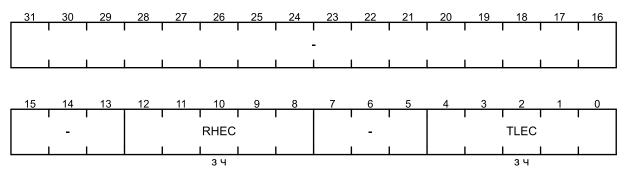

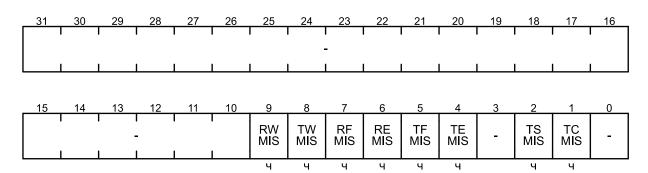

В состав микроконтроллера входят функциональные элементы:

- 32-разрядное ядро архитектуры RISC-V с поддержкой системы команд RV32IMFCN\_ZBA\_ZBB\_ZBC\_ZBS, набора команд умножения, арифметических и логических команд, встроенным модулем обработки команд с плавающей запятой с одинарной точностью FPU, кэшем команд и поддержкой отладочного интерфейса JTAG;

- блок управления сбросом и синхронизацией RCU, имеющий в своем составе RC-генератор (1 МГц), синтезатор частоты SYSPLL и блок управления системными тактовыми сигналами SCM;

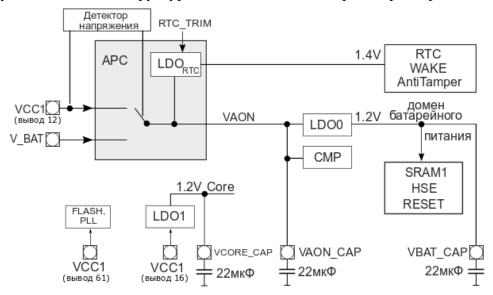

- системный блок управления энергопотреблением PMUSYS;

- блок управления энергопотреблением в составе с RTC модулем (PMURTC);

- блок коммутации AXI AHB;

- основная Flash-память объемом 1 Мбайт;

- SRAM0 (ОЗУ0) объемом 256 Кбайт;

- SRAM1 (ОЗУ1), подключенное к домену батарейного питания, объемом 64 Кбайт;

- 24-канальный контроллер прямого доступа к памяти DMA;

- блок часов реального времени RTC со входами контроля целостности;

- датчик температуры TSENSOR;

- сторожевой таймер WDT;

- независимый сторожевой таймер IWDT;

- один 8-канальный 12-разрядный быстродействующий АЦП с режимами цифрового компаратора для каждого из каналов (ADCSAR);

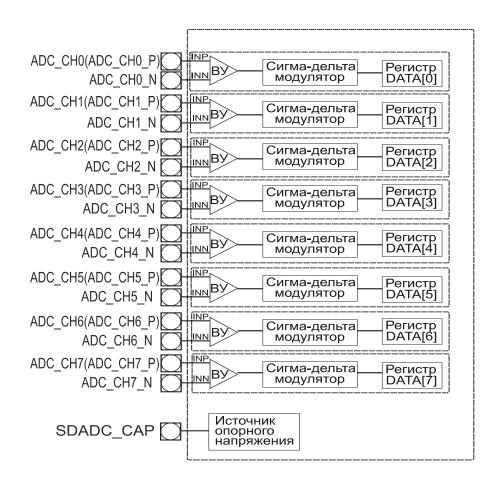

- один 8-канальный (16-канальный в бескорпусном исполнении) 16-разрядный сигмадельта АШП (ADCSD);

- три 16-разрядных порта ввода-вывода А, В, С;

- восемь аналоговых входов, подключенных к каналам АЦП (ADCSD и ADCSAR);

- один 32-разрядный таймер TMR32;

- три 16-разрядных таймеров TMR0 TMR2;

- пять приемопередатчиков UART0 UART4;

- блок криптографии CRYPTO;

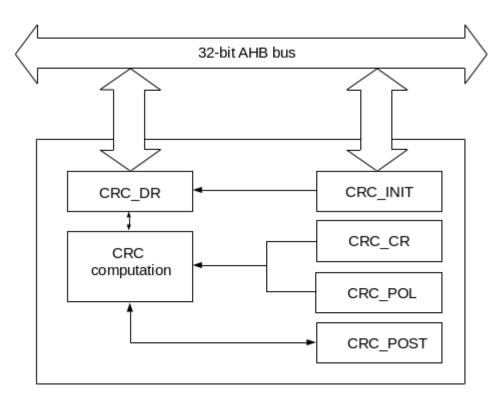

- два блока вычисления CRC (CRC0, CRC1);

- генератор случайных чисел (TRNG);

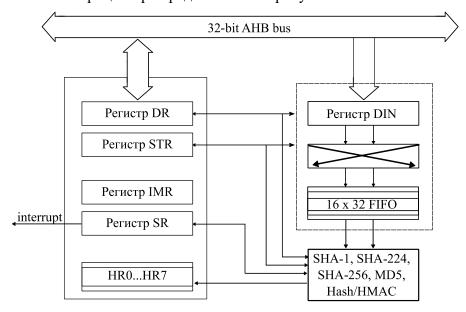

- HASH процессор;

- контроллеры интерфейсов:

- CAN 2.0b;

- USB 2.0 FullSpeed (Device);

- один контроллер I2C;

- один контроллер OSPI;

- два контроллера SPI (SPI0 SPI1).

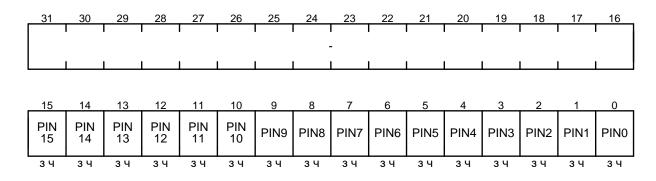

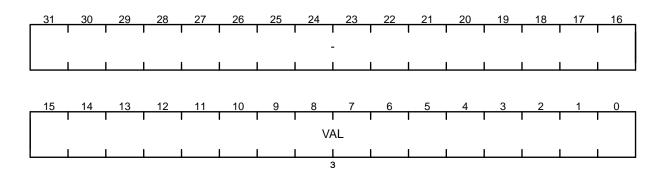

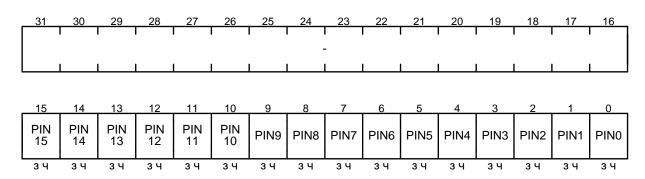

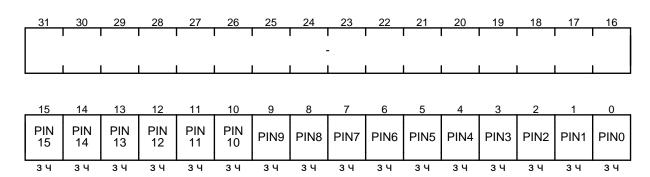

#### Особенности выводов микроконтроллера

Все выводы микроконтроллера по их функциональному назначению, организованы в группы:

- 16-разрядные порты ввода-вывода А, В, С;

- 8 аналоговых входов, подключаемых к каналам АЦП;

- порт тестирования JTAG;

- питание микроконтроллера;

- питание аналогового домена, включающего блоки:

- АЦП последовательного приближения (ADC);

- АЦП сигма-дельта (ADCSD);

- внутренний датчик температуры (TSENSOR), подключаемый к одному из входов АЦП;

- питание батарейного домена, включающего блоки:

- ОЗУ1;

- PMU;

- контроля вскрытия TAMPER;

- часов реального времени RTC;

- аналоговые компараторы (СМР0- СМР1);

- IWDT.

Каждый цифровой вывод порта микроконтроллера может использоваться как двунаправленный вывод общего назначения (режим GPIO). Помимо этого, все выводы имеют альтернативную функцию (или функции). Режим работы, альтернативная функция, нагрузочная способность и быстродействие, а также подтяжка к высокому уровню и функционирование в режиме выхода с открытым стоком/истоком могут быть заданы для каждого вывода независимо от других.

Примечание — После сброса микроконтроллера выводы портов ввода-вывода конфигурируются как выводы общего назначения и находятся в третьем состоянии.

Порт JTAG, предназначенный для внутрисхемного программирования микроконтроллера, тестирования и отладки программ пользователя, включает в свой состав пять выводов TCK, TMS, TDI, TDO, TRST для подключения JTAG эмулятора.

Выводы ADC\_CH0 – ADC\_CH7 (входные каналы АЦП), не подключенные к внешним источникам напряжения, находятся в плавающем состоянии.

Вывод RST является входом сигнала сброса микроконтроллера и должен находиться в состоянии логической единицы. Внешний сброс осуществляется подачей на вывод логического нуля в течение минимум 10 мкс.

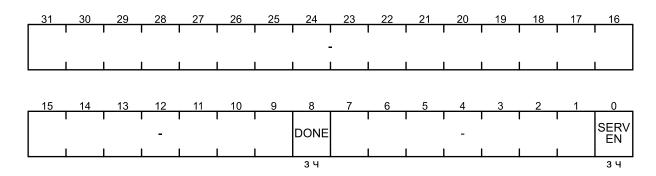

Микроконтроллер имеет конфигурационный вывод SERVEN. При подаче на SERVEN логической единицы во время сброса, микроконтроллер переходит в сервисный режим, в котором запрещаются любые операции со всей Flash-памятью, кроме полного стирания.

Выводы XI\_RTC и XO\_RTC предназначены для подключения внешнего источника тактового сигнала (с частотой 32 кГц) блока RTC.

Выводы XI\_OSC и XO\_OSC предназначены для подключения внешнего источника тактового сигнала микроконтроллера с частотой (2-30) М $\Gamma$ ц.

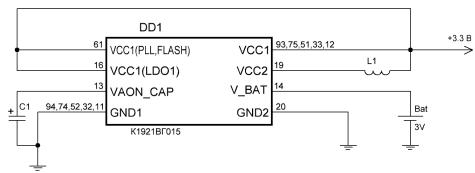

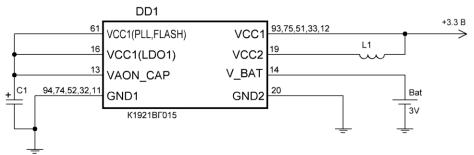

Вывод  $V_BAT$  предназначен для подключения внешнего источника питания (батарейки). Номинальное значение напряжения должно находиться в диапазоне от 1,7 до 3,6 В.

Выводы VCC1 и GND1 предназначены для подключения внешних источников питания ядра, Flash, PLL и периферии микроконтроллера. Номинальное значение напряжения должно находиться в диапазоне от 1,7 до 3,6 В. Максимальный ток потребления с учётом нагрузки по GPIOA, GPIOB, GPIOC - до 150 мА.

Вывод № 12 из группы выводов VCC1 предназначен для подключения входного напряжения APC.

Вывод № 16 из группы выводов VCC1 предназначен для подключения LDO1 питания ядра.

Вывод № 61 из группы выводов VCC1 предназначен для подключения питания Flash и PLL.

Выводы VCC2 и GND2 предназначены для подключения внешних источников питания АЦП и датчика температуры. Номинальное значение напряжения 3,3 В.

Вывод AREF предназначен для подключения внешнего источника опорного напряжения АЦП. Номинальное значение напряжения должно находиться в диапазоне от 1,2 до 3,3 В. Максимальный ток - до 0,1 мА.

Выводы VAON\_CAP, VCORE\_CAP, VBAT\_CAP предназначены для подключения внешних конденсаторов емкостью 22 мкФ. Конденсаторы, подключаемые к выводам VAON\_CAP, VCORE\_CAP, VBAT\_CAP вторым выводом подключаются к GND1.

Вывод SDADC\_CAP предназначен для подключения внешнего конденсатора емкостью 0,1 мкФ. Конденсатор, подключаемый к выводу SDADC\_CAP, вторым выводом подключается к GND2.

Примечание — На плате вывод питания GND1 может быть объединен с выводами питания GND2 (при этом должны быть приняты меры для снижения помех по питанию).

Выключение питания микроконтроллера подразумевает полное снятие напряжения как с выводов питания VCC1, VCC2, V\_BAT, AREF, так и со всех остальных выводов микроконтроллера.

Примечание — Запрещено подавать напряжение на функциональные выводы при выключенном питании микроконтроллера.

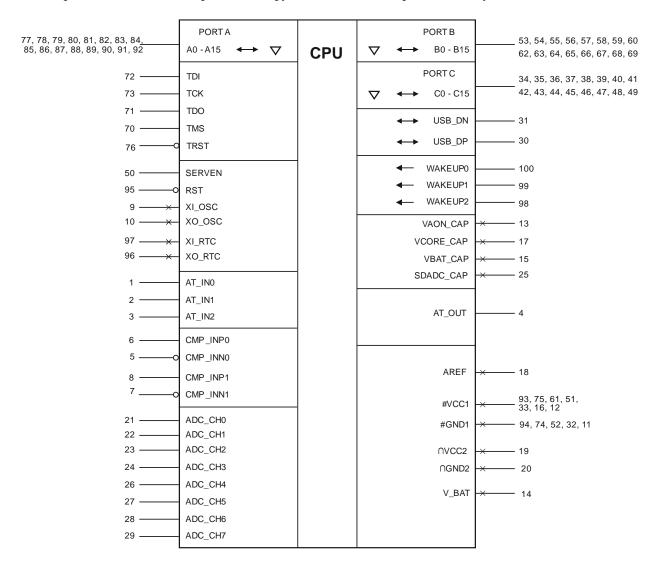

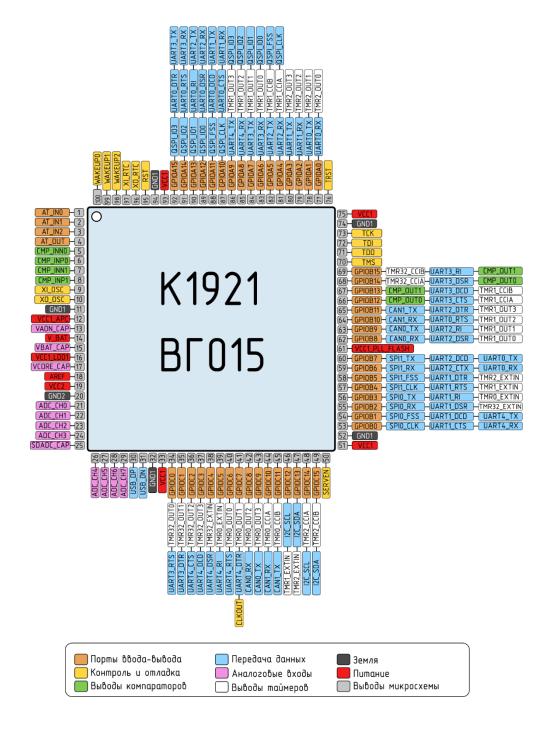

## УГО и назначение выводов микроконтроллера

Условное графическое обозначение микроконтроллера приведено на рисунке 2.2.

Функциональное назначение выводов микроконтроллера приведено в таблицах 2.1-2.3, в которых приняты обозначения: I- вход, O- выход, I/O- вход/выход, Z- третье состояние.

Примечание – Альтернативные функции выводов портов А, В, С указаны в таблице 2.1.

Рисунок 2.2 – Условное графическое обозначение микросхемы

Таблица 2.1 – Функциональное назначение выводов, имеющих альтернативные функции

| Обозна- | Обозначение    |        |        | ыводов, имеющих альтернативные функции |

|---------|----------------|--------|--------|----------------------------------------|

| чение   | альтернативной | Номер  | Тип    | Функциональное назначение вывода       |

| вывода  | функции вывода | вывода | вывода |                                        |

| 1       | 2              | 3      | 4      | 5                                      |

| A0      |                | 77     | I/O/Z  | Вход/выход порта А, разряд 0           |

|         | UART0_RX       |        | I      | Вход данных UART0                      |

|         | TMR2_OUT0      |        | О      | Выход TMR2                             |

|         |                |        |        |                                        |

| A1      |                | 78     | I/O/Z  | Вход/выход порта А, разряд 1           |

|         | UART0_TX       |        | О      | Выход данных UART0                     |

|         | TMR2_OUT1      |        | О      | Выход TMR2                             |

|         |                |        |        |                                        |

| A2      |                | 79     | I/O/Z  | Вход/выход порта А, разряд 2           |

|         | UART1_RX       |        | Ι      | Вход данных UART1                      |

|         | TMR2_OUT2      |        | О      | Выход TMR2                             |

|         |                |        |        |                                        |

| A3      |                | 80     | I/O/Z  | Вход/выход порта А, разряд 3           |

|         | UART1_TX       |        | О      | Выход данных UART1                     |

|         | TMR2_OUT3      |        | О      | Выход TMR2                             |

|         |                |        |        |                                        |

| A4      |                | 81     | I/O/Z  | Вход/выход порта А, разряд 4           |

|         | UART2_RX       |        | I      | Вход данных UART2                      |

|         | TMR1_CCIA      |        | I      | Вход захвата TMR1                      |

|         | QSPI_CLK       |        | I/O    | Вход/выход синхронизации QSPI          |

| A5      |                | 82     | I/O/Z  | Вход/выход порта А, разряд 5           |

|         | UART2_TX       |        | О      | Выход данных UART2                     |

|         | TMR1_CCIB      |        | I      | Вход захвата TMR1                      |

|         | QSPI_FSS       |        | I/O    | Вход/выход выбора устройства QSPI      |

| A6      |                | 83     | I/O/Z  | Вход/выход порта А, разряд 6           |

|         | UART3_RX       |        | I      | Вход данных UART3                      |

|         | TMR1_OUT0      |        | О      | Выход TMR1                             |

|         | QSPI_IO0       |        | I/O    | Вход/выход данных QSPI, разряд 0       |

| A7      |                | 84     | I/O/Z  | Вход/выход порта А, разряд 7           |

|         | UART3_TX       |        | О      | Выход данных UART3                     |

|         | TMR1_OUT1      |        | 0      | Выход ТМК1                             |

|         | QSPI_IO1       |        | I/O    | Вход/выход данных QSPI, разряд 1       |

| A8      | ****           | 85     | I/O/Z  | Вход/выход порта А, разряд 8           |

|         | UART4_RX       |        | I      | Вход данных UART4                      |

|         | TMR1_OUT2      |        | 0      | Bыход TMR1                             |

|         | QSPI_IO2       |        | I/O    | Вход/выход данных QSPI, разряд 2       |

| A9      | TIADE ( EX.    | 86     | I/O/Z  | Вход/выход порта А, разряд 9           |

|         | UART4_TX       |        | 0      | Выход данных UART4                     |

|         | TMR1_OUT3      |        | 0      | Buxog TMR1                             |

| 110     | QSPI_IO3       | 0.7    | I/O    | Вход/выход данных QSPI, разряд 3       |

| A10     | OGDI GLI       | 87     | I/O/Z  | Вход/выход порта А, разряд 10          |

|         | QSPI_CLK       |        | I/O    | Вход/выход синхронизации QSPI          |

|         | UART0_CTS      |        | I      | Вход сигнала готовности к приему UART0 |

|         | 1              |        | I      | 0111110                                |

| Продолэ<br>1 | кение таблицы 2.1 | 2   | 1 4   | T ==================================== |

|--------------|-------------------|-----|-------|----------------------------------------|

| 1            | 2                 | 3   | 4     | 5                                      |

| A11          |                   | 88  | I/O/Z | Вход/выход порта А, разряд 11          |

|              | QSPI_FSS          |     | I/O   | Вход/выход выбора устройства QSPI      |

|              | UART0_DCD         |     | I     | Вход отклика при обнаружении           |

|              |                   |     |       | информационного сигнала UART0          |

|              | UART1_TX          |     | O     | Выход данных UART1                     |

| A12          |                   | 89  | I/O/Z | Вход/выход порта А, разряд 12          |

|              | QSPI_IO0          |     | I/O   | Вход/выход данных QSPI, разряд 0       |

|              | UART0_DSR         |     | I     | Вход сигнала готовности источника      |

|              |                   |     |       | данных UART0                           |

|              | UART2_RX          |     | I     | Вход данных UART2                      |

| A13          |                   | 90  | I/O/Z | Вход/выход порта А, разряд 13          |

|              | QSPI_IO1          |     | I/O   | Вход/выход данных QSPI, разряд 1       |

|              | UART0_RI          |     | I     | Вход сигнала-индикатора вызова         |

|              |                   |     |       | UART0                                  |

|              | UART2_TX          |     | O     | Выход данных UART2                     |

| A14          |                   | 91  | I/O/Z | Вход/выход порта А, разряд 14          |

|              | QSPI_IO2          |     | I/O   | Вход/выход данных QSPI, разряд 2       |

|              | UART0_RTS         |     | О     | Выход сигнала запроса на передачу      |

|              |                   |     |       | UART0                                  |

|              | UART3_RX          |     | I     | Вход данных UART3                      |

| A15          |                   | 92  | I/O/Z | Вход/выход порта А, разряд 15          |

|              | QSPI_IO3          |     | I/O   | Вход/выход данных QSPI, разряд 3       |

|              | UART0_DTR         |     | O     | Выход сигнала готовности приемника     |

|              | _                 |     |       | данных UART0                           |

|              | UART3_TX          |     | O     | Выход данных UART3                     |

| В0           | _                 | 53  | I/O/Z | Вход/выход порта В, разряд 0           |

|              | SPI0_CLK          |     | I/O   | Вход/выход синхронизации SPI0          |

|              | UART1_CTS         |     | I     | Вход сигнала готовности к приему       |

|              | _                 |     |       | UART1                                  |

|              | UART4_RX          |     | I     | Вход данных UART4                      |

| B1           | _                 | 54  | I/O/Z | Вход/выход порта В, разряд 1           |

|              | SPI0 FSS          |     | I/O   | Вход/выход выбора устройства SPI0      |

|              | UART1_DCD         |     | I     | Вход отклика при обнаружении           |

|              | _                 |     |       | информационного сигнала UART1          |

|              | UART4_TX          |     | O     | Выход данных UART4                     |

| B2           | _                 | 55  | I/O/Z | Вход/выход порта В, разряд 2           |

|              | SPIO_RX           | -   | I     | Вход данных SPI0                       |

|              | UART1_DSR         |     | I     | Вход сигнала готовности источника      |

|              | ~ = .             |     |       | данных UART1                           |

|              | TMR32_EXTIN       |     | I     | Вход синхронизации TMR32               |

| В3           |                   | 56  | I/O/Z | Вход/выход порта В, разряд 3           |

|              | SPIO_TX           | 2.0 | O     | Выход данных SPI0                      |

|              | UART1_RI          |     | I     | Вход сигнала-индикатора вызова         |

|              | 0/11(1/1_1(1      |     | 1     | UART1                                  |

|              | TMR0_EXTIN        |     | I     | Вход синхронизации ТМR0                |

|              | 1111110_L/X11111  |     | 1     | 1 Drog emirpoinisagin Time             |

| SPI1_CLK UART1_RTS TMR1_EXTIN  SPI1_FSS UART1_DTR | 3<br>57<br>58                                                                                                                                                                                       | 4<br>  I/O/Z<br>  I/O<br>  O<br>  I<br>  I/O/Z                                                                                                                                                                         | 5 Вход/выход порта В, разряд 4 Вход/выход синхронизации SPI1 Выход сигнала запроса на передачу UART1 Вход синхронизации TMR1 |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| UART1_RTS  TMR1_EXTIN  SPI1_FSS UART1_DTR         |                                                                                                                                                                                                     | I/O<br>O                                                                                                                                                                                                               | Вход/выход синхронизации SPI1 Выход сигнала запроса на передачу UART1                                                        |

| UART1_RTS  TMR1_EXTIN  SPI1_FSS UART1_DTR         | 58                                                                                                                                                                                                  | O<br>I                                                                                                                                                                                                                 | Выход сигнала запроса на передачу<br>UART1                                                                                   |

| TMR1_EXTIN  SPI1_FSS UART1_DTR                    | 58                                                                                                                                                                                                  | I                                                                                                                                                                                                                      | UART1                                                                                                                        |

| SPI1_FSS<br>UART1_DTR                             | 58                                                                                                                                                                                                  |                                                                                                                                                                                                                        |                                                                                                                              |

| SPI1_FSS<br>UART1_DTR                             | 58                                                                                                                                                                                                  |                                                                                                                                                                                                                        | I RYOTI CHIIVIOIIII POITIII I INIP I                                                                                         |

| UART1_DTR                                         | 58                                                                                                                                                                                                  |                                                                                                                                                                                                                        |                                                                                                                              |

| UART1_DTR                                         |                                                                                                                                                                                                     | I/O/Z                                                                                                                                                                                                                  | Вход/выход порта В, разряд 5                                                                                                 |

|                                                   |                                                                                                                                                                                                     | I/O                                                                                                                                                                                                                    | Вход/выход выбора устройства SPI1                                                                                            |

| TMDA EXTENT                                       |                                                                                                                                                                                                     | О                                                                                                                                                                                                                      | Выход сигнала готовности приемника данных UART1                                                                              |

| TMR2_EXTIN                                        |                                                                                                                                                                                                     | I                                                                                                                                                                                                                      | Вход синхронизации TMR2                                                                                                      |

|                                                   | 59                                                                                                                                                                                                  | I/O/Z                                                                                                                                                                                                                  | Вход/выход порта В, разряд 6                                                                                                 |

| SPI1_RX                                           |                                                                                                                                                                                                     | I                                                                                                                                                                                                                      | Вход данных SPI1                                                                                                             |

| UART2_CTS                                         |                                                                                                                                                                                                     | Ι                                                                                                                                                                                                                      | Вход сигнала готовности к приему<br>UART2                                                                                    |

| UARTO RX                                          |                                                                                                                                                                                                     | Ī                                                                                                                                                                                                                      | Вход данных UART0                                                                                                            |

| 012210_101                                        | 60                                                                                                                                                                                                  |                                                                                                                                                                                                                        | Вход/выход порта В, разряд 7                                                                                                 |

| SPI1 TX                                           |                                                                                                                                                                                                     | -                                                                                                                                                                                                                      | Выход данных SPI1                                                                                                            |

|                                                   |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | Вход отклика при обнаружении                                                                                                 |

| 072772_5 05                                       |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | информационного сигнала UART2                                                                                                |

| UARTO TX                                          |                                                                                                                                                                                                     | O                                                                                                                                                                                                                      | Выход данных UART0                                                                                                           |

|                                                   | 62                                                                                                                                                                                                  | I/O/Z                                                                                                                                                                                                                  | Вход/выход порта В, разряд 8                                                                                                 |

| CANO RX                                           |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | Вход данных CAN0                                                                                                             |

|                                                   |                                                                                                                                                                                                     | I                                                                                                                                                                                                                      | Вход сигнала готовности источника                                                                                            |

| _                                                 |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | данных UART2                                                                                                                 |

| TMR1_OUT0                                         |                                                                                                                                                                                                     | O                                                                                                                                                                                                                      | Выход TMR1                                                                                                                   |

|                                                   | 63                                                                                                                                                                                                  | I/O/Z                                                                                                                                                                                                                  | Вход/выход порта В, разряд 9                                                                                                 |

| CAN0_TX                                           |                                                                                                                                                                                                     | О                                                                                                                                                                                                                      | Выход данных CAN0                                                                                                            |

| UART2_RI                                          |                                                                                                                                                                                                     | I                                                                                                                                                                                                                      | Вход сигнала-индикатора вызова UART2                                                                                         |

| TMR1_OUT1                                         |                                                                                                                                                                                                     | O                                                                                                                                                                                                                      | Выход TMR1                                                                                                                   |

|                                                   | 64                                                                                                                                                                                                  | I/O/Z                                                                                                                                                                                                                  | Вход/выход порта В, разряд 10                                                                                                |

| CAN1_RX                                           |                                                                                                                                                                                                     | I                                                                                                                                                                                                                      | Вход данных CAN1                                                                                                             |

| UART2_RTS                                         |                                                                                                                                                                                                     | О                                                                                                                                                                                                                      | Выход сигнала запроса на передачу UART2                                                                                      |

| TMR1 OUT2                                         |                                                                                                                                                                                                     | 0                                                                                                                                                                                                                      | Выход TMR1                                                                                                                   |

|                                                   | 65                                                                                                                                                                                                  | _                                                                                                                                                                                                                      | Вход/выход порта В, разряд 11                                                                                                |

| CAN1 TX                                           |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | Выход данных САМ1                                                                                                            |

|                                                   |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | Выход сигнала готовности приемника                                                                                           |

|                                                   |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | данных UART2                                                                                                                 |

| TMR1 OUT3                                         |                                                                                                                                                                                                     | O                                                                                                                                                                                                                      | Выход TMR1                                                                                                                   |

| _                                                 | 66                                                                                                                                                                                                  | I/O/Z                                                                                                                                                                                                                  | Вход/выход порта В, разряд 12                                                                                                |

| CMP OUT0                                          |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | Выход компаратора, нулевой канал                                                                                             |

| UART3_CTS                                         |                                                                                                                                                                                                     | I                                                                                                                                                                                                                      | Вход сигнала готовности к приему<br>UART3                                                                                    |

| TMR1 CCIA                                         |                                                                                                                                                                                                     | T                                                                                                                                                                                                                      | Вход захвата ТМR1                                                                                                            |

| 1 WIN1_CCIA                                       | 67                                                                                                                                                                                                  |                                                                                                                                                                                                                        | Вход/выход порта В, разряд 13                                                                                                |

| CMP OUT1                                          | 07                                                                                                                                                                                                  |                                                                                                                                                                                                                        | Выход компаратора, первый канал                                                                                              |

|                                                   |                                                                                                                                                                                                     |                                                                                                                                                                                                                        | Вход компаратора, первый канал Вход отклика при обнаружении                                                                  |

| UAK13_DCD                                         |                                                                                                                                                                                                     | 1                                                                                                                                                                                                                      | информационного сигнала UART3                                                                                                |

| TMR1_CCIB                                         |                                                                                                                                                                                                     | I                                                                                                                                                                                                                      | информационного сигнала UAR13  Вход захвата TMR1                                                                             |

|                                                   | UARTO_RX  SPI1_TX UART2_DCD  UART0_TX  CAN0_RX UART2_DSR  TMR1_OUT0  CAN0_TX UART2_RI TMR1_OUT1  CAN1_RX UART2_RTS  TMR1_OUT2  CAN1_TX UART2_DTR  TMR1_OUT2  CAN1_TX UART2_DTR  TMR1_OUT3  CMP_OUT0 | UART0_RX  SPI1_TX UART2_DCD  UART0_TX  CAN0_RX UART2_DSR  TMR1_OUT0  CAN0_TX UART2_RI TMR1_OUT1  CAN1_RX UART2_RTS  TMR1_OUT2  CAN1_TX UART2_DTR  TMR1_OUT3  CMP_OUT0 UART3_CTS  TMR1_CCIA  CMP_OUT1  60  67  CMP_OUT1 | UART0_RX                                                                                                                     |

| <u>Продола</u> | жение таблицы 2.1 | 2  | 1     |                                            |

|----------------|-------------------|----|-------|--------------------------------------------|

| <u>l</u>       | 2                 | 3  | 4     | 5                                          |

| B14            | Th AD 22 CCLA     | 68 | I/O/Z | Вход/выход порта В, разряд 14              |

|                | TMR32_CCIA        |    | I     | Вход захвата ТMR32                         |

|                | UART3_DSR         |    | I     | Вход сигнала готовности источника          |

|                | CMD OLITTO        |    |       | данных UART3                               |

| D15            | CMP_OUT0          |    | 0     | Выход компаратора, нулевой канал           |

| B15            |                   | 69 | I/O/Z | Вход/выход порта В, разряд 15              |

|                | TMR32_CCIB        |    | I     | Вход захвата ТМR32                         |

|                | UART3_RI          |    | I     | Вход сигнала-индикатора вызова UART3       |

|                | CMP_OUT1          |    | 0     | Выход компаратора, первый канал            |

| C0             |                   | 34 | I/O/Z | Вход/выход порта С, разряд 0               |

|                | TMR32_OUT0        |    | 0     | Выход TMR32                                |

|                | UART3_RTS         |    | O     | Выход сигнала запроса на передачу          |

|                |                   |    |       | UART3                                      |

|                |                   |    |       |                                            |

| C1             |                   | 35 | I/O/Z | Вход/выход порта С, разряд 1               |

|                | TMR32_OUT1        |    | O     | Выход TMR32                                |

|                | UART3_DTR         |    | O     | Выход сигнала готовности приемника         |

|                |                   |    |       | данных UART3                               |

|                |                   |    |       |                                            |

| C2             |                   | 36 | I/O/Z | Вход/выход порта С, разряд 2               |

|                | TMR32_OUT2        |    | O     | Выход TMR32                                |

|                | UART4_CTS         |    | I     | Вход сигнала готовности к приему           |

|                |                   |    |       | UART4                                      |

|                |                   |    |       |                                            |

| C3             |                   | 37 | I/O/Z | Вход/выход порта С, разряд 3               |

|                | TMR32_OUT3        |    | O     | Выход ТМК32                                |

|                | UART4_DCD         |    | I     | Вход отклика при обнаружении               |

|                |                   |    |       | информационного сигнала UART4              |

| <u>C4</u>      |                   | 20 | 1/0/7 | D / C 4                                    |

| C4             | TMD22 EXTIN       | 38 | I/O/Z | Вход/выход порта С, разряд 4               |

|                | TMR32_EXTIN       |    | I     | Вход синхронизации TMR32                   |

|                | UART4_DSR         |    | I     | Вход сигнала готовности источника          |

|                |                   |    |       | данных UART4                               |

| C5             |                   | 39 | I/O/Z | Dyou/privou nonza C noona 5                |

| CS             | TMD0 EVTIN        | 39 | _     | Вход/выход порта С, разряд 5               |

|                | TMR0_EXTIN        |    | I     | Вход синхронизации ТМR0                    |

|                | UART4_RI          |    | 1     | Вход сигнала-индикатора вызова UART4       |

| C6             |                   | 40 | 1/0/7 | Dvot/privot Homzo C mongar 6               |

| Co             | TMD0 OUT0         | 40 | I/O/Z | Вход/выход порта С, разряд 6               |

|                | TMR0_OUT0         |    | 0     | Выход ТМКО                                 |

|                | UART4_RTS         |    |       | Выход сигнала запроса на передачу<br>UART4 |

| C7             |                   | 41 | I/O/Z |                                            |

| C/             | TMD0 OUT1         | 41 |       | Вход/выход порта С, разряд 7               |

|                | TMR0_OUT1         |    | 0     | Выход ТМКО                                 |

|                | UART4_DTR         |    | О     | Выход сигнала готовности приемника         |

|                | CLVOUT            |    | 0     | данных UART4                               |

|                | CLKOUT            |    | О     | Выход тактового сигнала CLKOUT             |

| 1       | 2          | 3              | 4     | 5                             |

|---------|------------|----------------|-------|-------------------------------|

|         |            |                | I/O/Z | Вход/выход порта С, разряд 8  |

| C0      | TMR0_OUT2  | 42             | О     | Выход TMR0                    |

| C8      | CAN0_RX    | 42             | I     | Вход данных CAN0              |

| <u></u> |            | 42             | 1/0/7 |                               |

| C9      | TO COLUMN  | 43             | I/O/Z | Вход/выход порта С, разряд 9  |

|         | TMR0_OUT3  |                | 0     | Выход ТМКО                    |

|         | CAN0_TX    |                | О     | Выход данных CAN0             |

| C10     |            | 44             | I/O/Z | Вход/выход порта С, разряд 10 |

|         | TMR0_CCIA  |                | I     | Вход захвата TMR0             |

|         | CAN1_RX    |                | I     | Вход данных САМ1              |

|         |            |                |       |                               |

| C11     |            | 45             | I/O/Z | Вход/выход порта С, разряд 11 |

|         | TMR0_CCIB  |                | I     | Вход захвата TMR0             |

|         | CAN1_TX    |                | О     | Выход данных CAN1             |

| C12     |            | 46             | I/O/Z | Вход/выход порта С, разряд 12 |

|         | I2C_SCL    |                | I/O   | Вход/выход синхронизации I2С  |

|         | TMR1_EXTIN |                | I     | Вход синхронизации ТМК1       |

| C12     |            | 47             | 1/0/7 | P                             |

| C13     | IOC CDA    | 47             | I/O/Z | Вход/выход порта С, разряд 13 |

|         | I2C_SDA    |                | I/O   | Вход/выход данных I2С         |

|         | TMR2_EXTIN |                | I     | Вход синхронизации ТМR2       |

| C14     |            | 48             | I/O/Z | Вход/выход порта С, разряд 14 |

|         | TMR2_CCIA  |                | I     | Вход захвата TMR2             |

|         | I2C_SCL    |                | I/O   | Вход/выход синхронизации I2С  |

| C15     |            | 49             | I/O/Z | Вход/выход порта С, разряд 15 |

| C13     | TMR2_CCIB  | <del>1</del> 7 | I     | Вход захвата ТМК2             |

|         | I2C_SDA    |                | I/O   | Вход/выход данных I2С         |

|         |            |                | 1, 5  | Zieg build guillia inc        |

Примечание — В графе «Тип вывода» принятые условные обозначения:

- I вход,

- O выход,

- Z третье состояние.

Таблица 2.2 – Функциональное назначение выводов, не имеющих альтернативных функций

| Обозначение<br>вывода | Номер<br>вывода | Тип<br>вывода | Функциональное назначение вывода                                              |

|-----------------------|-----------------|---------------|-------------------------------------------------------------------------------|

| 1                     | 2               | 3             | 4                                                                             |

| XI_OSC                | 9               | _             | Вывод внешнего тактового сигнала/ Вывод для подключения кварцевого резонатора |

| XO_OSC                | 10              | _             | Вывод для подключения кварцевого резонатора                                   |

16

| Продолжение т | аблицы 2.2 |              |                                               |

|---------------|------------|--------------|-----------------------------------------------|

| 1             | 2          | 3            | 4                                             |

| RST           | 95         | I            | Вход сигнала сброса                           |

| TCK           | 73         | I            | Вход тактового сигнала порта JTAG (Pull-down) |

| TDI           | 72         | I            | Вход данных порта JTAG (Pull-up)              |

| TDO           | 71         | О            | Выход данных порта JTAG                       |

| TMS           | 70         | Ι            | Вход режима порта JTAG (Pull-up)              |

| TRST          | 76         | Ι            | Вход сброса порта JTAG (Pull-up)              |

| SERVEN        | 50         | I            | Вход сигнала активации сервисного режима      |

|               |            |              | (Pull-down)                                   |

| XI_RTC        | 97         | _            | Вывод для подключения кварцевого резонатора   |

| 111_1110      | ,          |              | (32 кГц)                                      |

| XO_RTC        | 96         | _            | Вывод для подключения кварцевого резонатора   |

| 110_1110      | 70         |              | (32 кГц)                                      |

| USB DN        | 31         | I/O          | Вход/выход «USB Dn»                           |

| USB_DP        | 30         | I/O          | Вход/выход «USB Dp»                           |

| CMP INP0      | 6          | I            | Прямой вход компаратора, канал 0              |

| CMP_INN0      | 5          | I            | Инверсный вход компаратора, канал 0           |

| CMP_INP1      | 8          | I            | 1 1                                           |

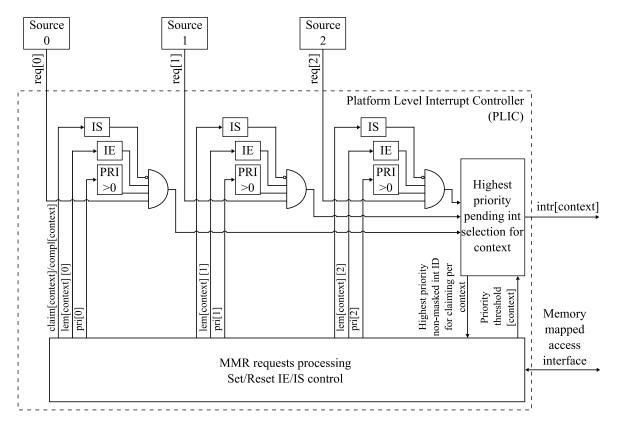

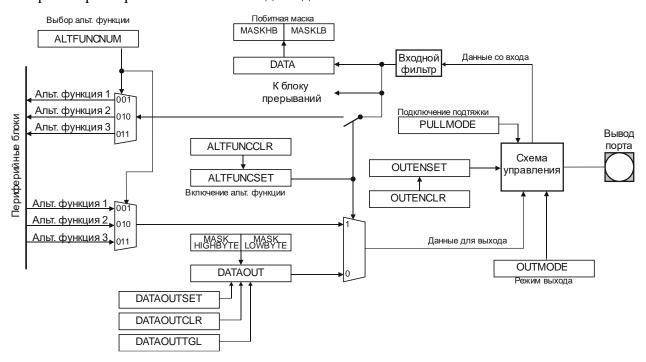

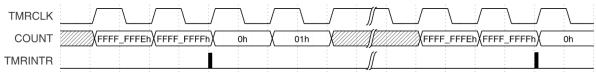

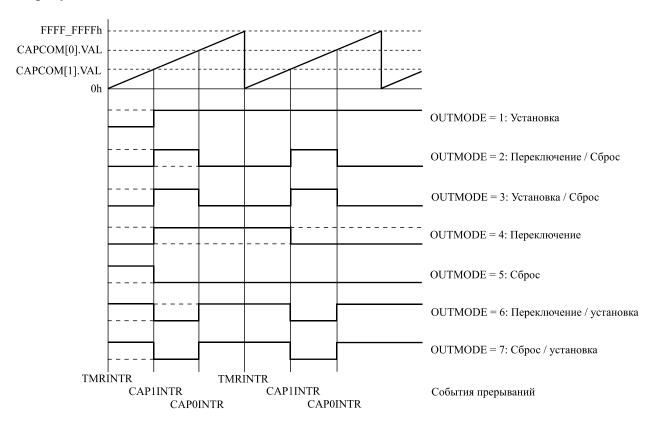

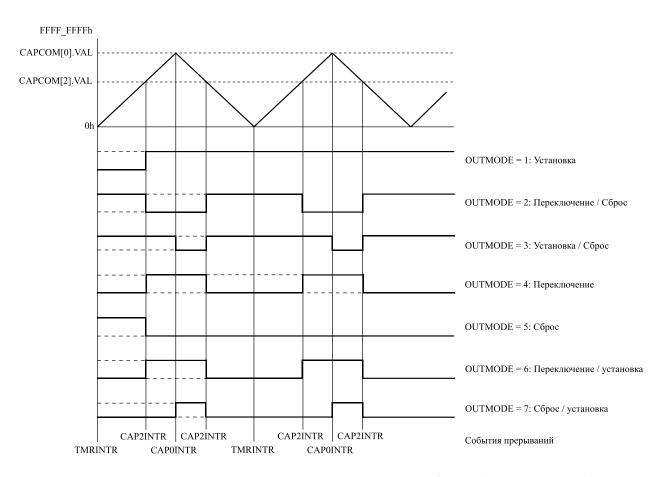

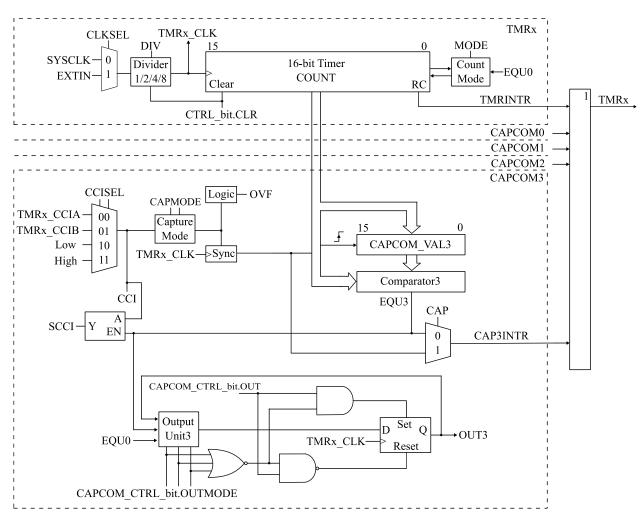

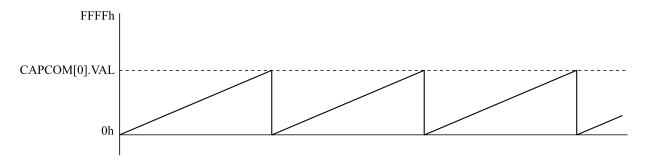

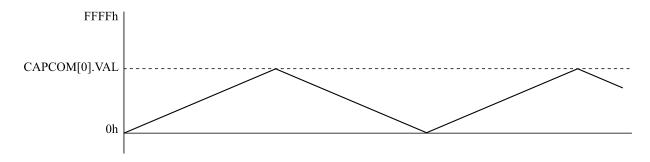

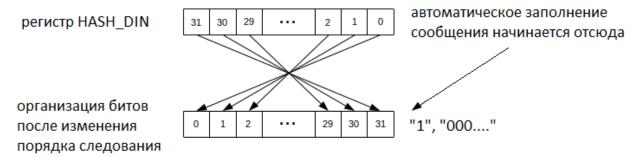

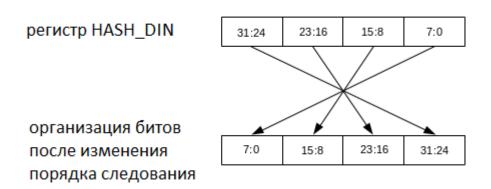

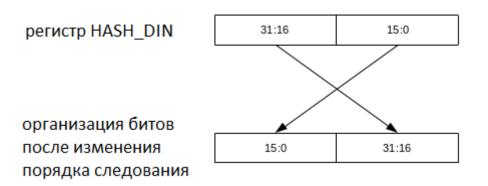

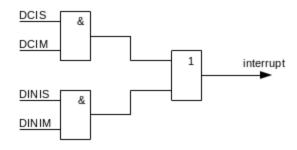

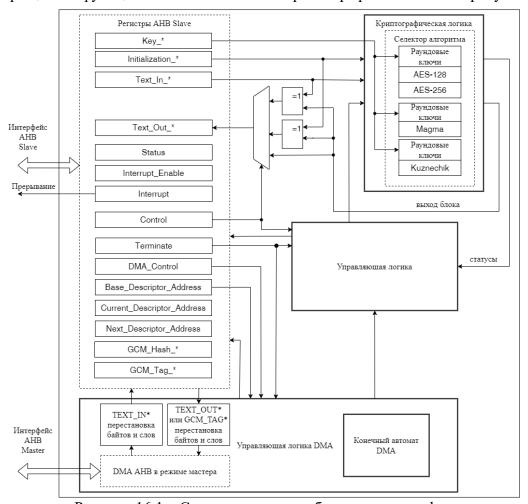

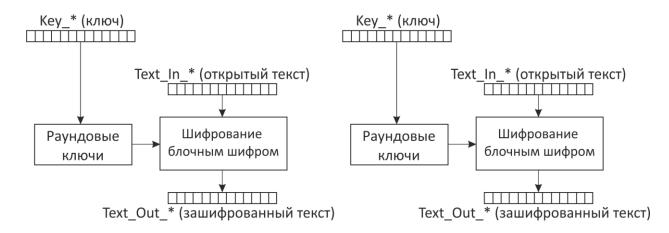

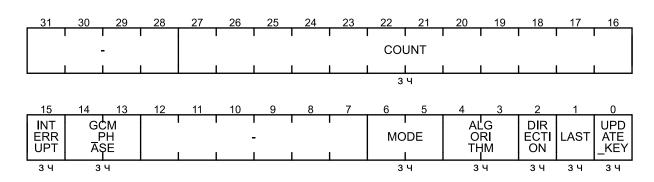

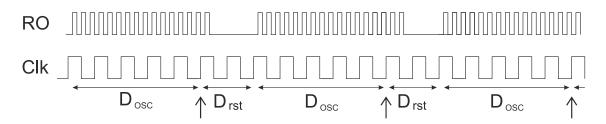

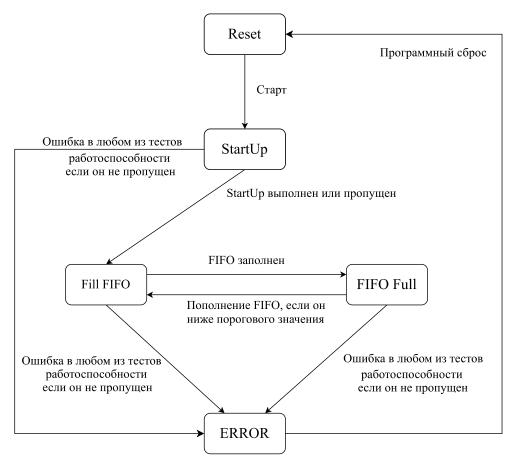

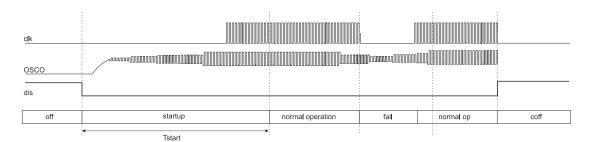

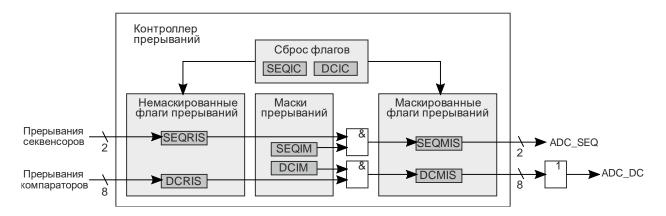

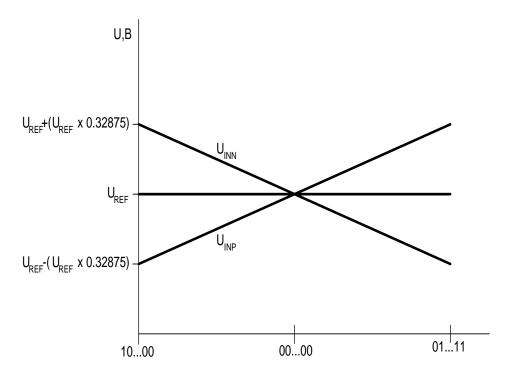

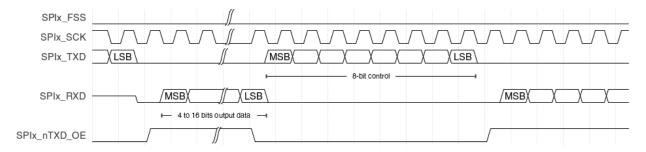

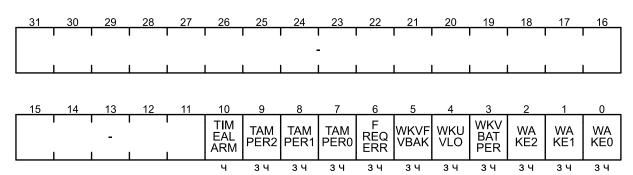

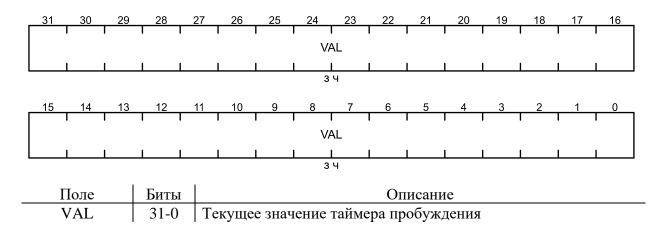

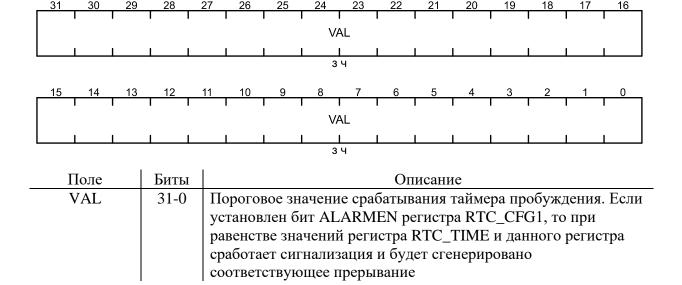

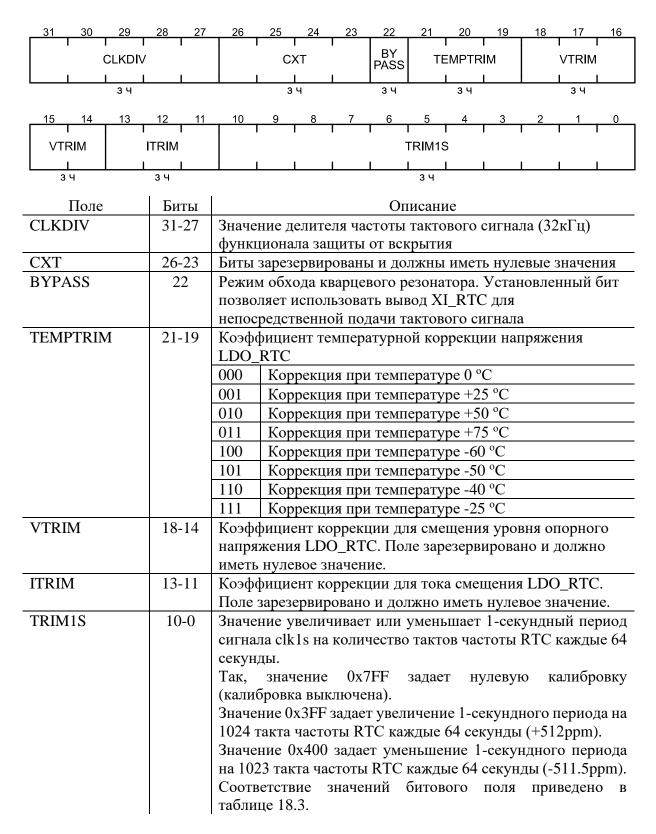

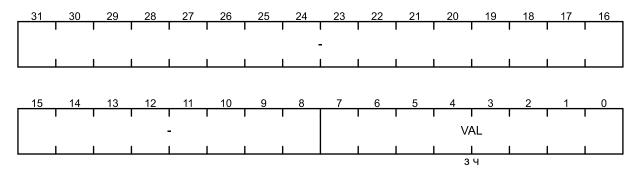

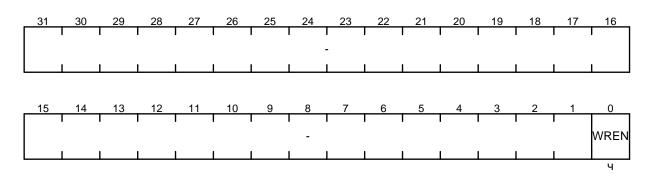

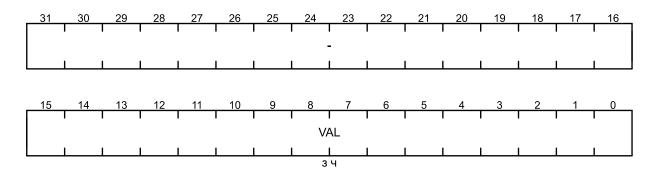

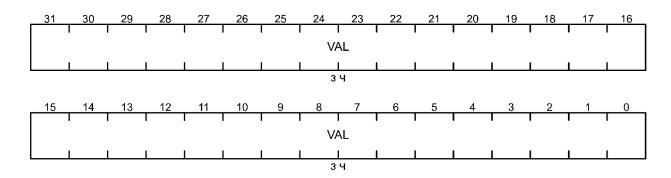

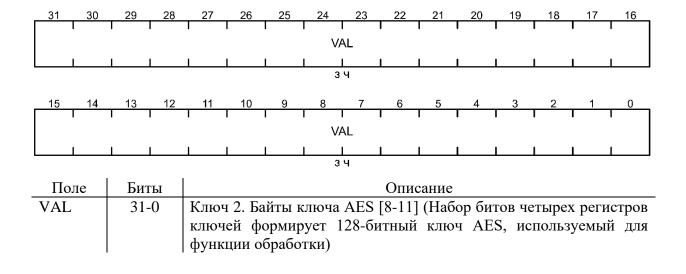

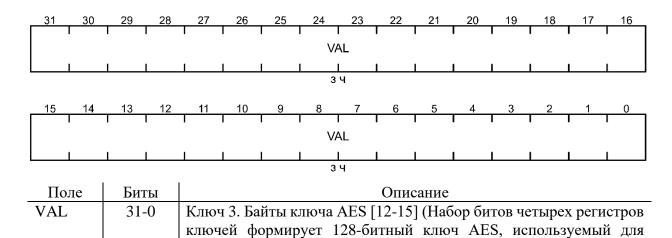

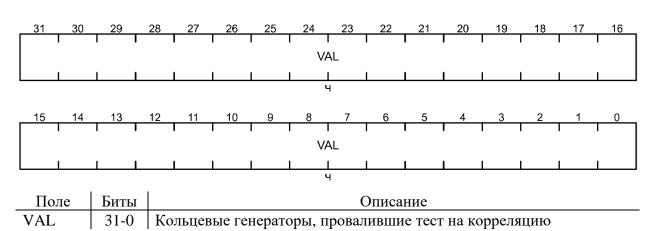

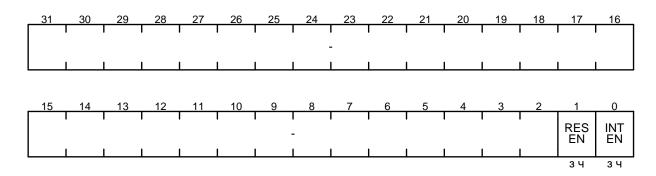

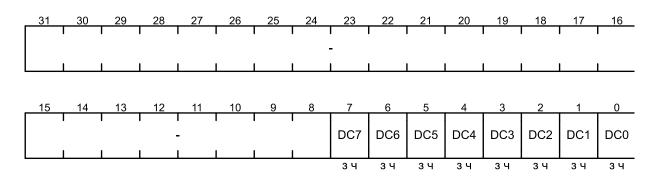

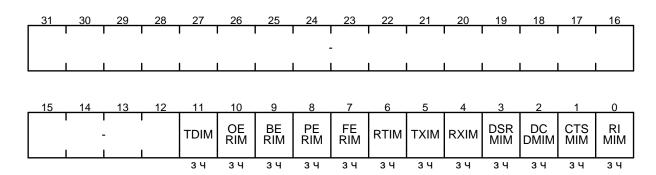

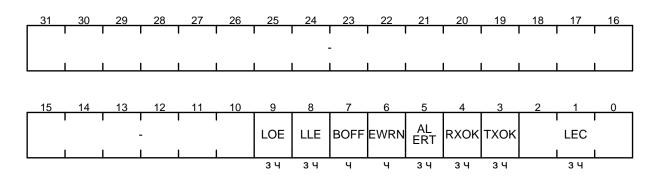

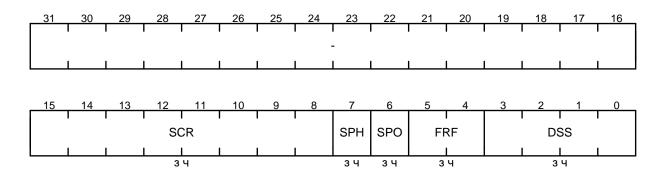

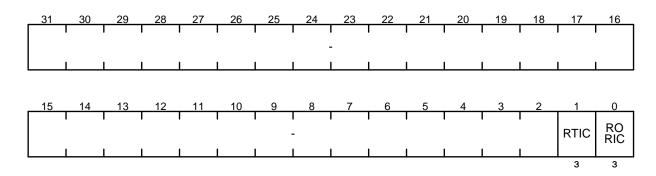

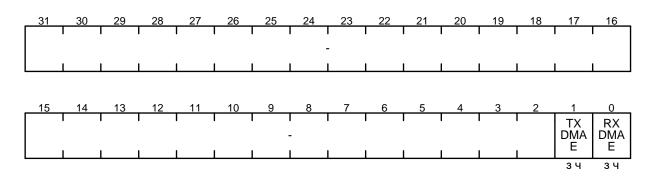

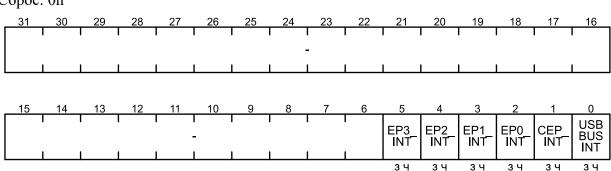

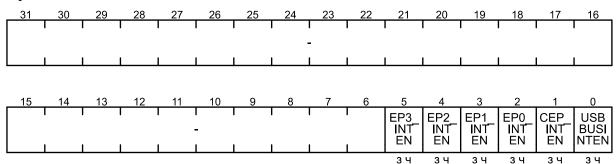

| _             | 7          |              | Прямой вход компаратора, канал 1              |