## МИКРОСХЕМЫ ИНТЕГРАЛЬНЫЕ 1273HA084

Руководство пользователя

## Содержание

| 1   | Введение                                                                                     | 4  |

|-----|----------------------------------------------------------------------------------------------|----|

| 2   | Назначение                                                                                   | 5  |

| 2.1 | 1 Основные характеристики микросхемы                                                         | 6  |

| 2.2 | 2 Конструктивные характеристики микросхемы                                                   | 6  |

| 2.3 |                                                                                              |    |

| 3   | Структурная схема и описание работы микросхемы                                               | 14 |

| 3.1 | 1 Рекомендуемые схемы подключения                                                            | 15 |

| 3.2 | 2 Цифро-аналоговые преобразователи                                                           | 16 |

| 3.3 | 3 Тактовые сигналы                                                                           | 18 |

| 3.4 | 4 Включение питания и сброс                                                                  | 20 |

| 3.5 | 5 Автономный режим                                                                           | 22 |

| 3.6 | б Порт управления $I^2$ С                                                                    | 23 |

| 3.7 | 7 Запись по I <sup>2</sup> C                                                                 | 24 |

| 3.8 | 8 Чтение по I <sup>2</sup> C                                                                 | 25 |

| 3.9 | 9 Порт управления SPI                                                                        | 26 |

| 3.1 | 10 Чтение и запись по SPI в пакетном режиме                                                  | 27 |

| 3.1 | 11 Питание и опорное напряжение                                                              | 28 |

| 3.1 | 12 Последовательный порт ввода данных                                                        | 29 |

| 3.1 | 13 Режимы мультиплексирования с разделением по времени (TDM)                                 | 30 |

| 3.1 | 14 Датчик температуры 3                                                                      | 33 |

| 4   | Описание регистров управления                                                                | 33 |

| 4.] | 1 PLL_CLK_CTRL0 – регистр управления тактовым сигналом и<br>схемой ФАПЧ                      | 36 |

| 4.2 | 2 PLL_CLK_CTRL1 – регистр управления тактовым сигналом и<br>схемой ФАПЧ                      | 37 |

| 4.3 | 3 PDN_THRMSENS_CTRL_1 – регистр управления датчиком температуры и управления питанием блоков | 39 |

| 4.4 | 4 PDN_CTRL2 – регистр управления питанием каналов ЦАП                                        | 40 |

| 4.5 | 5 PDN_CTRL3 – регистр управления питанием каналов ЦАП                                        | 41 |

| 4.6 | б THRM_TEMP_STAT – регистр результата измерения температуры                                  | 41 |

| 4.7 | 7 DAC_CTRL0 - регистр управления                                                             | 42 |

| 4.8 | 8 DAC_CTRL1 - регистр управления                                                             | 43 |

| 4.9   | DAC_CTRL2 - регистр управления                                                                        | 44 |

|-------|-------------------------------------------------------------------------------------------------------|----|

| 4.10  | DAC_MUTE1 – регистр выключения звука каналов ЦАП                                                      | 46 |

| 4.11  | DAC_MUTE2 – регистр выключения звука каналов ЦАП                                                      | 47 |

| 4.12  | DACMSTR_VOL – регистр управления уровнем громкости всех каналов                                       | 48 |

| 4.13  | DAC01_VOL – регистр управления уровнем громкости 1 канала ЦАП                                         | 48 |

| 4.14  | DAC02_VOL – регистр управления уровнем громкости 2 канала ЦАП                                         | 48 |

| 4.15  | DAC03_VOL – регистр управления уровнем громкости 3 канала ЦАП                                         | 49 |

| 4.16  | DAC04_VOL – регистр управления уровнем громкости 4 канала ЦАП                                         | 49 |

| 4.17  | DAC05_VOL – регистр управления уровнем громкости 5 канала ЦАП                                         | 49 |

| 4.18  | DAC06_VOL – регистр управления уровнем громкости 6 канала ЦАП                                         | 50 |

| 4.19  | DAC07_VOL – регистр управления уровнем громкости 7 канала ЦАП                                         | 50 |

| 4.20  | DAC08_VOL – регистр управления уровнем громкости 8 канала ЦАП                                         | 50 |

| 4.21  | DAC09_VOL – регистр управления уровнем громкости 9 канала ЦАП                                         | 51 |

| 4.22  | DAC10_VOL – регистр управления уровнем громкости 10 канала ЦАП.                                       | 51 |

| 4.23  | DAC11_VOL – регистр управления уровнем громкости 11 канала ЦАП                                        | 51 |

| 4.24  | DAC12_VOL – регистр управления уровнем громкости 12 канала ЦАП                                        | 52 |

| 4.25  | DAC13_VOL – регистр управления уровнем громкости 13 канала ЦАП                                        | 52 |

| 4.26  | DAC14_VOL – регистр управления уровнем громкости 14 канала ЦАП                                        | 52 |

| 4.27  | DAC15_VOL – регистр управления уровнем громкости 15 канала ЦАП.                                       | 53 |

| 4.28  | DAC16_VOL – регистр управления уровнем громкости 16 канала ЦАП.                                       | 53 |

|       | CM_SEL_PAD_STRGTH – регистр управления нагрузочной<br>собностью цифровых выходов и вывода общей точки | 53 |

|       | DAC_POWER1 – регистр настройки потребляемой мощности алов ЦАП                                         | 54 |

|       | DAC_POWER2 – регистр настройки потребляемой мощности алов ЦАП                                         | 55 |

|       | DAC_POWER3 – регистр настройки потребляемой мощности алов ЦАП                                         | 56 |

|       | DAC_POWER4 – регистр настройки потребляемой мощности палов ЦАП                                        | 57 |

| Заклк | очение                                                                                                | 63 |

|       | ожение А (обязательное) Термины, определения и буквенные                                              |    |

| -     | значения параметров, не установленные действующими стандартами                                        | 64 |

| Лист  | регистрации изменений                                                                                 | 66 |

#### 1 Введение

Развитие цифровой техники и цифровых методов обработки сигналов определило современные тенденции в разработке самых разнообразных систем, устройств и приборов. Значительную роль в этих тенденциях занимает аналого-цифровое и цифро-аналоговое преобразование.

Цифро-аналоговый преобразователь (ЦАП) — это устройство для перевода цифровых данных в аналоговый сигнал.

Микросхемы ЦАП нашли широкое применение в усилителях звука, аудиокодеках, системах обработки видео, системах распознавания данных, системах калибровки датчиков, измерительных устройствах, системах управления двигателями, системах распределения данных, цифровых потенциометрах, системах цифровой связи и т. д.

Настоящее руководство пользователя содержит описание принципа работы и технические характеристики интегральной микросхемы 1273HA084 и другие сведения, необходимые для обеспечения полного использования технических возможностей микросхемы ЦАП.

#### 2 Назначение

Интегральная схема 1273НА084 — это однокристальный 16-канальный цифро-аналоговый преобразователь (ЦАП) для воспроизведения аудио сигналов. Микросхема включает в себя последовательный порт аудио данных, цифровые интерполирующие фильтры, аттенюаторы с логарифмической шкалой изменения уровня громкости, многоуровневые сигма-дельта ( $\Sigma$ - $\Delta$ ) модуляторы и усилительные каскады с дифференциальными выходами по напряжению.

Микросхема имеет интерфейсы SPI и I<sup>2</sup>C для управления режимами работы и установки уровня громкости каждого канала с помощью внешнего контроллера. В микросхеме 1273HA084 предусмотрен автономный режим работы без использования SPI и I<sup>2</sup>C, при котором настройки могут быть заданы с помощью внешних выводов.

Микросхема содержит схему фазовой автоподстройки частоты (ФАПЧ) для формирования внутренних тактовых сигналов. Тактовый сигнал может быть сформирован из сигнала кадровой синхронизации данных левого и правого канала (DLRCLK) или внешнего тактового сигнала от вывода MCLKI/ XTALI (вывод 63).

Напряжение питания аналоговой части микросхемы составляет 5 В, напряжение питания цифровой части — от 2,5 В, схемы ФАПЧ — от 2,5 В. Для получения необходимого напряжения питания цифровой части можно использовать интегрированный драйвер стабилизатора напряжения.

Интегральная схема 1273HA084 имеет датчик температуры кристалла. Чтобы измерить температуру или прочитать результат измерения, необходимо использовать интерфейсы управления.

Основные области применения микросхемы:

- профессиональные аудио устройства;

- домашние кинотеатры, автомобильные аудио системы;

- музыкальные сэмплеры, цифровые микшеры, цифровые процессоры аудио эффектов.

#### 2.1 Основные характеристики микросхемы

Основные характеристики микросхемы:

- напряжение питания цифровой части от 2,5 В;

- напряжение питания аналоговой части 5 В;

- тактовый сигнал внешний или формируемый при помощи схемы ФАПЧ;

- драйвер линейного стабилизатора с программируемым выходным напряжением для питания цифровой части;

- поддерживает разрядность входных данных до 24 бит и частоты дискретизации от 32 до 192 кГц;

- встроенный регулятор уровня громкости звука с автоматической плавной установкой;

- датчик температуры с цифровым выходом;

- управление по SPI и  $I^2$ C;

- программное выключение звука с отсутствием щелчков;

- программное переключение в режим пониженного энергопотребления;

- гибкий последовательный порт ввода данных с поддержкой режима мультиплексирования входных данных с разделением по времени (TDM).

#### 2.2 Конструктивные характеристики микросхемы

Микросхема выполнена в 88-выводном металлокерамическом корпусе 4235.88-1.

Масса микросхемы – не более 4,5 г.

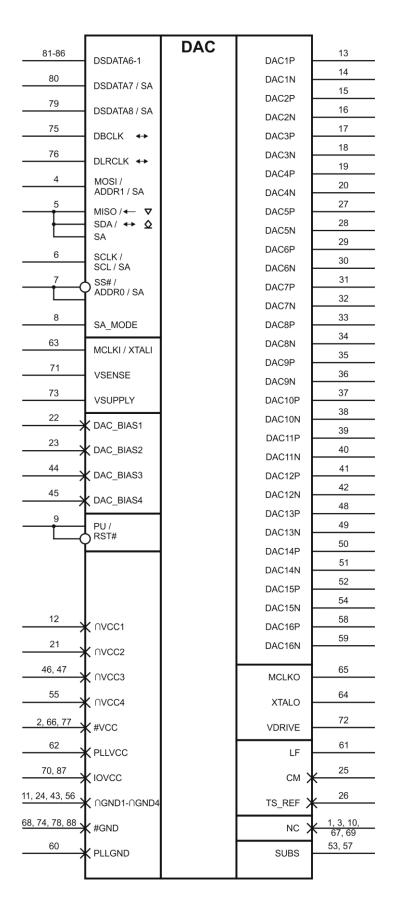

Условное графическое обозначение микросхемы приведено на рисунке 2.1.

Функциональное назначение выводов приведено в таблице 2.1.

Рисунок 2.1 – Условное графическое обозначение микросхемы 1273HA084

#### назначение

# Таблица 2.1 – Функциональное микросхемы 1273HA084

| Номер             | Обозначение         |                                                                                                            | Тип               |

|-------------------|---------------------|------------------------------------------------------------------------------------------------------------|-------------------|

| вывода            | вывода              | Функциональное назначение                                                                                  | вывода            |

| 1                 | 2                   | 3                                                                                                          | 4                 |

| 68, 74,<br>78, 88 | #GND                | Цифровая земля                                                                                             | -                 |

| 70, 87            | IOVCC               | Питание цифровых входных и выходных портов                                                                 | -                 |

| 71                | VSENSE              | Вывод подключения к выходу 2,5 В стабилизатора                                                             | I                 |

| 72                | VDRIVE              | Вывод управления базой проходного транзистора                                                              | 0                 |

| 73                | VSUPPLY             | Вход подключения 5 В стабилизатора                                                                         | I                 |

| 75                | DBCLK               | Вход/выход тактового сигнала последовательной загрузки данных ЦАП                                          | I/O               |

| 76                | DLRCLK              | Вход/выход сигнала кадровой синхронизации данных левого и правого каналов ЦАП                              | I/O               |

| 79                | DSDATA8/SA          | Вход последовательного ввода данных для ЦАП 15 и ЦАП 16/ Вход выбора режима TDM                            | I                 |

| 80                | DSDATA7/SA          | Вход последовательного ввода данных для ЦАП 13 и ЦАП 14/ Вход выбора режима TDM                            | I                 |

| 81                | DSDATA6             | Вход последовательного ввода данных для ЦАП 11 и ЦАП 12                                                    | I                 |

| 82                | DSDATA5             | Вход последовательного ввода данных для ЦАП 9 и ЦАП 10                                                     | Ι                 |

| 83                | DSDATA4             | Вход последовательного ввода данных для ЦАП 7 и ЦАП 8                                                      | I                 |

| 84                | DSDATA3             | Вход последовательного ввода данных для ЦАП 5 и ЦАП 6                                                      | Ι                 |

| 85                | DSDATA2             | Вход последовательного ввода данных для ЦАП 3 и ЦАП 4                                                      | Ι                 |

| 86                | DSDATA1             | Вход последовательного ввода данных для ЦАП 1 и ЦАП 2                                                      | Ι                 |

| 2, 66, 77         | #VCC                | Вход питания цифровой части                                                                                |                   |

| 4                 | MOSI/ADDR1/SA       | Вход управления данными(SPI)/ Адрес 1 (I <sup>2</sup> C)/ Автономный режим (SA_MODE)                       | I                 |

| 5                 | MISO/<br>SDA/<br>SA | Выход управления данными (SPI) Вход/выход управления данными (I <sup>2</sup> C) Автономный режим (SA_MODE) | O/Z<br>I/O/2<br>I |

| 6                 | SCLK/SCL/SA         | $egin{array}{cccccccccccccccccccccccccccccccccccc$                                                         | I                 |

## Продолжение таблицы 2.1

| 1  | 2            | 3                                                | 4 |

|----|--------------|--------------------------------------------------|---|

| 7  | SS#/ADDR0/SA | Вход выбора режима ведомого (slave) (SPI)        | I |

|    |              | активный низкий логический уровень/Адрес         |   |

|    |              | 0 (I <sup>2</sup> C)/ Автономный режим (SA_MODE) |   |

| 8  | SA_MODE      | Автономный режим                                 | I |

| 9  | PU/RST#      | Включение/ Сброс                                 | I |

| 11 | ∩GND1        | Аналоговая земля                                 | - |

| 12 | ∩VCC1        | Вход питания аналоговой части                    | - |

| 13 | DAC1P        | ЦАП 1 положительный выход                        | О |

| 14 | DAC1N        | ЦАП 1 отрицательный выход                        | О |

| 15 | DAC2P        | ЦАП 2 положительный выход                        | О |

| 16 | DAC2N        | ЦАП 2 отрицательный выход                        | О |

| 17 | DAC3P        | ЦАП 3 положительный выход                        | О |

| 18 | DAC3N        | ЦАП 3 отрицательный выход                        | О |

| 19 | DAC4P        | ЦАП 4 положительный выход                        | О |

| 20 | DAC4N        | ЦАП 4 отрицательный выход                        | О |

| 21 | ∩VCC2        | Вход питания аналоговой части                    | _ |

| 22 | DAC_BIAS1    | Вывод подключения внешней фильтрующей            | _ |

|    |              | емкости для ∩VCC2                                |   |

| 23 | DAC_BIAS2    | Вывод подключения внешней фильтрующей            | - |

|    |              | емкости для ∩GND2                                |   |

| 24 | ∩GND2        | Аналоговая земля                                 | _ |

| 25 | CM           | Вывод подключения внешней фильтрующей            | _ |

|    |              | емкости для опорного источника напряжения        |   |

|    |              | к выводу ∩GND2.                                  |   |

|    |              | Внутренний источник опорного напряжения          |   |

|    |              | может быть выключен с помощью регистра           |   |

|    |              | PLL CLK CTRL1, тогда вывод может                 |   |

|    |              | управляться от внешнего источника                |   |

|    |              | напряжения                                       |   |

| 26 | TS_REF       | Вывод подключения внешней фильтрующей            | - |

|    |              | емкости для опорного источника напряжения        |   |

|    |              | к выводу ∩GND2                                   |   |

| 27 | DAC5P        | ЦАП5 положительный выход                         | O |

| 28 | DAC5N        | ЦАП5 отрицательный выход                         | O |

| 29 | DAC6P        | ЦАП6 положительный выход                         | О |

| 30 | DAC6N        | ЦАП6 отрицательный выход                         | О |

| 31 | DAC7P        | ЦАП7 положительный выход                         | О |

| 32 | DAC7N        | ЦАП7 отрицательный выход                         | О |

| 33 | DAC8P        | ЦАП8 положительный выход                         | О |

| 34 | DAC8N        | ЦАП8 отрицательный выход                         | O |

| 35 | DAC9P        | ЦАП9 положительный выход                         | O |

| 36 | DAC9N        | ЦАП9 отрицательный выход                         | О |

| 37 | DAC10P       | ЦАП10 положительный выход                        | О |

| 38 | DAC10N       | ЦАП10 отрицательный выход                        | О |

| 39 | DAC11P       | ЦАП11 положительный выход                        | О |

| 40 | DAC11N       | ЦАП11 отрицательный выход                        | О |

Окончание таблицы 2.1

| 1         | 2                   | 3                                              | 4       |

|-----------|---------------------|------------------------------------------------|---------|

| 41        | DAC12P              | ЦАП12 положительный выход                      | О       |

| 42        | DAC12N              | ЦАП12 отрицательный выход                      | О       |

| 43        | ∩GND3               | Аналоговая земля                               | -       |

| 44        | DAC_BIAS3           | Вывод подключения внешней фильтрующей          | -       |

|           |                     | емкости для ∩GND3                              |         |

| 45        | DAC_BIAS4           | Вывод подключения внешней фильтрующей          | -       |

|           |                     | емкости для ∩VCC3                              |         |

| 46,47     | ∩VCC3               | Вход питания аналоговой части                  | -       |

| 48        | DAC13P              | ЦАП13 положительный выход                      | O       |

| 49        | DAC13N              | ЦАП13 отрицательный выход                      | O       |

| 50        | DAC14P              | ЦАП14 положительный выход                      | О       |

| 51        | DAC14N              | ЦАП14 отрицательный выход                      | О       |

| 52        | DAC15P              | ЦАП15 положительный выход                      | O       |

| 54        | DAC15N              | ЦАП15 отрицательный выход                      | О       |

| 55        | ∩VCC4               | Вход питания аналоговой части                  | -       |

| 56        | ∩GND4               | Аналоговая земля                               | -       |

| 58        | DAC16P              | ЦАП16 положительный выход                      | O       |

| 59        | DAC16N              | ЦАП16 отрицательный выход                      | O       |

| 60        | PLLGND              | PLL земля                                      | -       |

| 61        | LF                  | Вывод фильтра схемы ФАПЧ                       | О       |

| 62        | PLLVCC              | Вывод питания схемы ФАПЧ                       | -       |

| 63        |                     | Вход главного тактового сигнала/вход           | I       |

|           | MCLKI/XTALI         | кварцевого генератора                          |         |

| 64        | XTALO               | Выход инвертора кварцевого генератора          | О       |

| 65        | MCLKO               | Выход главного тактового сигнала               | О       |

| 53, 57    | SUBS                | Технологические выводы корпуса                 | -       |

| 1, 3, 10, | NC                  | Не используется                                | -       |

| 69, 67    |                     |                                                |         |

| П         | римечание – В графе | «Тип вывода»: I – вход, О – выход, Z – выход с | третьим |

Примечание – В графе «Тип вывода»: І – вход, О – выход, Z – выход с третьим состоянием, 2 – режим открытого стока.

#### 2.3 Электрические характеристики микросхемы

Электрические характеристики микросхем 1273НА084 при приемке и поставке приведены в таблице 2.2.

Значения предельно допустимых электрических режимов эксплуатации в диапазоне рабочих температур приведены в таблице 2.3.

Термины, определения, сокращения и буквенные обозначения параметров – по ОСТ В 11 0998-99, ГОСТ Р 57435-2017 и ГОСТ Р 57441-2017.

Термины, определения и буквенные обозначения параметров, неустановленные действующими стандартами, представлены в приложении A. Таблица 2.2 – Значения электрических параметров микросхемы 1273HA084 при приемке и поставке

| Наименование параметра,                                                                                                         | Буквенное обозначе- | Нор        |             | Темпера      |

|---------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|-------------|--------------|

| единица измерения, режим измерения                                                                                              | <del>   </del>      | парам      | _           | тура         |

|                                                                                                                                 | ние                 | не         | не<br>более | среды,<br>°С |

| 1                                                                                                                               | параметра           | менее<br>3 |             | 5            |

| 1 Drywania wanania wa wakana wa manya wa                                                                                        | 2                   | 3          | 4           | 3            |

| 1 Выходное напряжение низкого уровня по выводам DBCLK, DLRCLK, MISO/SDA/SA,                                                     | U <sub>OL</sub>     |            |             |              |

| MCLKO, B,                                                                                                                       |                     |            | 0,4         |              |

| $U_{CC1} = 4.5 \text{ B}, U_{CC2} = 3.0 \text{ B}, U_{CC3} = 3.0 \text{ B},$                                                    |                     | _          | 0,4         |              |

| $U_{CC4} = 3.0 \text{ B}, U_{CC2} = 3.0 \text{ B}, U_{CC3} = 3.0 \text{ B}, U_{CC4} = 3.0 \text{ B}, U_{CC4} = 1 \text{ MA}$    |                     |            |             |              |

| 2 Выходное напряжение высокого уровня по                                                                                        | U <sub>OH</sub>     |            |             | _            |

| выводам DBCLK, DLRCLK, MISO/SDA/SA,                                                                                             | Con                 |            |             |              |

| MCLKO, B,                                                                                                                       |                     | 2,4        | _           |              |

| $U_{CC1} = 4.5 \text{ B}, U_{CC2} = 3.0 \text{ B}, U_{CC3} = 3.0 \text{ B},$                                                    |                     | _, .       |             |              |

| $U_{CC4} = 3.0 \text{ B}, I_{OH} = -1 \text{ mA}$                                                                               |                     |            |             |              |

| 3 Размах дифференциального выходного                                                                                            | Upp                 |            |             | 1            |

| напряжения по выводам DAC1P – DAC1N,                                                                                            | rr                  |            |             |              |

| DAC2P – DAC2N, DAC3P – DAC3N,                                                                                                   |                     |            |             |              |

| DAC4P – DAC4N, DAC5P – DAC5N,                                                                                                   |                     |            |             |              |

| DAC6P – DAC6N, DAC7P – DAC7N,                                                                                                   |                     |            |             |              |

| DAC8P – DAC8N, DAC9P – DAC9N,                                                                                                   |                     |            |             |              |

| DAC10P – DAC10N, DAC11P – DAC11N,                                                                                               |                     |            |             |              |

| DAC12P – DAC12N, DAC13P – DAC13N,                                                                                               |                     |            |             |              |

| DAC14P – DAC14N, DAC15P – DAC15N,                                                                                               |                     | 8          | 9           |              |

| DAC16P – DAC16N, B,                                                                                                             |                     | O          |             | $-60 \pm 3$  |

| $U_{CC1} = 5.0 \text{ B}, U_{CC2} = 3.3 \text{ B}, U_{CC3} = 5.0 \text{ B},$                                                    |                     |            |             | $25 \pm 10$  |

| $U_{CC4} = 3.3 \text{ B}$                                                                                                       |                     |            |             | $85 \pm 3$   |

| 4 Ток утечки низкого уровня по выводам                                                                                          | $I_{ILL}$           |            |             |              |

| DSDATA1, DSDATA2, DSDATA3, DSDATA4,                                                                                             |                     |            |             |              |

| DSDATA5, DSDATA6, DSDATA7/SA,                                                                                                   |                     |            |             |              |

| DSDATA8/SA, DBCLK, DLRCLK,                                                                                                      |                     |            |             |              |

| MOSI/ADDR1/SA, MISO/SDA/SA, SCLK/SCL/SA,                                                                                        |                     |            |             |              |

| PU/RST#, SS#/ADDR0/SA, SA_MODE,                                                                                                 |                     | 10         |             |              |

| MCLKI/XTALI, мкА,<br>U <sub>CC1</sub> = 5,5 B, U <sub>CC2</sub> = 3,6 B, U <sub>CC3</sub> = 5,5 B,                              |                     | -10        | _           |              |

| $U_{CC4} = 3,5 \text{ B}, U_{CC2} = 3,0 \text{ B}, U_{CC3} = 3,5 \text{ B},$<br>$U_{CC4} = 3,6 \text{ B}, U_{IL} = 0 \text{ B}$ |                     |            |             |              |

| 5 Ток утечки высокого уровня по выводам                                                                                         | $I_{\rm ILH}$       |            |             |              |

| DSDATA1, DSDATA2, DSDATA3, DSDATA4,                                                                                             | ILH                 |            |             |              |

| DSDATA5, DSDATA6, DSDATA7/SA,                                                                                                   |                     |            |             |              |

| DSDATA8/SA, DBCLK, DLRCLK,                                                                                                      |                     |            |             |              |

| MOSI/ADDR1/SA, MISO/SDA/SA, SCLK/SCL/SA,                                                                                        |                     |            |             |              |

| PU/RST#, SS#/ADDR0/SA, SA MODE,                                                                                                 |                     |            |             |              |

| MCLKI/XTALI, mkA,                                                                                                               |                     | _          | 10          |              |

| $U_{CC1} = 5.5 \text{ B}, U_{CC2} = 3.6 \text{ B}, U_{CC3} = 5.5 \text{ B},$                                                    |                     |            |             |              |

| $U_{CC4} = 3.6 \text{ B}, U_{IH} = U_{CC3}$                                                                                     |                     |            |             |              |

| 6 Динамический ток потребления от источника                                                                                     | I <sub>OCC1</sub>   |            |             |              |

| U <sub>CC1</sub> , MA,                                                                                                          |                     | _          | 100         |              |

| $U_{CC1} = 5,5 \text{ B, } f_{CI\_MCLK} = 12,288 \text{ M}\Gamma \text{ц, } f_s = 48 \text{ к}\Gamma \text{ц}$                  |                     |            |             |              |

#### Окончание таблицы 2.2

| 1                                                                                                                                                                                                              | 2                 | 3   | 4   | 5                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|--------------------------|

| 7 Динамический ток потребления от источника $U_{CC2}$ , мA, $U_{CC2} = 3.6$ B, $f_{CI\_MCLK} = 12,288$ МГц, $f_s = 48$ кГц                                                                                     | I <sub>OCC2</sub> | -   | 40  |                          |

| 8 Динамический ток потребления от источника $U_{CC3}$ , мA, $U_{CC3} = 5.5$ B, $f_{CI\_MCLK} = 12,288$ МГц, $f_s = 48$ кГц                                                                                     | I <sub>OCC3</sub> | -   | 10  |                          |

| 9 Динамический ток потребления от источника $U_{CC4}$ , мA, $U_{CC4} = 3.6$ B, $f_{CI\_MCLK} = 12,288$ МГц, $f_s = 48$ кГц                                                                                     | I <sub>OCC4</sub> | -   | 10  |                          |

| 10 Погрешность усиления характеристики, % от полной шкалы, $U_{\rm CC1} = 5,0$ B, $U_{\rm CC2} = 3,3$ B                                                                                                        | E <sub>G</sub>    | -10 | 10  |                          |

| 11 Погрешность смещения характеристики, мВ, $U_{CC1} = 5.0 \text{ B}, U_{CC2} = 3.3 \text{ B}$                                                                                                                 | Eo                | -25 | 25  | $-60 \pm 3$<br>25 \pm 10 |

| 12 Динамический диапазон, дБ, $U_{CC1} = 5.0$ В, $U_{CC2} = 3.3$ В, $\Delta f = (20 \ \Gamma \mu - 20 \ \kappa \Gamma \mu)$ , $f_s = 48 \ \kappa \Gamma \mu$ , уровень входного сигнала $-60 \ dBFS$           | DNR               | 95  | _   | $85 \pm 3$               |

| 13 Общие гармонические искажения плюс шум, $U_{CC1} = 5.0$ B, $U_{CC2} = 3.3$ B, $\Delta f = (20 \ \Gamma \mu - 20 \ \kappa \Gamma \mu)$ , $f_s = 48 \ \kappa \Gamma \mu$ , уровень входного сигнала $-1$ dBFS | THD+N             | -   | -75 |                          |

| 14 Функциональный контроль                                                                                                                                                                                     | ФК                | -   | _   |                          |

#### Примечания

- 1 Нормы на электрические параметры приведены при условии: нагрузка выходов аудио 3,1 кОм.

- 2 Параметры  $I_{ILL}$ ,  $I_{ILH}$  при температуре минус 60 °C не измеряются, а гарантируются нормами при температуре (25  $\pm$  10) °C.

- 3 При измерении динамических токов потребления  $f_{\text{CI\_MCLK1}} = f_s \times 256 = 48 \times 256 = 12288 \ \kappa \Gamma \mu = 12,288 \ M \Gamma \mu \ (в режиме PLL mode).$

- 4 Измерения динамического диапазона проводятся без фильтра (RMS).

- 5 Измерения общих гармонических искажений плюс шум проводятся при всех работающих каналах.

- 6 При функциональном контроле  $f_{\text{CI\_MCLK1}} = f_s \times 256$  (в режиме PLL mode),  $f_{\text{CI\_MCLK1}} = f_s \times 512$  (в режиме Direct).

Таблица 2.3 – Предельно допустимые и предельные режимы эксплуатации микросхемы 1273HA084

|                                          | Буквенное             | Прел     | ельно     | Преле    | льный           |

|------------------------------------------|-----------------------|----------|-----------|----------|-----------------|

| Наименование параметра режима,           | обозначен             |          | ый режим  | _        | ким             |

| единица измерения                        | ие                    | -        |           | •        |                 |

| _                                        | параметра             | не менее | не более  | не менее | не более        |

| 1                                        | 2                     | 3        | 4         | 5        | 6               |

| 1 Напряжение питания по выводам          | U <sub>CC1</sub>      |          |           |          |                 |

| ∩VCC, B                                  |                       | 4,5      | 5,5       | -0,3     | 5,5             |

| 2 Напряжение питания по выводам          | U <sub>CC2</sub>      |          |           |          |                 |

| #VCC, B                                  |                       | 3,0      | 3,6       | -0,3     | 3,6             |

| 3 Напряжение питания по выводам IOVCC    | $U_{CC3}$             |          |           |          |                 |

| В                                        |                       | 3,0      | 5,5       | -0,3     | 5,5             |

| 4 Напряжение питания по выводу           | $U_{CC4}$             |          |           |          |                 |

| PLLVCC, B                                |                       | 2,25     | 3,6       | -0,3     | 3,6             |

| 5 Входное напряжение по выводу           | $U_{\rm I}$           |          |           |          |                 |

| VSUPPLY, B                               |                       | 3,0      | 5,5       | -0,3     | 6,0             |

| 6 Входное напряжение низкого уровня по   | U <sub>IL</sub>       |          |           |          |                 |

| выводам DSDATA1, DSDATA2, DSDATA3,       |                       |          |           |          |                 |

| DSDATA4, DSDATA5, DSDATA6,               |                       |          |           |          |                 |

| DSDATA7/SA, DSDATA8/SA, DBCLK,           |                       |          |           |          |                 |

| DLRCLK, MOSI/ADDR1/SA,                   |                       |          |           |          |                 |

| SO/SDA/SA,SCLK/SCL/SA, PU/RST#,          |                       |          |           |          |                 |

| SS#/ADDR0/SA, SA_MODE,                   |                       |          | 0.0       |          |                 |

| MCLKI/XTALI, B                           |                       | 0        | 0,8       | -0,3     | _               |

| 7 Входное напряжение высокого уровня     | $U_{ m IH}$           |          |           |          |                 |

| по выводам DSDATA1, DSDATA2,             |                       |          |           |          |                 |

| DSDATA3, DSDATA4, DSDATA5,               |                       |          |           |          |                 |

| DSDATA6, DSDATA7/SA, DSDATA8/SA,         |                       |          |           |          |                 |

| DBCLK, DLRCLK, MOSI/ADDR1/SA,            |                       |          |           |          |                 |

| MISO/SDA/SA, SCLK/SCL/SA, PU/RST#,       |                       |          |           |          |                 |

| SS#/ADDR0/SA, SA_MODE,<br>MCLKI/XTALI, B |                       | 2,5      | $U_{CC3}$ |          | H + 0.3         |

| 8 Выходной ток низкого уровня по         | $I_{OL}$              | 2,3      | 0003      | _        | $U_{CC3} + 0,3$ |

| выводам DBCLK, DLRCLK,                   | IOL                   |          |           |          |                 |

| MISO/SDA/SA, MCLKO, MA                   |                       | _        | 1         | _        | _               |

| 9 Выходной ток высокого уровня по        | $I_{OH}$              |          | 1         |          |                 |

| выводам DBCLK, DLRCLK,                   | IOH                   |          |           |          |                 |

| MISO/SDA/SA, MCLKO, MA                   |                       | -1       | _         | _        | _               |

| 10 Частота следования импульсов          | f <sub>CI_MCLK1</sub> | 1        |           |          |                 |

| тактовых сигналов MCLK в режиме PLL      | ZCI_MCLKI             |          |           |          |                 |

| mode                                     |                       |          |           |          |                 |

| $(256 \times f_s)$ , МГц                 |                       | 6,9      | 40,5      | _        | _               |

| 11 Частота следования импульсов          | fci_mclk2             | ,        | ,         |          |                 |

| тактовых сигналов MCLK в режиме Direct   |                       |          |           |          |                 |

| (512×f <sub>s</sub> ), МГц               |                       | _        | 27,1      | _        | _               |

#### Окончание таблицы 2.3

| 1                                                                                 | 2         | 3  | 4   | 5 | 6 |  |

|-----------------------------------------------------------------------------------|-----------|----|-----|---|---|--|

| 12 Частота следования импульсов                                                   | fci_sclk  |    |     |   |   |  |

| тактовых сигналов SCLK, МГц                                                       |           | _  | 10  | _ | - |  |

| 13 Частота следования импульсов                                                   | fci_dbclk |    |     |   |   |  |

| тактовых сигналов DBCLK в режиме PLL                                              |           |    |     |   |   |  |

| mode                                                                              |           |    |     |   |   |  |

| (256×f <sub>s</sub> ), МГц                                                        |           | _  | 27  | _ | _ |  |

| 14 Частота дискретизации, кГц                                                     | $f_s$     | 32 | 192 | _ | - |  |

| Примечание — Время работы в одном из предельных режимов должно быть не более 5 с. |           |    |     |   |   |  |

## 3 Структурная схема и описание работы микросхемы

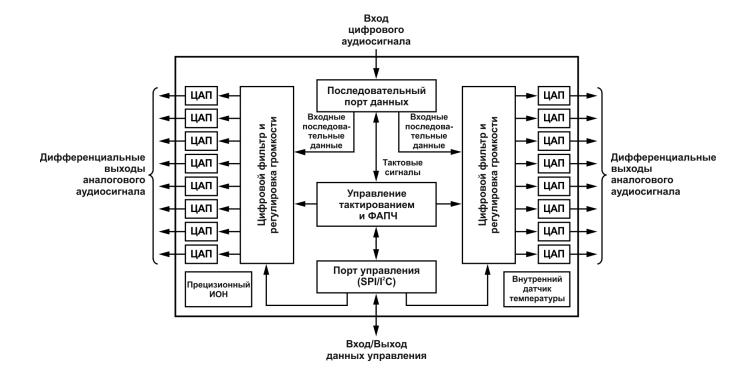

Структурная схема 1273НА084 представлена на рисунке 3.1.

Рисунок 3.1 - Структурная схема микросхемы 1273НА084

Микросхема поддерживает работу  $\mathbf{c}$ аудио данными, представленными в дополнительном коде, разрядностью 16 бит и 24 бита, с частотой от 32 до 192 кГц. Последовательный порт ввода данных имеет восемь линий данных (по два канала ЦАП на каждую линию), общий сигнал (DLRCLK) общий кадровой синхронизации тактовый И сигнал последовательной загрузки данных (DBCLK). В ИС 1273HA084 предусмотрен режим мультиплексирования входных данных с разделением по времени (TDM), при котором данные нескольких каналов могут быть переданы по одной линии данных (до 16 каналов).

#### 3.1 Рекомендуемые схемы подключения

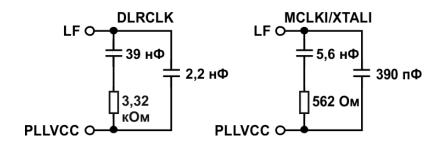

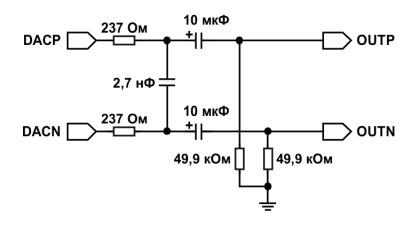

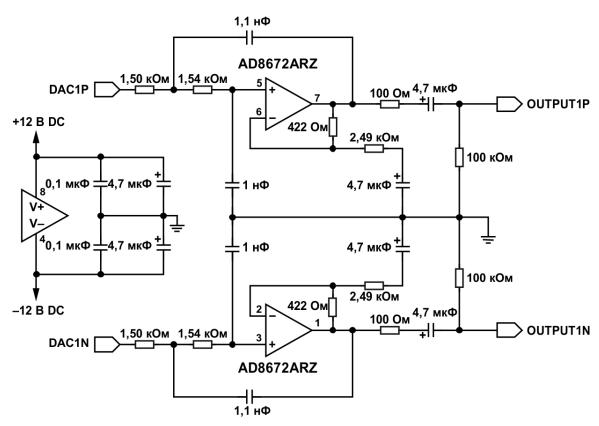

Рекомендуемые схемы подключения показаны на рисунках 3.2-3.5. Контурные фильтры для режимов синхронизации схемы ФАПЧ от сигналов DLRCLK и MCLKI/XTALI показаны на рисунке 3.2. Выходные фильтры для дифференциальных выходов ЦАП показаны на рисунках 3.3 и 3.5.

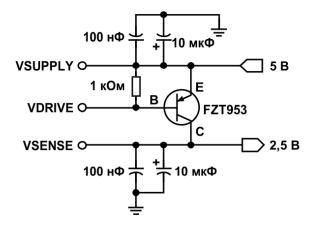

Схема внешнего стабилизатора показана на рисунке 3.4.

Рисунок 3.2 - Контурные фильтры для режимов синхронизации схемы ФАПЧ от сигналов DLRCLK и MCLKI/XTAL

Рисунок 3.3 - Выходной пассивный фильтр

Рисунок 3.4 - Схема внешнего стабилизатора

Рисунок 3.5 - Выходной активный фильтр Бесселя второго порядка

#### 3.2 Цифро-аналоговые преобразователи

Микросхема 1273НА084 имеет 16 дифференциальных каналов ЦАП с выходами по напряжению. Каналы ЦАП имеют встроенные цифровые интерполирующие фильтры с ослаблением сигнала в полосе задерживания 68 дБ, линейной ФЧХ. Каждый канал имеет свой независимый программируемый 256 шагов аттенюатор, с диапазоном регулировки по 0,375 дБ.

Микросхема 1273HA084 имеет режим малой задержки распространения сигнала. Этот режим доступен при  $f_S = 192 \ \kappa \Gamma \mu$  и включается с помощью битов [2:1] регистра DAC CTRLO. Установив эти разряды в 0b11, задержку распространения можно уменьшить до 10 мкс. Более короткая задержка достигается за счет уменьшения тракта цифровой фильтрации. Выбор ЭТОГО режима оказывает негативное уменьшается полоса пропускания в области звуковых частот и возрастает уровень шумов.

Каждый аналоговый выход в номинальном режиме имеет уровень постоянной составляющей 2,25 В. Дифференциальный сигнал имеет размах

± 2,12 В выше и ниже значения 2,25 В. Максимальный размах дифференциального выходного сигнала 8,48 В.

К дифференциальным аналоговым выходам требуется подключить фильтр, как показано на рисунках 3.3 и 3.5.

В микросхеме 1273HA084 предусмотрена функция управления аналоговыми характеристиками ЦАП. Поэтому можно программировать регистры для уменьшения потребляемой мощности за счет снижения уровней SNR и THD + N. Пониженное энергопотребление происходит за счет изменения внутренних токов смещения.

Регистры DAC\_POWER1 - DAC\_POWER4 используются для установки четырех режимов потребляемой мощности, индивидуально для каждого из 16 каналов (см. таблицу 3.1).

Таблица 3.1 - Режимы потребляемой мощности и изменение качества выходного сигнала

| Установки<br>регистра                               | Лучшее качество сигнала | Хорошее качество сигнала | Низкое<br>потребление | Минимальное<br>потребление |

|-----------------------------------------------------|-------------------------|--------------------------|-----------------------|----------------------------|

| Динамический ток потребления от источника $U_{CC1}$ | 84 мА                   | 75 мА                    | 66 мА                 | 56 мА                      |

| Отношение<br>сигнал/шум                             | 0 дБ                    | -0,2 дБ                  | -1,5 дБ               | -14,2 дБ                   |

| ТНD + N (уровень сигнала −1 дБ от полной шкалы )    | 0 дБ                    | -1,8 дБ                  | -3,0 дБ               | -5,8 дБ                    |

Для общего контроля потребляемой мощности всех каналов, могут использоваться биты [7:6] регистра PLL\_CLK\_CTRL1.

#### 3.3 Тактовые сигналы

При включении питания и установке высокого логического уровня на выводе PU/RST# микросхема начинает работу в автономном режиме или в режиме программирования, в зависимости от уровня сигнала на выводе SA\_MODE. Тактирование микросхемы в автономном режиме описано в разделе 3.5.

По умолчанию микросхема находится в режиме программирования, выводы DLRCLK и DBCLK находятся в режиме ведомого (slave). Для работы микросхемы 1273HA084 необходимо подать группу сигналов: MCLK, DLRCLK, DBCLK.

Программирование регистров PLL\_CLK\_CTRL0, PLL\_CLK\_CTRL1 разрешается только после установления высокого логического уровня на выводе PU/RST# (вывод 9).

При подаче тактового сигнала на вывод MCLKI/XTALI (вывод 63) с частотой  $256\times$ ,  $384\times$ ,  $512\times$  или  $768\times f_S$  (относительно  $f_S=48$  кГц) нужно выбрать встроенную на кристалле схемы ФАПЧ в качестве источника главного тактового сигнала. Для этого надо установить биты выбора главного тактового сигнала (MCS), как показано в таблице 3.3.

По умолчанию микросхема 1273HA084 находится в режиме  $256 \times f_S$  (биты MCS регистра PLL\_CLK\_CTRL0 установлены в 0b00),  $f_S = 48 \ \mathrm{k\Gamma \mu}$  (биты FS регистра DAC\_CTRL0 установлены в 0b00), тогда частота главного тактового сигнала должна быть равна 12,288 МГц. Чтобы перейти в режим с частотой дискретизации  $f_S = 96 \ \mathrm{k\Gamma \mu}$  при той же частоте главного тактового сигнала, необходимо установить биты FS регистра DAC\_CTRL0 в 0b01. Аналогичным образом можно установить режим с частотой дискретизации  $f_S = 192 \ \mathrm{k\Gamma \mu}$ .

В режиме по умолчанию встроенная схема ФАПЧ генерирует внутренний тактовый сигнал из внешнего тактового сигнала. Сигнал сброса активирует схему ФАПЧ, для этого не требуется запись в регистры через интерфейс I<sup>2</sup>C или SPI в нормальном режиме работы. При включенной схеме ФАПЧ среднеквадратичное значение ошибки временного интервала джиттера не превышает 300 пс.

Таблица 3.2 – Выбор частоты главного тактового сигнала и частоты

дискретизации

| Выбор частоты |                  | Выбор частоты главного тактового сигнала (биты MCS регистра |                      |         |                    |         |                  |         |

|---------------|------------------|-------------------------------------------------------------|----------------------|---------|--------------------|---------|------------------|---------|

| дискретизации |                  | PLL_CLK_CTRL0)                                              |                      |         |                    |         |                  |         |

| (биты FS      | MCS              | = b00                                                       | MCS                  | = b01   | MCS                | = b10   | MCS              | = b11   |

| регистра      | Отно-            | MCLK,                                                       | Отно-                | MCLK,   | Отно-              | MCLK,   | Отно-            | MCLK,   |

| DAC_CTRL0)    | шение            | МΓц                                                         | шение                | МΓц     | шение              | МΓц     | шение            | МΓц     |

| 32 кГц,       | $256 \times f_S$ | 8,192                                                       | $384 \times f_S$     | 12,288  | $512 \times f_S$   | 16,384  | $768 \times f_S$ | 24,576  |

| FS = b00      |                  |                                                             |                      |         |                    |         |                  |         |

| 44,1 кГц,     | $256 \times f_S$ | 11,2896                                                     | $384 \times f_S$     | 16,9344 | $512 \times f_S$   | 22,5792 | $768 \times f_S$ | 33,8688 |

| FS = b00      |                  |                                                             |                      |         |                    |         |                  |         |

| 48 кГц,       | $256 \times f_S$ | 12,288                                                      | $384 \times f_S$     | 18,432  | $512 \times f_S$   | 24,576  | $768 \times f_S$ | 36,864  |

| FS = b00      |                  |                                                             |                      |         |                    |         |                  |         |

| 64 кГц,       | $128 \times f_S$ | 8,192                                                       | 192 × f <sub>S</sub> | 12,288  | $256 \times f_S$   | 16,384  | $384 \times f_S$ | 24,576  |

| FS = b01      |                  |                                                             |                      |         |                    |         |                  |         |

| 88,2 кГц,     | $128 \times f_S$ | 11,2896                                                     | $192 \times f_S$     | 16,9344 | $256 \times f_S$   | 22,5792 | $384 \times f_S$ | 33,8688 |

| FS = b01      |                  |                                                             |                      |         |                    |         |                  |         |

| 96 кГц,       | $128 \times f_S$ | 12,288                                                      | $192 \times f_S$     | 18,432  | $256 \times f_S$   | 24,576  | $384 \times f_S$ | 36,864  |

| FS = b01      |                  |                                                             |                      |         |                    |         |                  |         |

| 128 кГц,      | $64 \times f_S$  | 8,192                                                       | $96 \times f_S$      | 12,288  | $128 \times f_S$   | 16,384  | $192 \times f_S$ | 24,576  |

| FS = b10      |                  |                                                             |                      |         |                    |         |                  |         |

| или FS = b11  |                  |                                                             |                      |         |                    |         |                  |         |

| 176,4 кГц,    | $64 \times f_S$  | 11,2896                                                     | $96 \times f_S$      | 16,9344 | $128 \times f_S$   | 22,5792 | $192 \times f_S$ | 33,8688 |

| FS = b10      |                  |                                                             |                      |         |                    |         |                  |         |

| или FS = b11  |                  |                                                             |                      |         |                    |         |                  |         |

| 192 кГц,      | $64 \times f_S$  | 12,288                                                      | $96 \times f_S$      | 18,432  | $128 \times f_{S}$ | 24,576  | $192 \times f_S$ | 36,864  |

| FS = b10      |                  |                                                             |                      |         |                    |         |                  |         |

| или FS = b11  |                  |                                                             |                      |         |                    |         |                  |         |

Когда схема ФАПЧ отключена, нужно использовать независимый кварцевый генератор для формирования главного тактового сигнала.

При использовании ИС 1273HA084 в режиме непосредственной подачи главного тактового сигнала, нужно выключить схему ФАПЧ с помощью регистра PDN\_THRMSENS\_CTRL\_1. В этом режиме нужно подать тактовый сигнал с частотой  $512 \times f_S$  (относительно  $f_S = 48 \ \mathrm{k\Gamma u}$ ) на вывод MCLKI, и установить бит CLK SEL регистра PLL CLK CTRL1 в 0b1.

Схема ФАПЧ в микросхеме 1273HA084 может быть запрограммирована в режим синхронизации от внешнего сигнала DLRCLK без внешнего главного тактового сигнала. Если установить биты PLLIN

регистра PLL\_CLK\_CTRL0 в 0b01 и подключить требуемый контурный фильтр к выводу LF (см. рисунок 3.2), то схема ФАПЧ будет генерировать все необходимые для работы внутренние тактовые сигналы без использования внешнего главного тактового сигнала. Этот режим уменьшает количество высокочастотных сигналов в конструкции и уменьшает электромагнитные помехи.

Так же можно уменьшить излучение электромагнитных помех схемы при использовании внутреннего тактового сигнала последовательной загрузки данных путем установки бита BCLK\_GEN в регистре DAC\_CTRL1 в 0b1.

Для тактирования внешних устройств можно использовать сигнал MCLKO (вывод 65). Режим работы сигнала MCLKO устанавливается битами [5:4] регистра PLL\_CLK\_CTRL1. По умолчанию значение битов 0b10, на выводе 65 действует буферизированный сигнал MCLKI.

Значение битов 0b00 устанавливает частоту сигнала МСLКО в диапазоне от 4 до 6 МГц. Значение 0b01 устанавливает частоту сигнала МСLКО — в диапазоне от 8 до 12 МГц. Значение тактовой частоты автоматически масштабируется относительно частоты сигнала МСLКІ (вывод 63).

$\Pi$  р и м е р 1 — Биты установлены в 0b00, частота сигнала МСLКI имеет значение 8,192 МГц, тогда на выходе МСLКО (вывод 65) будет сигнал с частотой (8,192/2) = 4,096 МГц.

$\Pi$  р и м е р 2 — Биты установлены в 0b01, частота сигнала МСLКI имеет значение 36,864 МГц, тогда на выходе МСLКО (вывод 65) будет сигнал с частотой (36,864/3) = 12,288 МГц.

#### 3.4 Включение питания и сброс

Последовательность подачи напряжения питания:

- подать напряжение питания аналоговой части микросхемы на выводы  $\cap$ VCC (выводы 12, 21, 46, 47, 55);

- подать напряжение питания входных и выходных портов на выводы IOVCC (вывод 70, 87);

- только после установления напряжения на выводах ∩VCC и IOVCC подается напряжение питания на выводы #VCC (выводы 2, 67, 77) (при

использовании внутреннего линейного стабилизатора это условие выполняется по умолчанию);

- во время установления всех напряжений питания микросхемы, на вывод PU/RST# (вывод 9) должен подаваться низкий уровень. После установления всех напряжений питания необходимо установить высокий логический уровень на выводе PU/RST# (вывод 9) (для этого можно использовать простую RC цепь).

Низкий уровень сигнала PU/RST# переводит микросхему в состояние низкого энергопотребления (менее 3,0 мкА), блокируя функционирование микросхемы до подачи высокого логического уровня сигнала PU/RST#. После подачи высокого логического уровня на этот вывод, микросхеме требуется 300 мс для перехода в рабочие состояние.

Для начала работы с микросхемой необходимо установить бит PUP регистра PLL\_CLK\_CTRL0 в 0b1. Бит PUP используется для отключения питания микросхемы. Установка бита PUP в 0b0 переводит микросхему в режим ожидания, сохраняя при этом настройки всех регистров. Кроме того, для отключения отдельных блоков микросхемы можно использовать биты управления питанием в регистре PDN\_THRMSENS\_CTRL1.

После установки бита PUP, необходимо установить бит MMUTE регистра DAC CTRL0 в 0b0 для включения звука всех каналов.

Бит SOFT\_RST в регистре PLL\_CLK\_CTRL0 устанавливает во всех регистрах управления значения по умолчанию, кроме регистров PLL\_CLK\_CTRL0 и PLL\_CLK\_CTRL1. Бит SOFT\_RST не выключает аналоговые выходы, и переключение этого разряда не дает слышимых звуковых щелчков.

Последовательность включения микросхемы 1273НА084:

- подать напряжения питания на микросхему 1273HA084, как было описано выше;

- подать на вывод PU/RST# высокий логический уровень после того, как источники питания стабилизируются;

- установить бит PUP в 0b1;

- запрограммировать нужные регистры для обеспечения требуемого режима работы;

- установить бит ММUТЕ в 0b0, чтобы включить звук на всех каналах.

#### 3.5 Автономный режим

Микросхема 1273HA084 может работать без управления по интерфейсам I<sup>2</sup>C или SPI. Такой автономный режим можно задать, установив на выводе SA\_MODE уровень напряжения IOVCC. Все регистры имеют значения по умолчанию, задание режимов осуществляется с помощью внешних выводов (смотрите таблицу 3.3).

Таблица 3.3 - Настройки автономного режима

| Номер<br>вывода | Значение логического уровня | Режим работы микросхемы                                                                                                          |  |  |  |  |

|-----------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 4               | 0                           | Режим ведущего (master) последовательного интерфейса аудиоданных Режим ведомого (slave) последовательного интерфейса аудиоданных |  |  |  |  |

| 5               | 0<br>1                      | $MCLKI = 256 \times f_S$ , схема ФАПЧ включена $MCLKI = 384 \times f_S$ , схема ФАПЧ включена                                    |  |  |  |  |

| 6               | 0                           | Должен быть установлен в 0                                                                                                       |  |  |  |  |

| 7               | 0                           | Формат данных последовательного интерфейса - I <sup>2</sup> S. Режим TDM последовательного интерфейса задается выводами 79 и 80  |  |  |  |  |

| Применения      |                             |                                                                                                                                  |  |  |  |  |

Примечания

- 1. Высокий логический уровень соответствует подключению к IOVCC.

- 2. Низкий логический уровень соответствует подключению к #GND.

Для установки режима TDM последовательного интерфейса в автономном режиме работы, нужно подать высокий уровень (уровень напряжения IOVCC) на вывод 7. В таблице 3.4 показаны доступные настройки режима TDM, установка этих режимов происходят путем подключения выводов DSDATA8 и DSDATA7 к выводам #GND или IOVCC.

После включения микросхемы 1273HA084 в автономном режиме и установки PU/RST# в высокий уровень, на выводе MCLKO действует буферизированный сигнал MCLKI.

Таблица 3.4 - Режимы TDM

| Номер вывода | Значения логического | Режим работы микросхемы                  |

|--------------|----------------------|------------------------------------------|

|              | уровня               |                                          |

|              | 00                   | TDM4: DLRCLK импульс                     |

| 80:79        | 01                   | TDM8: DLRCLK импульс                     |

| 00.77        | 10                   | TDM16: DLRCLK импульс                    |

|              | 11                   | TDM8: DLRCLK 50 % коэффициент заполнения |

| Ппимеч       | ания                 |                                          |

Примечания

- Высокий логический уровень соответствует подключению к IOVCC.

- Низкий логический уровень соответствует подключению к #GND.

#### 3.6 Порт управления I<sup>2</sup>C

Микросхема 1273HA084 имеет порт управления, совместимый с I<sup>2</sup>C, который позволяет осуществлять программирование и чтение данных внутренних регистров управления микросхемы. Интерфейс I<sup>2</sup>C в микросхеме 1273НА084 — двухпроводный, состоящий из линии тактового сигнала SCL (вывод 6) и линии данных SDA (вывод 5).

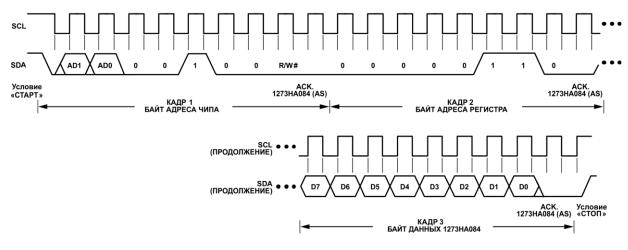

Линия SDA является двунаправленной. Микросхема передает данные по SDA либо для подтверждения приема данных от ведущего (master) устройства (сигнал ACK), либо во время операции чтения. Линия SDA в режиме порта I<sup>2</sup>C имеет конфигурацию с открытым стоком, которая требует внешний подтягивающий к высокому логическому уровню резистор сопротивлением 2 кОм. Операция записи или чтения начинается, когда линия SDA переключается в низкий логический уровень при высоком уровне на линии SCL, как показано на рисунках 3.6 и 3.7.

Изменение сигнала SDA разрешено только при низком уровне сигнала SCL, за исключением тех случаев, когда возникает условие «СТАРТ» или «СТОП», как показано на рисунках 3.6 и 3.7. Первые 8 бит слова данных состоят из адреса устройства и бита чтения/записи R/W#. Адрес устройства состоит из внутреннего встроенного адреса (0х04) и адреса, заданного двумя выводами 4 (ADDR1) и 7 (ADDR0) (см. таблицу 3.5).

Таблица 3.5 - Адреса I<sup>2</sup>C

| ADDR1 | ADDR0 | Адреса ведомого (slave) |

|-------|-------|-------------------------|

| 0     | 0     | 0x04                    |

| 0     | 1     | 0x24                    |

| 1     | 0     | 0x44                    |

| 1     | 1     | 0x64                    |

#### 3.7 Запись по **I**<sup>2</sup>C

Два разряда адреса позволяют использовать в системе четыре микросхемы 1273HA084. Инициализация операции записи в микросхеме включает в себя следующие шаги (см. рисунок 3.6):

- отправка условия «СТАРТ»;

- отправка адреса устройства с установкой бита R/W# в низкий логический уровень. Микросхема отвечает сигналом подтверждения, чтобы сообщить об адресации к устройству;

- отправка второго кадра, указывающего микросхеме, в какой регистр должна быть сделана запись. Микросхема передает второй сигнал подтверждения;

- отправка третьего кадра с восемью разрядами данных, которые необходимо записать в регистр. Микросхема передает третий сигнал подтверждения;

- отправка условия «СТОП» для завершения передачи данных.

Таблица 3.6 - Запись одиночного слова данных по I<sup>2</sup>C

| S                                                          | Адрес ИС, $R/W# = 0$ | AS     | Адрес регистра     | AS    | Слово данных    | AS      | P     |  |

|------------------------------------------------------------|----------------------|--------|--------------------|-------|-----------------|---------|-------|--|

|                                                            | Примечание — S       | - Стар | товый бит, Р - Сто | повый | бит, АМ - Подтв | ерждені | ие от |  |

| ведущего (master), AS - Подтверждение от ведомого (slave). |                      |        |                    |       |                 |         |       |  |

Т а б л и ц а 3.7 - Запись данных в пакетном режиме по  $I^2C$

| S                                                          | Адрес ИС, | AS  | Адрес      | AS  | Слово      | AS    | Слово      | AS    | Слово            | AS     | P  |

|------------------------------------------------------------|-----------|-----|------------|-----|------------|-------|------------|-------|------------------|--------|----|

|                                                            | R/W# = 0  |     | регистра   |     | данных     |       | данных     |       | данных           |        |    |

|                                                            | -         |     |            |     | 1          |       | 2          |       | N                |        |    |

|                                                            | Примечани | е — | S - Старто | вый | бит, Р - С | гопов | вый бит, А | M - I | <b>Тодтвержд</b> | ение ( | ОТ |

| ведущего (master), AS - Подтверждение от ведомого (slave). |           |     |            |     |            |       |            |       |                  |        |    |

Рисунок 3.6 - Формат записи по  $I^2C$

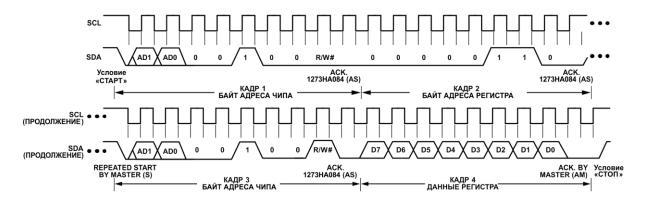

#### 3.8 Чтение по І<sup>2</sup>С

Для выполнения операции чтения требуется сначала произвести запись, чтобы указать нужный регистр, а после этого выполнить чтение данных. Для этого нужно выполнить следующие шаги (см. рисунок 3.7):

- отправка условия «СТАРТ», за которым следует кадр адреса устройства с низким уровнем бита R/W#. и кадр адреса регистра. Микросхема отвечает сигналом подтверждения;

- повторная отправка условия «СТАРТ». Далее следует кадр адреса устройства с высоким уровнем бита R/W#. В следующем кадре микросхема выводит данные регистра на линию SDA;

- отправка условия «СТОП» для завершения операции чтения.

Таблица 3.8 - Чтение одиночного слова данных по I<sup>2</sup>C

| S   | Адрес ИС,                                                               | AS | Адрес    | AS | S | Адрес ИС, | AS | Слово  | AM | P |

|-----|-------------------------------------------------------------------------|----|----------|----|---|-----------|----|--------|----|---|

|     | R/W# = 0                                                                |    | регистра |    |   | R/W#=1    |    | данных |    |   |

| ВАП | Примечание — S - Стартовый бит, P - Стоповый бит, AM - Подтверждение от |    |          |    |   |           |    |        |    |   |

| ВСД | ведущего (master), AS - Подтверждение от ведомого (slave).              |    |          |    |   |           |    |        |    |   |

Таблица 3.9 - Чтение данных в пакетном режиме по I<sup>2</sup>C

| S | 1 | Адрес | A | Адрес   | A | S | Адрес | A | Слово  | A | Слово  | A | Слово  | A | P |

|---|---|-------|---|---------|---|---|-------|---|--------|---|--------|---|--------|---|---|

|   | I | ИС,   | S | регистр | S |   | ИС,   | S | данных | M | данных | M | данных | M |   |

|   | F | R/W#  |   | a       |   |   | R/W#  |   | 1      |   | 2      |   | N      |   |   |

|   | = | = 0   |   |         |   |   | = 1   |   |        |   |        |   |        |   |   |

$\Pi$  р и м е ч а н и е - S - Стартовый бит, P - Стоповый бит, AM - Подтверждение от ведущего (master), AS - Подтверждение от ведомого (slave).

Рисунок 3.7 - Формат чтения по  $I^2C$

#### 3.9 Порт управления SPI

Микросхема 1273HA084 имеет порт управления SPI, который позволяет осуществлять программирование и чтение данных внутренних регистров управления.

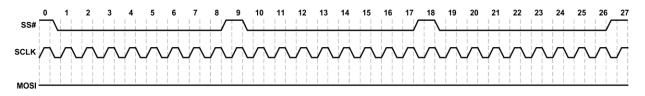

По умолчанию микросхема находится в режиме I<sup>2</sup>C. Чтобы войти в режим управления по SPI, нужно выполнить три пустые операции записи через порт SPI (микросхема не дает подтверждения для этих трех операций), как показано на рисунке 3.8. Начиная с четвертого цикла записи, данные могут быть записаны или считаны из микросхемы. Микросхема может выйти из режима управления по SPI только по сигналу PU/RST#, который инициализируется при подаче питания на микросхему.

Рисунок 3.8 - Последовательность сигналов для инициализации порта SPI

Порт управления по SPI микросхемы – это 4-проводный последовательный интерфейс. Информация передается в виде 24-разрядных слов данных. Сигналы SS# и SCLK могут быть асинхронны относительно частоты дискретизации микросхемы. В таблице 3.10 показан формат байта адреса при использовании SPI.

Первый байт слова данных является глобальным адресом чипа с битом чтения/записи. Для микросхемы адрес 0x06 сдвинут влево на один разряд изза бита R/W#. Второй байт – это адрес регистра микросхемы, третий байт – это данные (рисунки 3.9 и 3.10).

Таблица 3.10 - Формат байта адреса чипа с битом R/W#.

| Разряд 0 | Разряд 1 | Разряд 2 | Разряд 3 | Разряд 4 | Разряд 5 | Разряд 6 | Разряд 7 |

|----------|----------|----------|----------|----------|----------|----------|----------|

| 0        | 0        | 0        | 0        | 1        | 1        | 0        | R/W#     |

Рисунок 3.9 - Временная диаграмма сигналов при операции записи по SPI

Во время операции чтения из микросхемы вывод MISO/SDA/SA находится в третьем состоянии до начала третьего байта, когда на вывод поступают данные (см. рисунок 3.10). Вывод MISO/SDA/SA находится в третьем состоянии на протяжении всего остального времени, что позволяет подключить его к шине, соединяющий несколько устройств.

Младший бит первого байта при передаче данных по SPI - это разряд R/W#. Он определяет операцию чтения (логический уровень 1) или записи (логический уровень 0). См. таблицу 3.10.

Рисунок 3.10 - Временная диаграмма сигналов при операции чтения по SPI

#### 3.10 Чтение и запись по SPI в пакетном режиме

Через порт SPI можно осуществлять чтение и запись в пакетном режиме. Это делается путем отправки байта с адресом чипа с битом R/W#, далее выполняется отправка первого адреса регистра, в который будет производиться запись или чтение. Далее, до тех пор, пока удерживается низкий уровень сигнала SS# (вывод 7), регистры могут быть последовательно считаны или записаны, при подаче тактового сигнала SCLK.

Для программирования регистров по SPI в пакетном режиме нужно выполнить следующие действия:

- отправка байта адреса с битом R/W# равного логическому нулю (операция записи);

- отправка адреса первого регистра;

- отправка значений регистров;

- переключение вывода SS# (вывод 7) для окончания передачи;

- чтение в пакетном режиме для того, чтобы убедиться, что запись регистров прошла успешно.

#### 3.11 Питание и опорное напряжение

Напряжение питания аналоговой части микросхемы 5,0 B, напряжение питания цифровой части от 2,5 B, напряжение питания цифровых входных и выходных портов 3,3 B или 5,0 B.

Для защиты микросхемы от помех в цепи питания надо шунтировать выводы питания микросхемы керамическими чип конденсаторами емкостью 100 нФ, расположенными как можно ближе к выводам. Также нужно установить электролитические конденсаторы, емкостью не менее 22 мкФ для каждой шины питания.

Микросхема 1273HA084 включает в себя драйвер линейного стабилизатора, которому требуется внешний силовой транзистор и шунтирующий конденсатор для построения стабилизатора с программируемым выходным напряжением (биты VREG\_CTRL регистра DAC\_CTRL2). Рекомендуемая схема стабилизатора показана на рисунке 3.4.

Если драйвер стабилизатора не используется, то нужно подключить выводы VSUPPLY и VDRIVE к выводам #GND и оставить вывод VSENSE неподключенным.

Все цифровые входы и выходы совместимы с логическими уровнями ТТЛ и КМОП.

Внутреннее опорное напряжение датчика температуры выводится на вывод TS\_REF. К этому выводу необходимо подключить конденсаторы емкостью  $10 \text{ мк}\Phi$  и  $100 \text{ н}\Phi$ , соединенными параллельно как можно ближе к микросхеме.

Схема внутреннего источника опорного напряжения (ИОН), основана на ширине запрещенной зоны. ИОН задает напряжение средней точки ЦАП и имеет выход на вывод СМ. ИОН может быть отключен в регистре PLL\_CLK\_CTRL1 установкой бита VREF\_EN в 0b0, при этом вывод СМ может управляться от внешнего источника.

К выводу СМ требуется подключить конденсаторы емкостью 10 мкФ и 100 нФ, соединенные параллельно, как можно ближе к микросхеме.

Опорное напряжение на выводе СМ может использоваться для подачи смещения на внешний операционный усилитель (ОУ), который буферизует выходные сигналы. Чтобы получить малошумящий источник с низким сопротивлением для подключения к внешним цепям, необходимо изолировать вывод СМ от внешней цепи с помощью малошумящего ОУ.

#### 3.12 Последовательный порт ввода данных

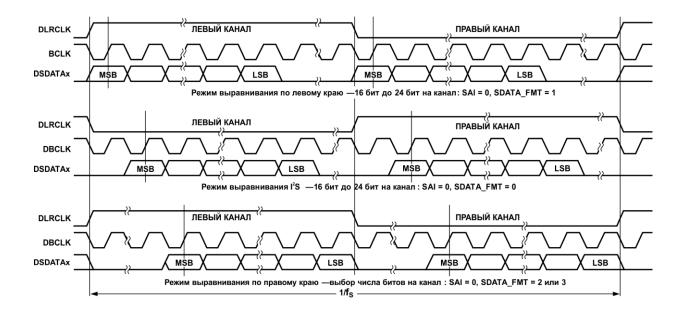

Последовательный порт ввода данных имеет восемь линий данных DSDATAх (по два канала на каждую линию), общий сигнал кадровой синхронизации (DLRCLK) и общий тактовый сигнал последовательной загрузки данных (DBCLK). Временные диаграммы сигналов последовательного порта в стерео режимах показаны на рисунке 3.11.

По умолчанию последовательный порт работает в режиме I<sup>2</sup>S; он устанавливается при включении питания и сбросе. Порт может быть запрограммирован в режимы работы с выравниванием данных по левому и по правому краю (24- и 16-разрядных данных), с помощью битов SDATA\_FMT регистра DAC\_CTRL0. Для выбора режима стерео и TDM служат биты SAI регистра DAC\_CTRL0. Полярность вывода DLRCLK программируется с помощью бита LRCLK\_POL регистра DAC\_CTRL1, что позволяет легко менять местами каналы.

Рисунок 3.11 - Временные диаграммы сигналов последовательного порта в стерео режимах

Вывод DBCLK позволяет захватывать данные по переднему или заднему фронту тактового сигнала. Бит BCLK\_EDGE регистра DAC\_CTRL1 служит для выбора активного фронта.

Последовательный порт может быть установлен в режим ведущего (master) и режим ведомого (slave) путем установки бита SAI\_MS регистра DAC\_CTRL1. По умолчанию последовательный порт находится в режиме ведомого (slave).

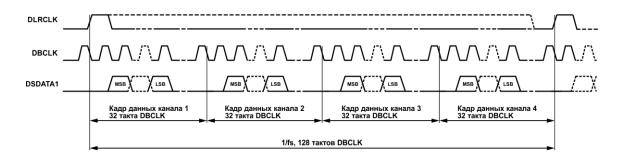

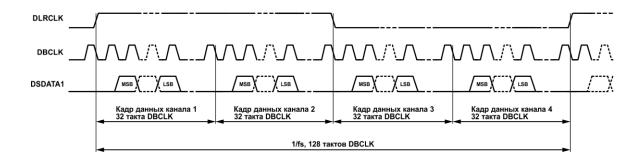

## 3.13 Режимы мультиплексирования с разделением по времени (TDM)

Последовательный порт данных микросхемы 1273НА084 поддерживает несколько режимов мультиплексирования с разделением по времени (TDM). Микросхема 1273НА084 поддерживает работу с одной линией данных (TDM16), с двумя линиями данных (TDM8), с четырьмя линиями данных (TDM4) или с восьмью линиями данных (TDM2). Сигнал кадровой синхронизации DLRCLK может работать как в режиме коротких импульсов длительностью, равной одному периоду тактового сигнала, так и в режиме с коэффициентом заполнения импульса 50 %. Для каждого режима можно выбрать длительность передачи данных 16 или 32 такта на канал.

Назначение выводов последовательного порта определяется в зависимости от выбранного режима TDM (см. таблицу 3.11).

Таблица 3.11 - Назначение выводов последовательного порта в зависимости от режима TDM

|               | Стерео                       | Режим TDM4           | Режим TDM8         | Режим TDM16        |

|---------------|------------------------------|----------------------|--------------------|--------------------|

| C             | режимы                       | (SAI = 2)            | (SAI = 3)          | (SAI = 4)          |

| Сигнал        | (SAI = 0 или                 | ,                    |                    | , ,                |

|               | SAI = 1                      |                      |                    |                    |

|               | Канал 1/Канал                |                      |                    |                    |

| DSDATA1       | 2                            | Каналы 1 - 4         | Каналы 1 - 8       | Каналы 1 - 12      |

| DSDITIT       | ввод данных                  | ввод данных          | ввод данных        | ввод данных        |

|               | Канал 3/Канал                | Каналы 5 - 8         | Каналы 9 - 12      |                    |

| DSDATA2       | 4                            | ввод данных          | ввод данных        | Не используется    |

|               | ввод данных                  | ввод данных          | ввод данных        |                    |

|               | Канал 5/Канал                | Каналы 9 - 12        |                    |                    |

| DSDATA3       | 6                            | ввод данных          | Не используется    | Не используется    |

|               | ввод данных                  | -7474-               |                    |                    |

|               | Канал 7/Канал                | II                   | TT                 | TT                 |

| DSDATA4       | 8                            | Не используется      | Не используется    | Не используется    |

|               | ввод данных<br>Канал 9/Канал |                      |                    |                    |

| DSDATA5       | 10                           | Не используется      | Не используется    | Не используется    |

| DSDATAS       | ввод данных                  | The mellosibs yellex | пс используется    | пе используется    |

|               | Канал                        |                      |                    |                    |

| DSDATA6       | 11/Канал 12                  | Не используется      | Не используется    | Не используется    |

|               | ввод данных                  | ,                    | ,                  |                    |

|               | Канал                        |                      |                    |                    |

| DSDATA7       | 13/Канал 14                  | Не используется      | Не используется    | Не используется    |

|               | ввод данных                  |                      |                    |                    |