# МИКРОСХЕМА ИНТЕГРАЛЬНАЯ 1867ВМ8Т

Руководство пользователя  $N\!\!\!_{2}2$

ОПИСАНИЕ ИНСТРУКЦИЙ

# Содержание

| Введение. Набор инструкций процессора цифровой обработки сигналов 1867ВМ8Т | 3   |

|----------------------------------------------------------------------------|-----|

| 1 Символы и аббревиатуры набора инструкций, пример описания инструкции     | 4   |

| 1.1 Набор инструкций: символы и аббревиатуры                               | 4   |

| 1.2 Пример описания инструкции                                             | 8   |

| 2 Краткое описание набора инструкций                                       | 10  |

| 2.1 Арифметические операции                                                | 10  |

| 2.2 Логические операции                                                    | 15  |

| 2.3 Операции управления выполнением программы                              | 17  |

| 2.4 Операции загрузки и сохранения                                         | 20  |

| 2.5 Повтор однократной инструкции                                          | 24  |

| 3 Классы инструкций и количество циклов их выполнения                      | 26  |

| 4 Подробное описание набора инструкций                                     | 68  |

| Приложение А (обязательное) Коды условий                                   | 249 |

| Приложение Б (обязательное) Регистры состояния и управления процессором    | 251 |

| Лист регистрации изменений                                                 | 252 |

|                                                                            |     |

#### Введение. Набор инструкций процессора цифровой обработки сигналов 1867ВМ8Т

Настоящий документ является продолжением руководства КФДЛ.431299.026 микросхемы 1867ВМ8Т и подробно описывает систему команд этого процессора. Благодаря глубокой конвейеризации и разветвленной системе команд процессор 1867ВМ8Т одинаково хорошо поддерживает численно емкие операции обработки сигналов и приложения общего назначения, такие как многопроцессорная обработка и высокоскоростное управление.

Необходимо отметить, что под термином «мнемоника» в настоящем документе подразумевается символьное обозначение инструкции, поступающей на вход транслятора (ассемблера). Для многих мнемоник существует несколько вариантов синтаксиса, отличающихся наличием и количеством различных операндов, различными вариантами их расположения и/или сдвига; вариантами размещения и/или сдвига полученного результата и т.д. Поэтому после ассемблирования одной и той же мнемоники с разными синтаксисами программа-транслятор выдает разные двоичные коды операций процессора (opcode), которые представляют собой, по сути, самостоятельные инструкции. Несмотря на возможность создания программного кода с использованием высокоуровневых языков, для оптимизации объема задействованной пограммной памяти и обеспечения вычислений в масштабе реального времени, разработчики широко применяют ассемблер, как минимум, для написания наиболее часто повторяемых и/или наиболее критичных по времени сегментов программы. Зачастую, один и тот же результат может быть получен с использованием разных инструкций и их сочетаний. Настоящий документ содержит всю необходимую информацию для создания оптимального исходного ассемблерного кода. В нем подробно изложены все особенности выполнения каждой инструкции, включая количество циклов, требуемых для ее выполнения в конвейере с учетом различных комбинаций хранения программного кода и операндов.

Настоящий документ состоит из четырех основных разделов, структурированных следующим образом:

- Раздел 1 содержит описание символов и аббревиатур набора инструкций и пример описания инструкции.

- Раздел 2 включает краткое описание инструкций, классифицированное по их функциональному назначению.

- Раздел 3 описывает классы инструкций и количество циклов их выполнения для различных комбинаций хранения программы кода и операндов.

- Раздел 4 посвящен детальному описанию каждой инструкции.

В качестве приложений в конце документа приведены коды условий, их возможные комбинации, применяемые в условных инструкциях, а также формат регистров состояния процессора.

# 1 Символы и аббревиатуры набора инструкций, пример описания инструкции

### 1.1 Набор инструкций: символы и аббревиатуры

В таблицах с 1 по 4 приводятся символы и аббревиатуры, используемые в разделе 2 «Краткое описание инструкций» и в разделе 4 при индивидуальном описании инструкций.

Таблица 1 – Символы и аббревиатуры набора инструкций

| Таолица 1 | <ul> <li>Символы и аббревиатуры набора инструкций</li> </ul>                        |

|-----------|-------------------------------------------------------------------------------------|

| Символ    | Описание                                                                            |

| A         | Аккумулятор А                                                                       |

| ALU       | Арифметико-логическое устройство                                                    |

| AR        | Вспомогательный регистр общего назначения (РОН)                                     |

| ARx       | Вспомогательный регистр с определенным номером $(0 \le x \le 7)$                    |

| ARP       | Поле в ST0, указывающее на вспомогательный регистр на странице – это 3-разрядное    |

|           | поле, которое указывает на выбранный (текущий) вспомогательный регистр (AR)         |

| ASM       | 5-разрядное поле в ST1, определяющее режим сдвига в аккумуляторе (-16 ≤ASM ≤15)     |

| В         | Аккумулятор В                                                                       |

| BRAF      | Флаг активизации повтора блока в ST1                                                |

| BRC       | Счетчик повтора блока                                                               |

| BITC      | 4-разрядное значение, которое определяет, какой бит (номер бита) в указанной ячейке |

|           | памяти данных будет проверен инструкцией тестирования битов ( $0 \le BITC \le 15$ ) |

| C16       | Бит в ST1, определяющий режим арифметических операций:                              |

|           | две 16-разрядых операции/операция с двойной точностью                               |

| C         | Бит переноса в ST0                                                                  |

| CC        | 2-разрядный код условия $(0 \le CC \le 3)$                                          |

| CMPT      | Бит режима совместимости в ST1                                                      |

| CPL       | Бит режима компиляции в ST1                                                         |

| cond      | Операнд, представляющий собой условие, тестируемое в условных инструкциях           |

| [D]       | Опция задержки (выполнения инструкции)                                              |

| DAB       | Адресная шина D                                                                     |

| DAR       | Регистр адреса DAB                                                                  |

| dmad      | 16-разрядный непосредственный адрес памяти данных $(0 \le \text{dmad} \le 65535)$   |

| Dmem      | Операнд памяти данных                                                               |

| DP        | 9-разрядное поле в ST0, указывающее на страницу памяти данных $(0 \le DP \le 511)$  |

| dst       | Аккумулятор, в который будет записан результат операции – приемник А или В          |

| dst_      | Аккумулятор, противоположный (альтернативный) приемному:                            |

|           | если $dst = A$ , то $dst_{} = B$ ;                                                  |

|           | если $dst = B$ , то $dst_{-} = A$                                                   |

| EAB       | Адресная шина Е                                                                     |

| EAR       | Регистр адреса ЕАВ                                                                  |

| FRCT      | Бит в ST1 – указатель дробного режима                                               |

| hi(A)     | Старшая часть (старшее слово) аккумулятора А (биты 31-16)                           |

| HM        | Бит HOLD-режима {фиксации или захвата} (в ST1)                                      |

| IFR       | Регистр флага прерывания                                                            |

| INTM      | Бит в ST1, указывающий на режим прерывания                                          |

| K         | Короткое непосредственное значение длиной менее 9 разрядов                          |

| k3        | 3-разрядное непосредственное значение $(0 \le k3 \le 7)$                            |

| k5        | 5-разрядное непосредственное значение ( $-16 \le k5 \le 15$ )                       |

| k9        | 3-разрядное непосредственное значение ( $0 \le k9 \le 511$ )                        |

| lk        | 16-разрядное длинное непосредственное значение                                      |

| Lmem      | 32-разрядный единый операнд памяти данных, использующий длиннословную               |

| ·         | адресацию                                                                           |

| mmr, MMR  | Регистр, отображаемый в память                                                      |

| MMRx,     | Регистр, картированный в памяти, AR0-AR7 или SP                                     |

| MMRy      | ***                                                                                 |

| n         | Количество слов после инструкции XC; n = 1 или 2                                    |

# Окончание таблицы 1

| Символ   | Описание                                                                         |

|----------|----------------------------------------------------------------------------------|

| N        | Номер статусного регистра, модифицируемого инструкциями RSBX, SSBX:              |

|          | N = 0 – регистр состояния ST0;                                                   |

|          | N = 1 – регистр состояния ST1                                                    |

| OVA      | Флаг переполнения для аккумулятора A (в ST0)                                     |

| OVB      | Флаг переполнения для аккумулятора В (в ST0)                                     |

| OVdst    | Флаг переполнения приемного аккумулятора А или В                                 |

| OVdst_   | Флаг переполнения аккумулятора, противоположного приемному А или В               |

| OVsrc    | Флаг переполнения аккумулятор – источник А или В                                 |

| OVM      | Бит режима обработки переполнения (в ST1)                                        |

| PA       | 16-разрядный непосредственный адрес порта ( $0 \le PA \le 65535$ )               |

| PAR      | Регистр программного адреса                                                      |

| PC       | Счетчик команд                                                                   |

| pmad     | 16-разрядный непосредственный адрес памяти программ ( $0 \le pmad \le 65535$ )   |

| Pmem     | Операнд в программной памяти                                                     |

| PMST     | Регистр состояния режимов процессора                                             |

| prog     | Операнд в программной памяти                                                     |

| [R]      | Опция округления                                                                 |

| RC       | Счетчик повторов                                                                 |

| REA      | Регистр конечного адреса повторяемого блока                                      |

| rnd      | Округление                                                                       |

| RSA      | Регистр стартового адреса повторяемого блока                                     |

| RTN      | Регистр быстрого возврата, используемый в инструкции RETF[D]                     |

| SBIT     | 4-разрядное значение, указывающее номер бита в регистре состояния, который будет |

|          | модифицирован инструкциями RSBX, SSBX (0 ≤ SBIT ≤ 15)                            |

| SHFT     | 4-разрядное значение сдвига ( $0 \le SHFT \le 15$ )                              |

| SHIFT    | 5-разрядное значение сдвига ( $-16 \le SHIFT \le 15$ )                           |

| Sind     | Одинарный операнд памяти данных, использующий косвенную адресацию                |

| Smem     | 16-разрядный одинарный операнд памяти данных                                     |

| SP       | Указатель стека                                                                  |

| src      | Аккумулятор-источник А или В                                                     |

| ST0, ST1 | Регистры состояния 0 и 1                                                         |

| SXM      | Бит режима знакового расширения (ST1)                                            |

| T        | Регистр временного хранения                                                      |

| TC       | Тестовый флаг в ST0                                                              |

| TOS      | Вершина стека                                                                    |

| TRN      | Регистр перемещений                                                              |

| TS       | Значение сдвига, определяемое битами 5-0 T-регистра ( $-16 \le TS \le 15$ )      |

| uns      | Беззнаковый                                                                      |

| XF       | Бит состояния внешнего флага в ST1                                               |

| Xmem     | 16-разрядный операнд памяти данных, используемый в инструкциях                   |

|          | с двойными операндами и некоторых инструкциях с одинарными операндами            |

| Ymem     | 16-разрядный операнд памяти данных, используемый в инструкциях                   |

|          | с двойными операндами                                                            |

| SP       | Значение указателя стека уменьшается на 1 (декремент на 1)                       |

| + + SP   | Значение указателя стека увеличивается на 1 (инкремент на 1)                     |

| + + PC   | Значение счетчика команд увеличивается на 1 (инкремент на 1)                     |

Таблица 2 – Символы и аббревиатуры кода операций

| · · · · · · · · · · · · · · · · · · · | волы и аооревиатуры кода операции                                          |

|---------------------------------------|----------------------------------------------------------------------------|

| Символ                                | Описание                                                                   |

| A                                     | Разряд адреса памяти данных                                                |

| ARX                                   | 3-разрядная величина, определяющая вспомогательный регистр                 |

| BITC                                  | 4-разрядный код бита                                                       |

| CC                                    | 2-разрядный код условия                                                    |

| CCCC CCCC                             | 8-разрядный код условия                                                    |

| COND                                  | 4- разрядный код условия                                                   |

| D                                     | Разряд выбора аккумулятора-приемника                                       |

|                                       | D = 0 - aккумулятор A                                                      |

|                                       | $D = 1 - a \kappa k y M y л \pi t o p B$                                   |

| I                                     | Разряд режима адресации                                                    |

|                                       | I = 0 – режим прямой адресации                                             |

|                                       | I = 1 – режим косвенной адресации                                          |

| K                                     | Короткий непосредственный операнд меньше 9 разрядов                        |

| MMRX                                  | 4-разрядное значение, указывающее на один из девяти картированных в памяти |

|                                       | регистров ( $0 \le MMRX \le 8$ )                                           |

| MMRY                                  | 4-разрядное значение, указывающее на один из девяти картированных в памяти |

|                                       | регистров $(0 \le MMRY \le 8)$                                             |

| N                                     | Одиночный бит                                                              |

| NN                                    | 2-разрядное значение, определяющее тип прерывания                          |

| R                                     | Разряд опции округления (rnd)                                              |

|                                       | R = 0 – инструкция выполняется без округления                              |

|                                       | R = 1 - результат округляется                                              |

| S                                     | Разряд выбора аккумулятора-источника                                       |

|                                       | S = 0 — аккумулятор A                                                      |

|                                       | S = 1 - аккумулятор B                                                      |

| SBIT                                  | 4-разрядный номер бита статусного регистра                                 |

| SHFT                                  | 4-разрядное значение сдвига $(0 \le SHFT \le 15)$                          |

| SHIFT                                 | 5-разрядное значение сдвига ( $-16 \le SHIFT \le 15$ )                     |

| X                                     | Разряд памяти данных                                                       |

| Y                                     | Разряд памяти данных                                                       |

| Z                                     | Разрзяд активизации задержанных инструкций                                 |

|                                       | Z = 0 — инструкция выполняется без задержки                                |

|                                       | Z = 1 – инструкция выполняется с задержкой                                 |

Таблица 3 – Синтаксис набора инструкций (условные символы и форматы)

| Символ            | Описание                                                                                                     |

|-------------------|--------------------------------------------------------------------------------------------------------------|

| Жирные            | Обязательная и неизменяемая часть синтаксиса инструкций выделяется жирным шрифтом.                           |

| символы           | Пример: В синтаксисе <b>ADD</b> <i>Xmem</i> , <i>Ymem</i> , <i>dst</i> можно использовать различные значения |

|                   | для <i>Хтет</i> и <i>Утет</i> , но слово <b>ADD</b> является неизменяемым и вводится, как приведено          |

| Наклонные         | Переменные в синтаксисе инструкций выделяются наклонным шрифтом.                                             |

| символы           | Пример: В синтаксисе <b>ADD</b> <i>Xmem</i> , <i>Ymem</i> , <i>dst</i> можно использовать различные значения |

|                   | для Хтет и Үтет                                                                                              |

| [x]               | Операнд в квадратных скобках является опционным (необязательным).                                            |

| . ,               | Пример: В синтаксисе <b>ADD</b> Smem [, SHIFT], src [, dst] необходимо обязательно указать                   |

|                   | значения Smem и src, а SHIFT и dst указываются в случае необходимости. Если не                               |

|                   | указывать SHIFT и dst в мнемоническом синтаксисе, компилятор сформирует двоичный                             |

|                   | код инструкции таким образом, что сложение будет выполнено без сдвига, а результат                           |

|                   | запишется в то место, откуда брались исходные данные (по умолчанию $dst = src$ )                             |

| #                 | Префикс константы, используемой для непосредственной адресации. Применяется с                                |

|                   | короткими и длинными непосредственными операндами в инструкциях, допускающих                                 |

|                   | различные режимы адресации, чтобы избежать неопределенности и указать на                                     |

|                   | непосредственный операнд.                                                                                    |

|                   | Hanpuмер: RPT #15 – короткая непосредственная адресация; следующая инструкция                                |

|                   | будет выполнена 16 раз.                                                                                      |

|                   | RPT 15 - прямая адресация; количество повторов следующей инструкции определяется                             |

|                   | значением ячейки памяти с адресом 15 на соответствующей странице (в зависимости от DP).                      |

|                   | Допускается применение в инструкциях, использующих только непосредственные                                   |

|                   | операнды. <i>Например</i> : RPTZ A,#15 эквивалентно RPTZ A, 15                                               |

| (abc)             | Содержимое регистра или ячейки аbc.                                                                          |

|                   | Пример: (src) означает содержимое аккумулятора-источника                                                     |

| $x \rightarrow y$ | Значение х присваивается регистру или ячейке у.                                                              |

|                   | $\Pi$ ример: (Smem) $\rightarrow$ dst означает, что содержимое указанной ячейки памяти загружается в         |

|                   | аккумулятор-приемник                                                                                         |

| r(n-m)            | Разряды от n до m регистра или ячейки r.                                                                     |

|                   | Пример: src(15-0) разряды с 15-го по 0-вой аккумулятора—источника                                            |

| << nn             | Сдвиг на nn разрядов влево (отрицательный или положительный)                                                 |

| ĬĬ                | Параллельная инструкция                                                                                      |

| <u>  </u>         | Вращение влево                                                                                               |

| //                | Вращение вправо                                                                                              |

| ~X                | Логическая инверсия от х                                                                                     |

| X                 | Абсолютное значение х                                                                                        |

| AAh               | Показывает что значение АА представлено в шестнадцатиричном виде                                             |

Таблица 4 – Операторы набора инструкций

| Символы     | Операторы                                | Просмотр (анализ) |

|-------------|------------------------------------------|-------------------|

| + - ~       | Унарные плюс, минус, логическая инверсия | Справа налево     |

| * / %       | Умножение, деление, модуль               | Слева направо     |

| + -         | Сложение, вычитание                      | Слева направо     |

| << >>       | Сдвиг влево, сдвиг вправо                | Слева направо     |

| <<<         | Логический сдвиг влево                   | Слева направо     |

| < ≤         | Меньше чем, меньше или равно             | Слева направо     |

| > ≥         | Больше чем, больше или равно             | Слева направо     |

| <b>≠</b> != | Не равно                                 | Слева направо     |

| &           | Поразрядное "И"                          | Слева направо     |

| ٨           | Поразрядное "Исключающее ИЛИ"            | Слева направо     |

| 1           | Поразрядное "ИЛИ"                        | Слева направо     |

Примечание — +, -, \* имеют приоритет над бинарными формами.

#### 1.2 Пример описания инструкции

Это пример типового описания инструкции, позволяющий ознакомиться с форматом описания инструкций и объясняющий, что описывает каждый заголовок. В данном подразделе при описании каждой инструкции представлена следующая информация:

- ассемблерный синтаксис;

- операнды;

- опкод (код операции двоичное представление инструкции);

- выполнение;

- статусные биты;

- количество слов;

- описание;

- количество циклов;

- классы:

- примеры.

Описание каждой инструкции начинается с ассемблерного синтаксиса. Метки могут размещаться перед инструкцией в той же строке или в первом столбце предыдущей строки. Синтаксическое выражение может заканчиваться дополнительным полем комментария. Следующие поля должны быть разделены пробелами:

- метка;

- инструкция и операнды;

- комментарий.

#### Синтаксис

- 1: **ПРИМЕР** *Smem, src*

- 2: **ПРИМЕР** *Smem*, **TS**, *src*

- 3: **ПРИМЕР** Smem, **16**, src [, dst]

- 4: **ПРИМЕР** *Smem* [, *SHIFT*], *src* [, *dst*]

Описание каждой инструкции начинается с ассемблерного синтаксиса. Смотри таблицы 1-3, описывающие символы синтаксиса инструкций.

Операнды

Smem: Одинарный операнд памяти данных Xmem, Ymem: Двойные операнды памяти данных

src, dst: A (аккумулятор A) В (аккумулятор B)

$-16 \le SHIFT \le 15$

Операнды могут быть константами или выражениями, вычисляемыми при ассемблировании, для ссылки на память, порты ввода/вывода, адреса регистров, указатели и различные другие константы. В этом прдразделе приводится также допустимый диапазон значений операндов.

Опкод

Опкод раскладывается на различные битовые поля для составления каждой инструкции. Смотри таблицы 1, 2, описывающие символы, применяемые в кодах инструкций.

Выполнение

- 1:  $(Smem) + (src) \rightarrow src$

- 2:  $(Smem) \ll (TS) + (src) \rightarrow src$

- 3:  $(Smem) \ll 16 + (src) \rightarrow dst$

- 4: (Smem) [<< SHIFT] +  $(src) \rightarrow dst$

Секция Выполнение описывает процедуры, имеющие место при выполнении инструкции. Для инструкций, имеющих несколько вариантов синтаксиса, нумерация вариантов опкода и выполнения соответствует нумерации синтаксиса. Смотри таблицу 1, описывающую символы, применяемые в секции «Выполнение».

Статусные биты

Выполнение инструкции может зависеть от состояния полей или отдельных разрядов статусных регистров; и, в свою очередь, вызывать в ходе выполнения изменение этих полей или разрядов. Оба эти варианта описываются в данной секции.

Описание

Эта секция описывает выполнение инструкций, и его влияние на состояние процессора и содержимое памяти. Обсуждаются все ограничения, накладываемые на операнды со стороны процессора или транслятора. Описание дублирует и дополняет символическую информацию, приведенную в секции «Выполнение».

Слово

В этом поле указывается количество слов памяти, требуемых для хранения инструкции и расширяющего ее слова. Для инструкций, использующих одноадресный режим, приводится количество слов для каждой модификации, за исключением модификаций с длинным смещением, которые требуют одного дополнительного слова.

Циклов

В этом поле указывается количество циклов, требуемых процессору 1867ВМ8Т, для выполнения одной инструкции с данными, расположенными в DARAM, и программным адресом из внутрикристального ПЗУ. Дополнительная детализация количества требуемых циклов при других конфигурациях памяти и в режиме повтора приводится в разделе 3 «Классы инструкций и количество циклов их выполнения».

Классы

В этом поле указывается класс инструкции для каждого синтаксиса. Смотри раздел 3 «Классы инструкций и количество циклов их выполнения» для описания каждого класса.

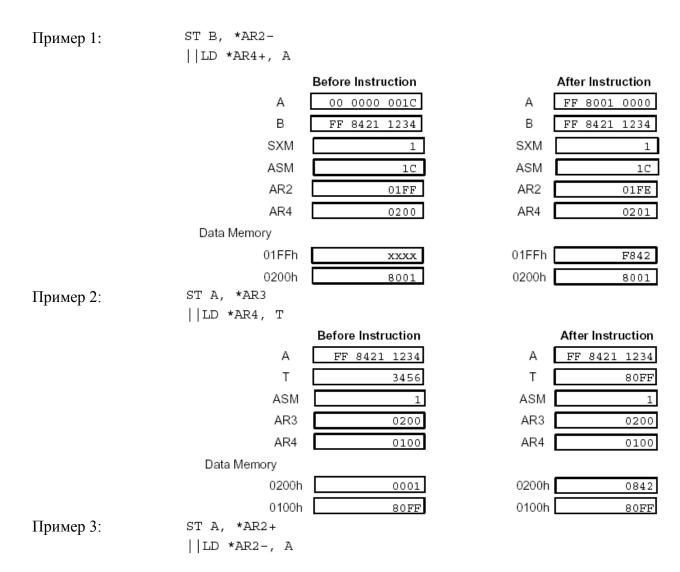

Пример

Код примера включен в каждую инструкцию. Приводится исходное содержимое памяти и/или регистров (до выполнения) и их именение в результате выполнения инструкции.

#### 2 Краткое описание набора инструкций

Набор инструкций процессора 1867BM8T можно разделить на четыре основных типа операций:

- арифметические операции;

- логические операции;

- операции управления с выполнением программы;

- операции загрузки и сохранения.

В данном разделе каждый тип операций в свою очередь разделен на более мелкие группы, в соответствии с выполняемыми функциями. Для каждого листинга инструкций приводится наилучшее количество слов, циклов и класс инструкции. Включена информация по повтору однократных инструкций и список инструкций, не работающих в режиме повтора (неповторяемых инструкций).

#### 2.1 Арифметические операции

В этом подразделе собраны инструкции арифметических операций. В таблицах с 5 по 10 приводятся инструкции, разделенные на следующие функциональные группы:

- инструкции сложения таблица 5;

- инструкции вычитания таблица 6;

- инструкции умножения таблица 7;

- инструкции умножения с накоплением и умножения с вычитанием таблица 8;

- двойные (с 32-разрядным операндом) инструкции таблица 9;

- инструкции для специфических применений таблица 10.

Таблица 5 – Инструкции сложения

| Синтаксис                     | Выражение                         | Cл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|-------------------------------|-----------------------------------|-------------------|--------------------|----------|

| ADD Smem, src                 | src = src + Smem                  | 1                 | 1                  | 3A, 3B   |

| ADD Smem, TS, src             | src = src + Smem << TS            | 1                 | 1                  | 3A, 3B   |

| ADD Smem, 16, src[, dst]      | dst = src + Smem << 16            | 1                 | 1                  | 3A, 3B   |

| ADD Smem[, SHIFT], src[, dst] | dst = src + Smem << SHIFT         | 2                 | 2                  | 4A, 4B   |

| ADD Xmem, SHFT, src           | src = src + Xmem << SHFT          | 1                 | 1                  | 3A       |

| ADD Xmem, Ymem, dst           | $dst = Xmem \ll 16 + Ymem \ll 16$ | 1                 | 1                  | 7        |

| ADD #lk[, SHFT], src[, dst]   | dst = src + #lk << SHFT           | 2                 | 2                  | 2        |

| ADD #lk, 16, src[, dst]       | $dst = src + \#lk \ll 16$         | 2                 | 2                  | 2        |

| ADD src[, SHIFT][, dst]       | $dst = dst + src \ll SHIFT$       | 1                 | 1                  | 1        |

| ADD src, ASM[, dst]           | $dst = dst + src \ll ASM$         | 1                 | 1                  | 1        |

| ADDC Smem, src                | src = src + Smem + C              | 1                 | 1                  | 3A, 3B   |

| ADDM #lk, Smem                | Smem = Smem + #lk                 | 2                 | 2                  | 18A, 18B |

| ADDS Smem, src                | src = src + uns(Smem)             | 1                 | 1                  | 3A, 3B   |

<sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 6 – Инструкции вычитания

| Синтаксис                                 | Выражение                                                                                                   | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------|--------------------|--------|

| SUB Smem, src                             | src = src - Smem                                                                                            | 1                 | 1                  | 3A, 3B |

| SUB Smem, TS, src                         | src = src — Smem << TS                                                                                      | 1                 | 1                  | 3A, 3B |

| SUB Smem, 16, <i>src</i> [ , <i>dst</i> ] | dst = src - Smem << 16                                                                                      | 1                 | 1                  | 3A, 3B |

| SUB Smem[, SHIFT], src[, dst]             | dst = src — Smem << SHIFT                                                                                   | 2                 | 2                  | 4A, 4B |

| SUB Xmem, SHFT, src                       | src = src — Xmem << SHFT                                                                                    | 1                 | 1                  | 3A     |

| SUB Xmem, Ymem, dst                       | dst = Xmem << 16 Ymem << 16                                                                                 | 1                 | 1                  | 7      |

| SUB #lk[, SHFT], src[, dst]               | dst = src — #lk << SHFT                                                                                     | 2                 | 2                  | 2      |

| SUB #lk, 16, src[, dst]                   | $dst = src - \#lk \ll 16$                                                                                   | 2                 | 2                  | 2      |

| SUB src[, SHIFT][, dst]                   | dst = dst — src << SHIFT                                                                                    | 1                 | 1                  | 1      |

| SUB src, ASM[, dst]                       | dst = dst src << ASM                                                                                        | 1                 | 1                  | 1      |

| SUBB Smem, src                            | $src = src - Smem - \check{C}$                                                                              | 1                 | 1                  | 3A, 3B |

| SUBC Smem, src                            | Если (src — Smem $<< 15$ ) $\geq 0$<br>src = (src — Smem $<< 15$ ) $<< 1 + 10$<br>Иначе<br>src = src $<< 1$ | 1<br>1            | 1                  | 3A, 3B |

| SUBS Smem, src                            | src = src - uns(Smem)                                                                                       | 1                 | 1                  | 3A, 3B |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 7 – Инструкции умножения

| Синтаксис           | Выражение                     | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс  |

|---------------------|-------------------------------|-------------------|--------------------|--------|

| MPY Smem, dst       | dst = T * Smem                | 1                 | 1                  | 3A, 3B |

| MPYR Smem, dst      | dst = rnd(T * Smem)           | 1                 | 1                  | 3A, 3B |

| MPY Xmem, Ymem, dst | dst = Xmem * Ymem, T = Xmem   | 1                 | 1                  | 7      |

| MPY Smem, #lk, dst  | dst = Smem * #lk, T = Smem    | 2                 | 2                  | 6A, 6B |

| MPY #lk, dst        | dst = T * #lk                 | 2                 | 2                  | 2      |

| MPYA dst            | dst = T * A(32-16)            | 1                 | 1                  | 1      |

| MPYA Smem           | B = Smem * A(32-16), T = Smem | 1                 | 1                  | 3A, 3B |

| MPYU Smem, dst      | dst = uns(T) * uns(Smem)      | 1                 | 1                  | 3A, 3B |

| SQUR Smem, dst      | dst = Smem * Smem, T = Smem   | 1                 | 1                  | 3A, 3B |

| SQUR A, dst         | dst = A(32-16) * A(32-16)     | 1                 | 1                  | 1      |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 8 – Инструкции умножения с накоплением и умножения с вычитанием

| Синтаксис                   | Выражение                                               | Cл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|-----------------------------|---------------------------------------------------------|-------------------|--------------------|----------|

| MAC Smem, src               | src = src + T * Smem                                    | 1                 | 1                  | 3A, 3B   |

| MAC Xmem, Ymem, src[, dst]  | dst = src + Xmem * Ymem,<br>T = Xmem                    | 1                 | 1                  | 7        |

| MAC #lk, src[, dst]         | dst = src + T * #lk                                     | 2                 | 2                  | 2        |

| MAC Smem, #lk, src[, dst]   | dst = src + Smem * #lk,<br>T = Smem                     | 2                 | 2                  | 6A, 6B   |

| MACR Smem, src              | src = rnd(src + T * Smem)                               | 1                 | 1                  | 3A, 3B   |

| MACR Xmem, Ymem, src[, dst] | dst = rnd(src + Xmem * Ymem),<br>T = Xmem               | 1                 | 1                  | 7        |

| MACA Smem[, B]              | B = B + Smem * A(32-16),<br>T = Smem                    | 1                 | 1                  | 3A, 3B   |

| MACA T, src[, dst]          | dst = src + T * A(32-16)                                | 1                 | 1                  | 1        |

| MACAR Smem[, B]             | B = rnd(B + Smem * A(32-16)),<br>T = Smem               | 1                 | 1                  | 3A, 3B   |

| MACAR T, src[, dst]         | dst = rnd(src + T * A(32-16))                           | 1                 | 1                  | 1        |

| MACD Smem, pmad, src        | src = src + Smem * pmad,<br>T = Smem, (Smem + 1) = Smem | 2                 | 3                  | 23A, 23B |

| MACP Smem, pmad, src        | src = src + Smem * pmad,<br>T = Smem                    | 2                 | 3                  | 22A, 22B |

| MACSU Xmem, Ymem, src       | src = src + uns(Xmem) * Ymem,<br>T = Xmem               | 1                 | 1                  | 7        |

| MAS Smem, src               | src = src - T * Smem                                    | 1                 | 1                  | 3A, 3B   |

| MASR Smem, src              | src = rnd(src - T * Smem)                               | 1                 | 1                  | 3A, 3B   |

| MAS Xmem, Ymem, src[, dst]  | dst = src - Xmem * Ymem,<br>T = Xmem                    | 1                 | 1                  | 7        |

| MASR Xmem, Ymem, src[, dst] | dst = rnd(src - Xmem * Ymem),<br>T = Xmem               | 1                 | 1                  | 7        |

| MASA Smem[, B]              | B = B — Smem * A(32-16),<br>T = Smem                    | 1                 | 1                  | 3A, 3B   |

| MASA T, src[, dst]          | dst = src - T * A(32-16)                                | 1                 | 1                  | 1        |

| MASAR T, src[, dst]         | dst = rnd(src - T * A(32-16))                           | 1                 | 1                  | 1        |

| SQURA Smem, src             | src = src + Smem * Smem,<br>T = Smem                    | 1                 | 1                  | 3A, 3B   |

| SQURS Smem, src             | src = src — Smem * Smem,<br>T = Smem                    | 1                 | 1                  | 3A, 3B   |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 9 – Двойные (с 32-разрядным операндом) инструкции

| Синтаксис             | Выражение                                                                                                                                                                    | Cл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|--------|

| DADD Lmem, src[, dst] | Если C16 = 0<br>dst = Lmem + src<br>Если C16 = 1<br>dst(39-16) = Lmem(31-16) + src(31-dst(15-0) = Lmem(15-0) + src(15-0)                                                     |                   | 1                  | 9A, 9B |

| DADST Lmem, dst       | Если $C16 = 0$<br>dst = Lmem + (T << 16 + T)<br>Если $C16 = 1$<br>dst(39-16) = Lmem(31-16) + T<br>dst(15-0) = Lmem(15-0) - T                                                 | 1                 | 1                  | 9A, 9B |

| DRSUB Lmem, src       | Если C16 = 0<br>src = Lmem — src<br>Если C16 = 1<br>src(39-16) = Lmem(31-16) — src(3<br>src(15-0) = Lmem(15-0) — src(15-0                                                    |                   | 1                  | 9A, 9B |

| DSADT Lmem, dst       | Если $C16 = 0$<br>$dst = Lmem \longrightarrow (T << 16 + T)$<br>Если $C16 = 1$<br>$dst(39-16) = Lmem(31-16) \longrightarrow T$<br>dst(15-0) = Lmem(15-0) + T                 | 1                 | 1                  | 9A, 9B |

| DSUB Lmem, src        | Если C16 = 0<br>src = src — Lmem<br>Если C16 = 1<br>src(39-16) = src(31-16) — Lmem(3<br>src(15-0) = src(15-0) — Lmem(15-0                                                    |                   | 1                  | 9A, 9B |

| DSUBT Lmem, dst       | Если $C16 = 0$<br>$dst = Lmem \longrightarrow (T << 16 + T)$<br>Если $C16 = 1$<br>$dst(39-16) = Lmem(31-16) \longrightarrow T$<br>$dst(15-0) = Lmem(15-0) \longrightarrow T$ | 1                 | 1                  | 9A, 9B |

<sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Lmem* добавляется еще 1 слово и один цикл.

Таблица 10 – Инструкции для специфических применений

| Синтаксис             | Выражение                                              | Сл.1) | Цкл. <sup>1)</sup> | Класс    |

|-----------------------|--------------------------------------------------------|-------|--------------------|----------|

| ABDST Xmem, Ymem      | B = B +  A(32-16) <br>A = (Xmem - Ymem) << 16          | 1     | 1                  | 7        |

| ABS src[, dst]        | dst =  src                                             | 1     | 1                  | 1        |

| CMPL src[, dst]       | dst = ∼src                                             | 1     | 1                  | 1        |

| DELAY Smem            | (Smem + 1) = Smem                                      | 1     | 1                  | 24A, 24B |

| EXP src               | T = кол-во знаковых разрядов (src) — 3                 | 3 1   | 1                  | 1        |

| FIRS Xmem, Ymem, pmad | B = B + A * pmad<br>A = (Xmem + Ymem) << 16            | 2     | 3                  | 8        |

| LMS Xmem, Ymem        | B = B + Xmem * Ymem<br>$A = A + Xmem << 16 + 2^{15}$   | 1     | 1                  | 7        |

| MAX dst               | dst = max(A, B)                                        | 1     | 1                  | 1        |

| MIN dst               | dst = min(A, B)                                        | 1     | 1                  | 1        |

| NEG src[, dst]        | dst = -src                                             | 1     | 1                  | 1        |

| NORM src[, dst]       | $dst = src \ll TS$<br>dst = norm(src, TS)              | 1     | 1                  | 1        |

| POLY Smem             | B = Smem << 16<br>A = rnd(A(32-16) * T + B)            | 1     | 1                  | 3A, 3B   |

| RND src[, dst]        | $dst = src + 2^{15}$                                   | 1     | 1                  | 1        |

| SAT src               | насыщение(src)                                         | 1     | 1                  | 1        |

| SQDST Xmem, Ymem      | B = B + A(32-16) * A(32-16)<br>A = (Xmem - Ymem) << 16 | 1     | 1                  | 7        |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

#### 2.2 Логические операции

В этом подразделе собраны инструкции логических операций. В таблицах с 11 по 15 приводятся инструкции, разделенные на следующие функциональные группы:

- инструкции "И" таблица 11;

- инструкции "ИЛИ" таблица 12;

- инструкции "Исключающее ИЛИ" таблица 13;

- инструкции сдвига таблица 14;

- инструкции тестирования таблица 15.

Таблица 11 – Инструкции "И"

| Синтаксис                   | Выражение                | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|-----------------------------|--------------------------|-------------------|--------------------|----------|

| AND Smem, src               | src = src & Smem         | 1                 | 1                  | 3A, 3B   |

| AND #lk[, SHFT], src[, dst] | dst = src & #lk << SHFT  | 2                 | 2                  | 2        |

| AND #lk, 16, src[, dst]     | dst = src & #lk << 16    | 2                 | 2                  | 2        |

| AND src[, SHIFT][, dst]     | dst = dst & src << SHIFT | 1                 | 1                  | 1        |

| ANDM #lk, Smem              | Smem = Smem & #lk        | 2                 | 2                  | 18A, 18B |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 12 – Инструкции "ИЛИ"

| Синтаксис                  | Выражение                      | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|----------------------------|--------------------------------|-------------------|--------------------|----------|

| OR Smem, src               | $src = src \mid Smem$          | 1                 | 1                  | 3A, 3B   |

| OR #lk[, SHFT], src[, dst] | $dst = src \mid \#lk << SHFT$  | 2                 | 2                  | 2        |

| OR #lk, 16, src[, dst]     | dst = src   #lk << 16          | 2                 | 2                  | 2        |

| OR src[, SHIFT][, dst]     | $dst = dst \mid src \ll SHIFT$ | 1                 | 1                  | 1        |

| ORM #lk, Smem              | $Smem = Smem \mid \#lk$        | 2                 | 2                  | 18A, 18B |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 13 – Инструкции "Исключающее ИЛИ"

| Выражение        | Сл. <sup>1)</sup>                                                                                                        | Цкл. <sup>1)</sup>                                       | Класс                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|

| src – src ^ Smem | 1                                                                                                                        | 1                                                        | 3A, 3B                                                           |

|                  | 2                                                                                                                        | 2                                                        | 2                                                                |

|                  | 2                                                                                                                        | 2                                                        | 2                                                                |

|                  | 1                                                                                                                        | 1                                                        | 1                                                                |

|                  | 2                                                                                                                        | 2                                                        | 18A, 18B                                                         |

|                  | Bыражение  src = src ^ Smem  dst = src ^ #lk << SHFT  dst = src ^ #lk << 16  dst = dst ^ src << SHIFT  Smem = Smem ^ #lk | src = src ^ Smem       1         dst = src ^ #lk << SHFT | src = src ^ Smem       1       1         dst = src ^ #lk << SHFT |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 14 – Инструкции сдвига

| Синтаксис                | Выражение                                            | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс |

|--------------------------|------------------------------------------------------|-------------------|--------------------|-------|

| ROL src                  | Вращение влево с включением переноса                 | 1                 | 1                  | 1     |

| ROLTC src                | Вращение влево с включением ТС-бита                  | 1                 | 1                  | 1     |

| ROR src                  | Вращение вправо с включением перенос                 | a 1               | 1                  | 1     |

| SFTA src, SHIFT [, dst]  | dst = src << SHIFT {арифметический сдвиг}            | 1                 | 1                  | 1     |

| SFTC src[, SHIFT][, dst] | если $src(31) = src(30)$ ,<br>тогда $src = src << 1$ | 1                 | 1                  | 1     |

| SFTL src, SHIFT [, dst]  | dst = src << SHIFT<br>{логический сдвиг}             | 1                 | 1                  | 1     |

<sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM.

Таблица 15 – Инструкции тестирования

| Синтаксис      | Выражение              | Сл.1) | Цкл. <sup>1)</sup> | Класс  |

|----------------|------------------------|-------|--------------------|--------|

|                |                        |       |                    |        |

| BIT Xmem, BITC | TC = Xmem(15 - BITC)   | 1     | 1                  | 3A     |

| BITF Smem, #lk | TC = (Smem && #lk)     | 2     | 2                  | 6A, 6B |

| BITT Smem      | TC = Smem(15 - T(3-0)) | 1     | 1                  | 3A, 3B |

| CMPM Smem, #lk | TC = (Smem == #lk)     | 2     | 2                  | 6A, 6B |

| CMPR CC, ARx   | Сравнение ARx с AR0    | 1     | 1                  | 1      |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

#### 2.3 Операции управления выполнением программы

В этом подразделе собраны инструкции управления выполнением программы. В таблицах с 16 по 22 приводятся инструкции, разделенные на следующие функциональные группы:

- инструкции переходов таблица 16;

- инструкции вызовов таблица 17;

- инструкции прерываний таблица 18;

- инструкции возвратов таблица 19;

- инструкции повторов таблица 20;

- инструкции работы со стеком таблица 21;

- смешанные инструкции управления выполнением программы таблица 22.

Таблица 16 – Инструкции переходов

| Синтаксис                      | Выражение                                         | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup>                                   | Класс |

|--------------------------------|---------------------------------------------------|-------------------|------------------------------------------------------|-------|

| B[D] pmad                      | PC = pmad(15-0)                                   | 2                 | $4/[2^{2}]$                                          | 29A   |

| BACC[D] src                    | PC = src(15-0)                                    | 1                 | $6/[4^{2)}]$                                         | 30A   |

| BANZ[D] pmad, Sind             | если (Sind $\neq$ 0),<br>тогда PC = pmad(15-0)    | 2                 | $4^{3)}/2^{4)}/$ [2 <sup>2)</sup> ]                  | 29A   |

| BC[D] pmad, cond [, cond [, co | ond ] ] если условие(я),<br>тогда PC = pmad(15-0) | 2                 | 5 <sup>3)</sup> /3 <sup>4)</sup> /[3 <sup>2)</sup> ] | 31A   |

Таблица 17 – Инструкции вызовов

| Синтаксис                        | Выражение                                       | Сл.1) | Цкл. <sup>1)</sup>                                    | Класс |

|----------------------------------|-------------------------------------------------|-------|-------------------------------------------------------|-------|

| CALA[D] src                      | $SP, PC + 1[3^{2)}] = TOS,$<br>PC = src(15-0)   | 1     | 6/[4 <sup>2)</sup> ]                                  | 30B   |

| CALL[D] pmad                     | $$ SP, PC + $2[4^{2)}]$ =TOS<br>PC = pmad(15-0) | 2     | $4/[2^{3}]$                                           | 29B   |

| CC[D] pmad, cond [, cond [, cond | $PC + 2[4^{2}] = TOS,$ $PC = pmad(15-0)$        | 2, 2  | 5 <sup>4</sup> /3 <sup>3</sup> /<br>[3 <sup>2</sup> ] | 31B   |

$<sup>^{1)}</sup>$  Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM.

<sup>&</sup>lt;sup>2)</sup> Условие выполнено.

<sup>3)</sup> Условие невыполнено.

<sup>&</sup>lt;sup>4)</sup> Задержанная инструкция.

<sup>&</sup>lt;sup>2)</sup> Задержанная инструкция.

<sup>3)</sup> Условие невыполнено.

<sup>4)</sup> Условие выполнено.

Таблица 18 – Инструкции прерываний

| Синтаксис | Выражение                                                | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс |

|-----------|----------------------------------------------------------|-------------------|--------------------|-------|

| INTR K    | SP, ++PC = TOS,<br>PC = IPTR(15-7) + K << 2,<br>INTM = 1 | 1                 | 3                  | 35    |

| TRAP K    | SP, ++PC = TOS,<br>PC = IPTR(15-7) + K << 2              | 1                 | 3                  | 35    |

Таблица 19 – Инструкции возвратов

| Синтаксис                     | Выражение                                  | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup>                                   | Класс |

|-------------------------------|--------------------------------------------|-------------------|------------------------------------------------------|-------|

| RC[D] cond [, cond [, cond ]] | если условие(я),<br>тогда PC = TOS, + + SP | 1                 | 5 <sup>2)</sup> /3 <sup>3)</sup> /[3 <sup>4)</sup> ] | 32    |

| RET[D]                        | PC = TOS, + + SP                           | 1                 | 5/[3 <sup>4)</sup> ]                                 | 32    |

| RETE[D]                       | PC = TOS, + + SP, INTM = 0                 | 1                 | 5/[3 <sup>4)</sup> ]                                 | 32    |

| RETF[D]                       | PC = RTT, + + SP, INTM = 0                 | 1                 | 3/[1 <sup>4)</sup> ]                                 | 33    |

<sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM.

Таблица 20 – Инструкции повторов

| Синтаксис     | Выражение                                                       | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс  |

|---------------|-----------------------------------------------------------------|-------------------|--------------------|--------|

| RPT Smem      | Повтор инструкции, RC = Smem                                    | 1                 | 3                  | 5A, 5B |

| RPT #K        | Повтор инструкции, RC = #K                                      | 1                 | 1                  | 1      |

| RPT #lk       | Повтор инструкции, RC = #lk                                     | 2                 | 2                  | 2      |

| RPTB[D] pmad  | Повтор блока, $RSA = PC + 2[4^{2}]$ , $REA = pmad$ , $BRAF = 1$ | 2                 | $4/[2^{2}]$        | 29A    |

| RPTZ dst, #lk | Повтор инструкции, $RC = \#lk$ , $dst = 0$                      | 2                 | 2                  | 2      |

<sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

<sup>2)</sup> Условие выполнено.

<sup>3)</sup> Условие невыполнено.

<sup>4)</sup> Задержанная инструкция.

<sup>&</sup>lt;sup>2)</sup> Задержанная инструкция.

Таблица 21 – Инструкции работы со стеком

| Синтаксис | Выражение          | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|-----------|--------------------|-------------------|--------------------|----------|

| FRAME K   | SP = SP + K        | 1                 | 1                  | 1        |

| POPD Smem | Smem = TOS, + + SP | 1                 | 1                  | 17A, 17B |

| POPM MMR  | MMR = TOS, + + SP  | 1                 | 1                  | 17A      |

| PSHD Smem | SP, Smem = TOS     | 1                 | 1                  | 16A, 16B |

| PSHM MMR  | SP, MMR = TOS      | 1                 | 1                  | 16A      |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 22 – Смешанные инструкции управления выполнением программы

| Синтаксис                     | Выражение                                                                                                                                                                  | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|-------|

| IDLE K                        | idle(k)                                                                                                                                                                    | 1                 | 4                  | 36    |

| MAR Smem                      | Если СМРТ = 0, тогда модифицировать $ARx$ Если СМРТ = 0 и $ARx \neq AR0$ , тог модифицировать $ARx$ , $ARP = x$ Если СМРТ = 0 и $ARx = AR0$ , тог модифицировать $AR(ARP)$ |                   | 1                  | 1, 2  |

| NOP                           | нет операции                                                                                                                                                               | 1                 | 1                  | 1     |

| RESET                         | программный сброс                                                                                                                                                          | 1                 | 3                  | 35    |

| RSBX N, SBIT                  | STN(SBIT) = 0                                                                                                                                                              | 1                 | 1                  | 1     |

| SSBX N, SBIT                  | STN(SBIT) = 1                                                                                                                                                              | 1                 | 1                  | 1     |

| XC n, cond [, cond [, cond ]] | если условие(я), тогда выполните следующие $n$ инструкций; $n=1$ или $2$                                                                                                   | . 1               | 1                  | 1     |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

#### 2.4 Операции загрузки и сохранения

В этом подразделе собраны инструкции загрузки и сохранения. В таблицах с 23 по 30 приводятся инструкции, разделенные на следующие функциональные группы:

- инструкции загрузки таблица 23;

- инструкции сохранения таблица 24;

- инструкции условного сохранения таблица 25;

- параллельные инструкции загрузки и сохранения таблица 26;

- параллельные инструкции загрузки и умножения таблица 27;

- параллельные инструкции сохранения и сложения/вычитания таблица 28;

- параллельные инструкции сохранения и умножения таблица 29;

- смешанные инструкции загрузки и сохранения таблица 30.

Таблица 23 – Инструкции загрузки

| Синтаксис             | Выражение                      | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|-----------------------|--------------------------------|-------------------|--------------------|----------|

| DLD Lmem, dst         | dst = Lmem                     | 1                 | 1                  | 9A, 9B   |

| LD Smem, dst          | dst = Smem                     | 1                 | 1                  | 3A, 3B   |

| LD Smem, TS, dst      | dst = Smem << TS               | 1                 | 1                  | 3A, 3B   |

| LD Smem, 16, dst      | $dst = Smem \ll 16$            | 1                 | 1                  | 3A, 3B   |

| LD Smem[, SHIFT], dst | dst = Smem << SHIFT            | 2                 | 2                  | 4A, 4B   |

| LD Xmem, SHFT, dst    | dst = Xmem << SHFT             | 1                 | 1                  | 3A       |

| LD #K, dst            | dst = #K                       | 1                 | 1                  | 1        |

| LD #lk[, SHFT], dst   | $dst = \#lk \ll SHFT$          | 2                 | 2                  | 2        |

| LD #lk, 16, dst       | dst = #lk << 16                | 2                 | 2                  | 2        |

| LD src, ASM[, dst]    | $dst = src \ll ASM$            | 1                 | 1                  | 1        |

| LD src[, SHIFT], dst  | $dst = src \ll SHIFT$          | 1                 | 1                  | 1        |

| LD Smem, T            | T = Smem                       | 1                 | 1                  | 3A, 3B   |

| LD Smem, DP           | DP = Smem(8-0)                 | 1                 | 3                  | 5A, 5B   |

| LD #k9, DP            | DP = #k9                       | 1                 | 1                  | 1        |

| LD #k5, ASM           | ASM = #k5                      | 1                 | 1                  | 1        |

| LD #k3, ARP           | ARP = #k3                      | 1                 | 1                  | 1        |

| LD Smem, ASM          | ASM = Smem(4-0)                | 1                 | 1                  | 3A, 3B   |

| LDM MMR, dst          | dst = MMR                      | 1                 | 1                  | 3A       |

| LDR Smem, dst         | dst = rnd(Smem)                | 1                 | 1                  | 3A, 3B   |

| LDU Smem, dst         | dst = uns(Smem)                | 1                 | 1                  | 3A, 3B   |

| LTD Smem              | T = Smem,<br>(Smem + 1) = Smem | 1                 | 1                  | 24A, 24B |

<sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Lmem* или *Smem* добавляется еще 1 слово и один цикл.

Таблица 24 – Инструкции сохранения

| Синтаксис              | Выражение                  | Cл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|------------------------|----------------------------|-------------------|--------------------|----------|

| DST src, Lmem          | Lmem = src                 | 1                 | 2                  | 13A, 13B |

| ST T, Smem             | Smem = T                   | 1                 | 1                  | 10A, 10B |

| ST TRN, Smem           | Smem = TRN                 | 1                 | 1                  | 10A, 10B |

| ST #lk, Smem           | Smem = #lk                 | 2                 | 2                  | 12A, 12B |

| STH src, Smem          | Smem = src << 16           | 1                 | 1                  | 10A, 10B |

| STH src, ASM, Smem     | Smem = src << (ASM - 16)   | 1                 | 1                  | 10A, 10B |

| STH src, SHFT, Xmem    | Xmem = src << (SHFT - 16)  | 1                 | 1                  | 10A      |

| STH src[, SHIFT], Smem | Smem = src << (SHIFT — 16) | 2                 | 2                  | 11A, 11B |

| STL src, Smem          | Smem = src                 | 1                 | 1                  | 10A, 10B |

| STL src, ASM, Smem     | Smem = src << ASM          | 1                 | 1                  | 10A, 10B |

| STL src, SHFT, Xmem    | $Xmem = src \ll SHFT$      | 1                 | 1                  | 10A, 10B |

| STL src[, SHIFT], Smem | Smem = src << SHIFT        | 2                 | 2                  | 11A, 11B |

| STLM src, MMR          | MMR = src                  | 1                 | 1                  | 10A      |

| STM #lk, MMR           | MMR = #lk                  | 2                 | 2                  | 12A      |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Lmem* или *Smem* добавляется еще 1 слово и один цикл.

Таблица 25 – Инструкции условного сохранения

| Синтаксис             | Выражение                                                                             | Cл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|-----------------------|---------------------------------------------------------------------------------------|-------------------|--------------------|----------|

| CMPS src, Smem        | Eсли = $src(31-16) > src(15-0)тогда Smem = src(31-16)Eсли = src(31-16) \le src(15-0)$ | 1                 | 1                  | 10A, 10B |

|                       | тогда Smem = $src(15-0)$                                                              |                   |                    |          |

| SACCD src, Xmem, cond | Если (условие)<br>Xmem = src << (ASM — 16)                                            | 1                 | 1                  | 15       |

| SRCCD Xmem, cond      | Если (условие)<br>Xmem = BRC                                                          | 1                 | 1                  | 15       |

| STRCD Xmem, cond      | Если (условие)<br>Хтет = Т                                                            | 1                 | 1                  | 15       |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

Таблица 26 – Параллельные инструкции загрузки и сохранения

| Синтаксис                       | Выражение                                       | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс |

|---------------------------------|-------------------------------------------------|-------------------|--------------------|-------|

| ST src, Ymem<br>   LD Xmem, dst | Ymem = src << (ASM — 16)<br>   dst = Xmem << 16 | 1                 | 1                  | 14    |

| ST src, Ymem<br>   LD Xmem, T   | Ymem = src << (ASM — 16)<br>   T = Xmem         | 1                 | 1                  | 14    |

Таблица 27 – Параллельные инструкции загрузки и умножения

| Синтаксис                          | Выражение                                                                             | Сл.1) | Цкл. <sup>1)</sup> | Класс |

|------------------------------------|---------------------------------------------------------------------------------------|-------|--------------------|-------|

| LD Xmem, dst<br>   MAC Ymem, dst_  | $\begin{array}{l} dst = Xmem << 16 \\ \parallel dst\_ = dst\_ + T * Ymem \end{array}$ | 1     | 1                  | 7     |

| LD Xmem, dst<br>   MACR Ymem, dst_ | $dst = Xmem << 16$ $\parallel dst = rnd(dst + T * Ymem)$                              | 1     | 1                  | 7     |

| LD Xmem, dst<br>   MAS Ymem, dst_  | $dst = Xmem << 16$ $\parallel dst\_ = dst\ T * Ymem$                                  | 1     | 1                  | 7     |

| LD Xmem, dst<br>   MASR Ymem, dst_ | $dst = Xmem << 16$ $\parallel dst = rnd(dst - T * Ymem)$                              | 1     | 1                  | 7     |

<sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM.

Таблица 28 – Параллельные инструкции сохранения и сложения/вычитания

| Синтаксис     | Выражение                          | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс |

|---------------|------------------------------------|-------------------|--------------------|-------|

| ST src, Ymem  | Ymem = src << (ASM - 16)           | 1                 | 1                  | 14    |

| ADD Xmem, dst | $\parallel dst = dst_+ Xmem << 16$ |                   |                    |       |

| ST src, Ymem  | Ymem = src << (ASM - 16)           | 1                 | 1                  | 14    |

| SUB Xmem, dst | T = (Xmem << 16) - dst             |                   |                    |       |

<sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM.

Таблица 29 – Параллельные инструкции сохранения и умножения

| Синтаксис                         | Выражение                                                            | Сл.1) | Цкл. <sup>1)</sup> | Класс |

|-----------------------------------|----------------------------------------------------------------------|-------|--------------------|-------|

| ST src, Ymem<br>   MAC Xmem, dst  | Ymem = src << (ASM — 16)<br>   dst = dst + T * Xmem                  | 1     | 1                  | 14    |

| ST src, Ymem<br>   MACR Xmem, dst | $Ymem = src << (ASM - 16)$ $\parallel dst = rnd(dst + T * Xmem)$     | 1     | 1                  | 14    |

| ST src, Ymem<br>   MAS Xmem, dst  | Ymem = src << (ASM — 16)<br>   dst = dst — T * Xmem                  | 1     | 1                  | 14    |

| ST src, Ymem<br>   MASR Xmem, dst | Ymem = $src \ll (ASM - 16)$<br>$\parallel dst = rnd(dst - T * Xmem)$ | 1     | 1                  | 14    |

| ST src, Ymem<br>   MPY Xmem, dst  | Ymem = src << (ASM — 16)<br>   dst = T * Xmem                        | 1     | 1                  | 14    |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM.

Таблица 30 – Смешанные инструкции загрузки и сохранения

| Синтаксис       | Выражение   | Сл. <sup>1)</sup> | Цкл. <sup>1)</sup> | Класс    |

|-----------------|-------------|-------------------|--------------------|----------|

| MVDD Xmem, Ymem | Ymem = Xmem | 1                 | 1                  | 14       |

| MVDK Smem, dmad | dmad = Smem | 2                 | 2                  | 19A, 19B |

| MVDM dmad, MMR  | MMR = dmad  | 2                 | 2                  | 19A      |

| MVDP Smem, pmad | pmad = Smem | 2                 | 4                  | 20A, 20B |

| MVKD dmad, Smem | Smem = dmad | 2                 | 2                  | 19A, 19B |

| MVMD MMR, dmad  | dmad = MMR  | 2                 | 2                  | 19A      |

| MVMM MMRx, MMRy | MMRy = MMRx | 1                 | 1                  | 1        |

| MVPD pmad, Smem | Smem = pmad | 2                 | 3                  | 21A, 21B |

| PORTR PA, Smem  | Smem = PA   | 2                 | 2                  | 27A, 27B |

| PORTW Smem, PA  | PA = Smem   | 2                 | 2                  | 28A, 28B |

| READA Smem      | Smem = A    | 1                 | 5                  | 25A, 25B |

| WRITA Smem      | A = Smem    | 1                 | 5                  | 26A, 26B |

<sup>&</sup>lt;sup>1)</sup> Значения в столбцах Сл. (количество слов) и Цкл. (количество циклов) приведены для случая, когда используется DARAM. При использовании косвенной адресации с длинным смещением или абсолютной адресации с *Smem* добавляется еще 1 слово и один цикл.

#### 2.5 Повтор однократной инструкции

В процессоре 1867ВМ8Т предусмотрены инструкции повтора. Инструкция, следующая за инструкцией повтора с операндом N, будет выполнена N+1 раз. Это значение сохраняется в 16-разрядном регистре повтора (RC). Регистр RC программно недоступен. Он загружается только инструкциями повтора. Однократная инструкция может быть выполнена максимально 65 536 раз. При повторе инструкции происходит автоматическая инкрементация абсолютного адреса программы или данных.

При активизации повтора инструкции все прерывания, включая NMI# (но не RESET#!) запрещаются до окончания цикла повтора. При этом процессор реагирует на сигнал HOLD# во время цикла повтора – реакция зависит от состояния HM бита в регистре \$T1

Функция повтора может применяться к различным инструкциям, таким как, умножение с накоплением и блочное перемещение данных, чтобы увеличить скорость выполнения этих инструкций. Эти инструкции, приведенные в таблице 31, являются многоцикловыми при обычном однократном выполнении, но в режиме повтора становятся эффективно одноцикловыми после выполнения первой итерации.

Таблица 31 – Многоцикловые инструкции, становящиеся одноцикловыми в режиме повтора

| Инструкция                                             | Описание                                                 | #Цкл. <sup>1)</sup> |  |

|--------------------------------------------------------|----------------------------------------------------------|---------------------|--|

| FIRS                                                   | Симметричный КИХ-фильтр                                  | 3                   |  |

| MACD                                                   | Умножить и поместить результат в аккумулятор с задержкой | 3                   |  |

| MACP                                                   | Умножить и поместить результат в аккумулятор             | 3                   |  |

| MVDK                                                   | Перемещение внутри памяти данных                         | 2                   |  |

| MVDM                                                   | Перемещение из памяти данных в MMR                       | 2                   |  |