В статье представлен новый отечественный 8-разрядный микроконтроллер (МК) 1882ВМ1Т, разработанный в АО «НИИЭТ» на базе архитектуры и системы команд MCS-51. Эта микросхема является развитием популярной линейки МК серии 1882 (1882ВЕ53У и др.), однако по сравнению с серийно выпускаемыми изделиями она имеет ряд неоспоримых преимуществ. Прежде всего, речь идет о наличии большого количества необходимых разработчику аппаратуры интерфейсов, портов и других периферийных устройств. Это, в частности, встроенная система защиты данных — блок кодирования по ГОСТ 28147-89. МК 1882ВМ1Т имеет в своем составе блок 16-разрядной арифметики MDU, а также встроенную энергонезависимую память программ и данных значительно увеличенного объема. Напряжение питания микросхемы составляет 3,3 В ±10 %.

В настоящее время большинство применяемых в мировой электронике МК основано на 8-разрядной архитектуре процессоров [1]. При этом наиболее широко используемой 8-разрядной архитектурой является MCS-51 (8051), разработанная Intel в 80-х гг. прошлого столетия. Эта архитектура до сих пор популярна среди разработчиков аппаратуры, поскольку она проста в использовании и обеспечена множеством доступных программных средств разработки. Кроме того, 8-разрядные МК с архитектурой MCS-51 поставляют на рынок многие производители.

В отечественной электронной отрасли разработкой и производством 8-разрядных МК на базе процессорного ядра MCS-51 занимается АО «НИИЭТ». В настоящее время НИИЭТ выпускает 6 типов МК с такой архитектурой, в т.ч. два радиационно стойких МК — 1830ВЕ32У и 1830ВЕ32АУ. Наибольшей популярностью среди этой группы МК пользуется 1882ВЕ53У внутрисистемно программируемый 8-разрядный МК со встроенной Flash-памятью программ 12 к Ч 8 бит и тактовой частотой 24 МГц. В состав МК входят также встроенная память данных 2 к Ч 8 бит (типа EEPROM), последовательный порт ввода/вывода UART, последовательный периферийный интерфейс SPI, три 16-разрядных таймера-счетчика, сторожевой таймер WDT и регистровое ОЗУ 256 Ч 8 бит.

В 2013 г. в АО «НИИЭТ» закончена разработка и освоено производство нового мультиинтерфейсного МК 1882ВМ1Т («Сложность-2»), который по своим характеристикам значительно превосходит своего предшественника — 1882ВЕ53У.

МК 1882ВМ1Т имеет в своем составе два вида встроенной энергонезависимой памяти — ПЗУ программ типа Flash объемом 32 кбайт (у 1882ВЕ53У — 12 кбайт) и ПЗУ данных типа EEPROM объемом 4 кбайт (у 1882ВЕ53У — 2 кбайт), последовательные интерфейсы SPI (два), I2C, LIN, последовательный интерфейс по ГОСТ Р 52070-2003 (MIL-STD-1553), два последовательных порта UART, а также блок кодирования по ГОСТ 28147-89.

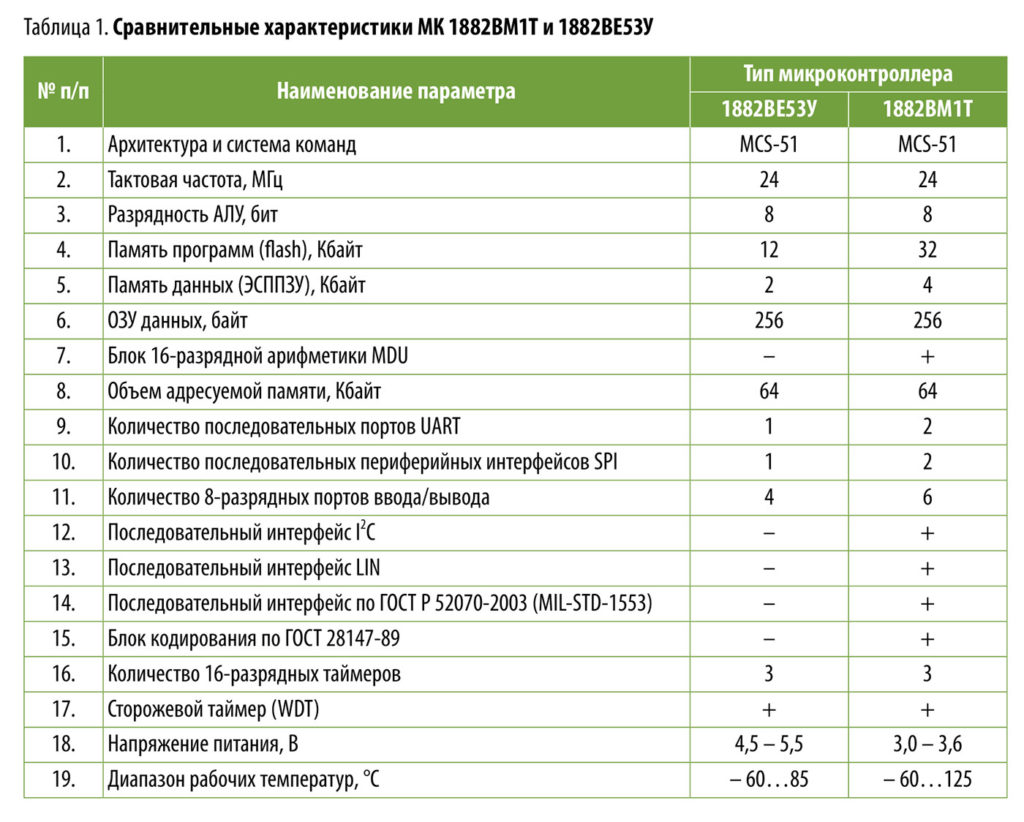

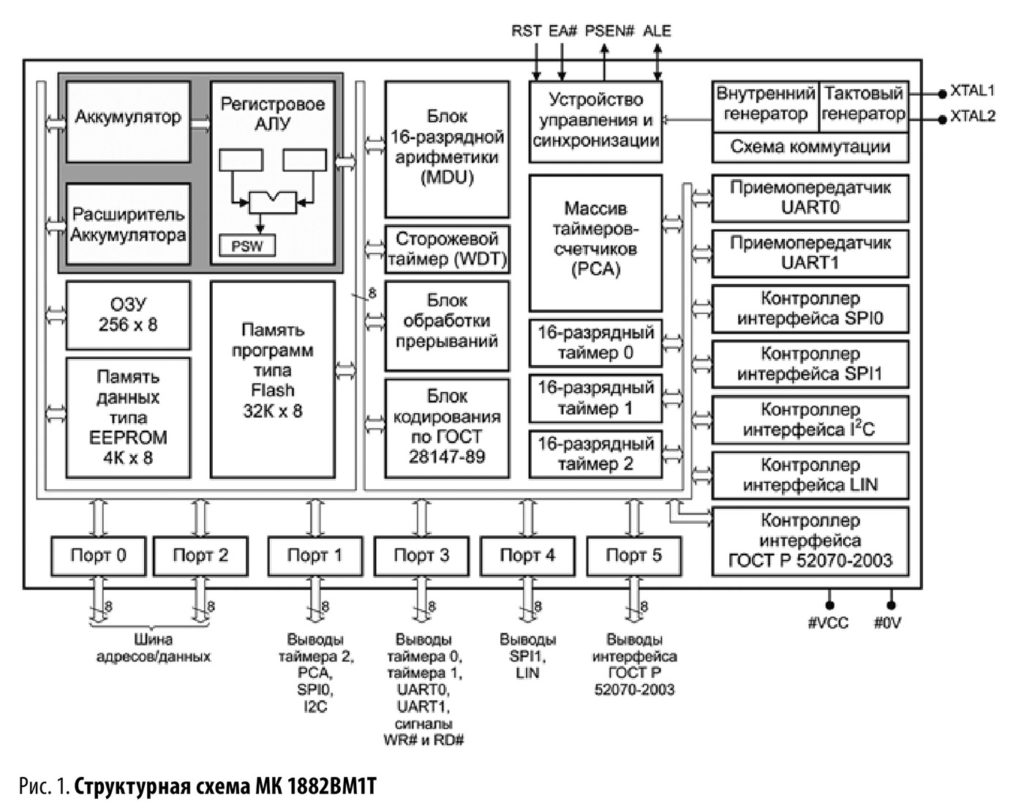

Сравнительные характеристики МК 1882ВМ1Т и 1882ВЕ53У представлены в таблице 1. Как и 1882ВЕ53У, МК 1882ВМ1Т предназначен для применения во встроенных цифровых системах управления и обработки данных и для сопряжения между интерфейсами различных типов в сетях обмена информацией. Наличие в МК 1882ВМ1Т такой важной функции как встроенная аппаратная реализация алгоритмов защиты данных по ГОСТ 28147-89 позволяет использовать его для управления внешними периферийными устройствами (АЦП, ЦАП, карточки памяти и т.д.) по защищенным каналам связи.

Технические характеристики МК 1882ВМ1Т

Как уже отмечалось, микросхема 1882ВМ1Т представляет собой мультиинтерфейсный 8-разрядный МК (периферийный сопроцессор) на базе архитектуры MCS-51 (8051) со встроенной аппаратной реализацией алгоритмов кодирования/декодирования информации.

Его основными особенностями являются:

– 8-разрядное процессорное ядро, оптимизированное для приложений управления;

– поддержка ускоренного режима работы ядра с уменьшенным временем выполнения команд;

– наличие встроенной перепрограммируемой памяти программ типа Flash и встроенной памяти данных типа EEPROM с поддержкой как параллельного, так и последовательного побайтного и пословного внутрисистемного программирования (ISP) посредством последовательного интерфейса SPI;

– три уровня защиты памяти программ;

– возможность задания коэффициента деления внутренней тактовой частоты;

– контроллер прерываний с четырьмя уровнями приоритетов;

– возможность выполнения арифметических операций над 16-разрядными операндами благодаря наличию встроенного блока MDU;

– возможность работы на пониженной мощности в режиме холостого хода (Idle) и в режиме пониженного энергопотребления (Power Down) с выходом из режимов по прерыванию;

– поддержка большого количества протоколов обмена (см. табл. 1).

Микросхема обеспечивает работу с внешней тактовой частотой до 24 МГц при включенном внутреннем делителе на два и до 12 МГц при выключенном делителе.

На рисунке 1 приведена структурная схема МК 1882ВМ1Т. основным блоком микроконтроллера является 8-разрядное ядро, в состав которого входит регистровое АЛУ, регистр аккумулятора, регистр расширителя аккумулятора и регистр слова состояния процессора.

В состав МК входит, как уже отмечалось, блок 16-разрядной арифметики (блок умножения и деления), наличие которого позволяет использовать микроконтроллер в приложениях управления в реальном масштабе времени, требующих быстрых математических вычислений. В составе МК имеется блок обработки прерываний, сторожевой таймер, таймеры-счетчики, а также устройство управления и синхронизации, массив таймеров-счетчиков (PCA) и генератор тактового сигнала. Для подключения кварцевого резонатора к тактовому генератору используются выводы XTAL1 и XTAL2.

Периферия микроконтроллера

Периферия МК 1882ВМ1Т представлена приемопередатчиками типа UART, модулями последовательных интерфейсов SPI, I2C, LIN, последовательным интерфейсом ГОСТ Р 52070-2003 и шестью двунаправленными портами ввода/вывода.

Через два идентичных универсальных асинхронных приемопередатчика UART0 и UART1 с поддержкой обнаружения ошибок посылки и автоматическим распознаванием адреса осуществляется прием и передача информации, представленной последовательным кодом в полном дуплексном режиме обмена. В состав приемопередатчика входят принимающий и передающий сдвиговые регистры (недоступные программно), а также специальный буферный регистр SBUFХ для записи данных для передачи и чтения полученных данных.

Последовательный периферийный интерфейс SPI предназначен для быстрого синхронного побайтного обмена информацией между МК и периферийными устройствами или между двумя МК. Четырехпроводной интерфейс SPI организуется по принципу «мастер-ведомый», т.е. между одним ведущим и одним или несколькими ведомыми устройствами, не требует дополнительного оборудования для подключения SPI-совместимых устройств и имеет широкие возможности для конфигурирования. В состав МК 1882ВМ1Т входят два идентичных модуля, реализующих поддержку интерфейса SPI.

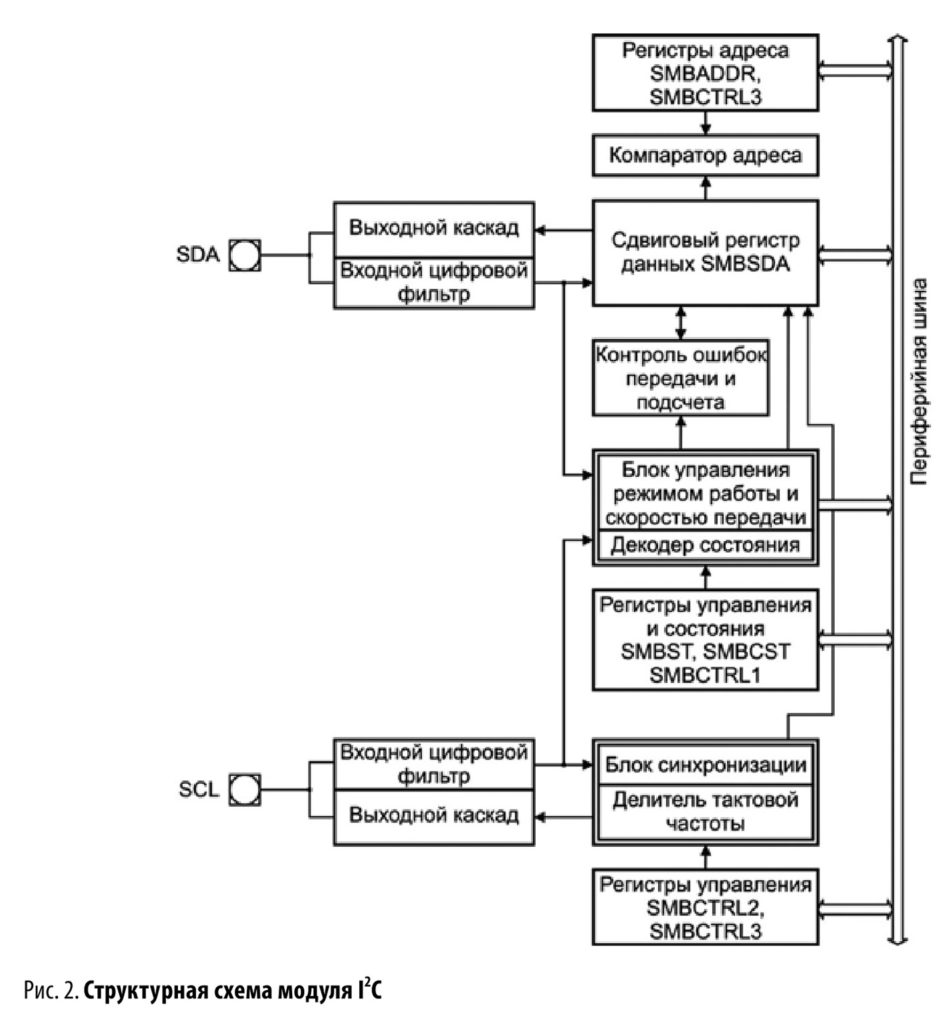

Контроллер интерфейса I2C (модуль I2C) обеспечивает полную поддержку двухпроводного последовательного синхронного интерфейса I2C/SMBus. Результат такой совместимости — легкое соединение со многими запоминающими устройствами и устройствами ввода/вывода, включая EEPROM, SRAM, счетчики, АЦП, ЦАП, периферийные устройства. Структурная схема модуля I2C приведена на рисунке 2.

Ниже перечислены функциональные возможности контроллера интерфейса (модуля) I2C:

– совместимость с протоколами SMBUS 1.1, SMBUS 2.0, ACCESS.BUS, I2C 2.1;

– поддержка скоростного/стандартного (FS) и высокоскоростного (HS) режимов;

– программирование действий «мастера-ведомого»;

– возможность подключения к шине нескольких ведущих устройств, т.е.

поддержка режима «Мультимастер» (ММ);

– один программно задаваемый адрес;

– 7 – или 10-разрядная адресация ведомого;

– поддержка адреса общего вызова.

К числу особых возможностей SMBUS относятся: – отслеживание времени простоя линии SCL;

– наличие функции отслеживания ошибок в пакетах данных (PEC) с использованием метода расчета контрольной суммы (CRC);

– поддержка адреса отклика мастера;

– поддержка полинга и контроля прерываний.

Контроллер интерфейса LIN (Local Interconnect Network) представляет собой последовательный коммуникационный протокол, предназначенный для создания локальных сетей обмена данными на коротких расстояниях. Cеть строится из единственного ведущего устройства (мастера) и множества ведомых устройств. Мастер контролирует все процессы, связанные с передачей данных (сообщений) по шине. Ведомые могут реагировать на сообщения мастера или других узлов сети, но отвечать они могут только будучи адресованными мастером. Шина LIN состоит из одного канала, по которому передаются синхросигналы и данные. Физическая среда канала представляет собой однопроводную линию, подключенную через подтягивающий резистор к шине питания. Высокий уровень сигнала на шине является рецессивным и показывает, что шина свободна. Низкий уровень сигнала на шине является доминантным и показывает, что шина занята.

Блок кодирования/декодирования по ГОСТ 28147-89 представляет собой аппаратную реализацию методов кодирования данных на основе алгоритмов указанного ГОСТа. Блок позволяет производить кодирование/декодирование данных (блоками по 8 байт) тремя симметричными методами:

– простой заменой;

– гаммированием;

– гаммированием с обратной связью.

Важным дополнением является возможность блока кодирования формировать на основе исходных данных контрольную комбинацию — так называемую имитовставку (аналог контрольной суммы), которая позволяет создавать дополнительную защиту данных.

Модуль магистрального последовательного интерфейса ГОСТ Р 52070-2003 представляет собой устройство, поддерживающее обмен данными с другими устройствами (контроллерами) посредством последовательного интерфейса (ГОСТ Р 52070-2003). Обеспечивается совместимость со стандартом MIL-STD-1553В.

В заключение несколько слов о программировании МК 1882ВМ1Т. Параллельное и последовательное программирование осуществляется с помощью программатора, при этом последовательное программирование позволяет перепрограммировать устройство внутри пользовательской системы (посредством интерфейса SPI).

Для защиты информации, хранящейся в памяти МК от случайного или преднамеренного считывания или стирания, предусмотрены специальные биты защиты (fuse-биты и lock-биты).

Средства для программирования и отладки

Рекомендованные средства разработки — Keil 8051 Development Tools. Программирование может осуществляться с использованием таких средств как Phyton ChipProg-48, ChipProg-40, ChipProg-ISP,

ChipProg-64. В качестве программно-аппаратного средства можно использовать макетно-отладочную плату КФДЛ.421457.002, разработанную в АО «НИИЭТ».

ЛИТЕРАТУРА

- Джозеф Ю. Переход с 8051-архитектуры на 32-разрядные процессоры // Электронные компоненты № 2, 2011.