А.В. Строгонов

ФГБОУ ВО «Воронежский государственный технический университет»

Аннотация:в статье рассматриваются вопросы разработки учебных процессорных ядер RISC-V с конвейерной архитектурой из работ [1,2] в САПР Altera Quartus Prime Standard Edition 17.1.0 для последующей реализации в базисе ПЛИС серии Cyclone V.

Ключевые слова: процессор, конвейерное ядро, архитектура RISC-V, симуляция, синтез в ПЛИС.

Implementation of the RISC-V processor pipeline core in the CYCLONE V FPGA basis

A.V. Strogonov

Federal State Budgetary Educational Institution of Voronezh region “Voronezh State Technical University”

Annotation: the article discusses the development of RISC-V training processor cores with a pipeline architecture from [1,2] in Altera Quartus Prime Standard Edition 17.1.0 CAD for subsequent implementation in the basis of FPGA Cyclone V

Keywords: processor, pipelined core, RISC-V architecture, simulation, FPGA synthesis

I. ВВЕДЕНИЕ

В России активно ведутся работы над созданием собственных микропроцессорных архитектур на базе открытого стандарта RISC-V. В настоящее время решается вопрос о государственной поддержке открытой архитектуры процессоров RISC-V.

Для подготовки специалистов в области разработки и программирования под архитектуру RISC-V создаются образовательные программы. Например, в университетах, таких как МИФИ и МФТИ, уже проводятся курсы и лекции, посвященные RISC-V. В научных исследованиях проводимых НИЦ «Курчатовский институт» для реализации интерфейсного ядра базового модуля мемристорного нейросинаптического процессора используется процессорное ядро SCR1 (RV32I) RISC-V международной компании Syntacore. Микроконтроллер Hackee на базе ядра SCR1 так же был спроектирован совместно магистрантами НИУ «МИЭТ» и специалистами компании Yadro.

II. ОСОБЕННОСТИ КОНВЕЙЕРНОГО ПРОЦЕССОРНОГО ЯДРА RISC-V

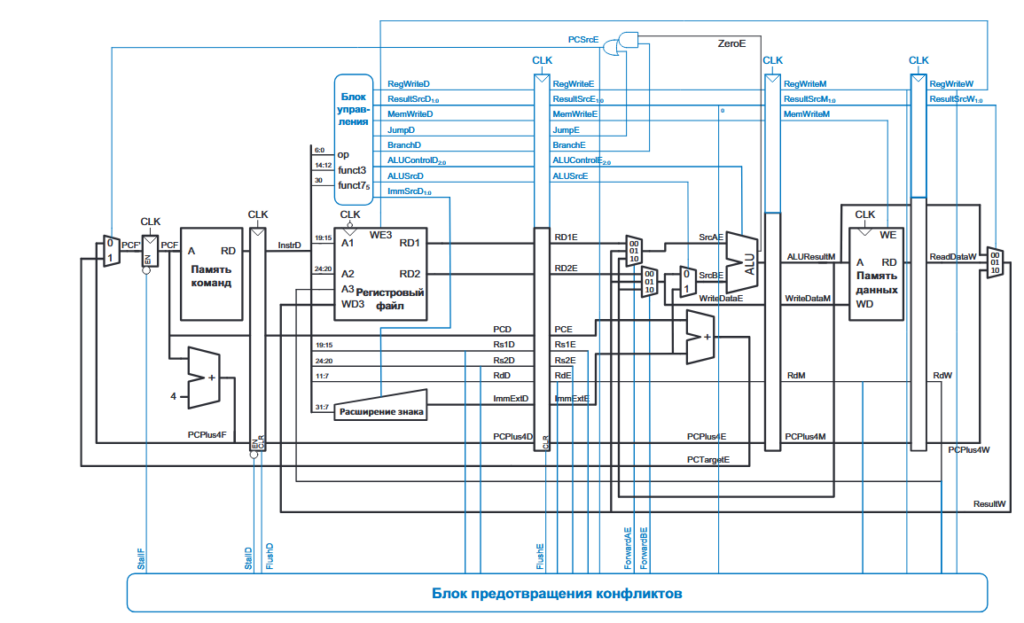

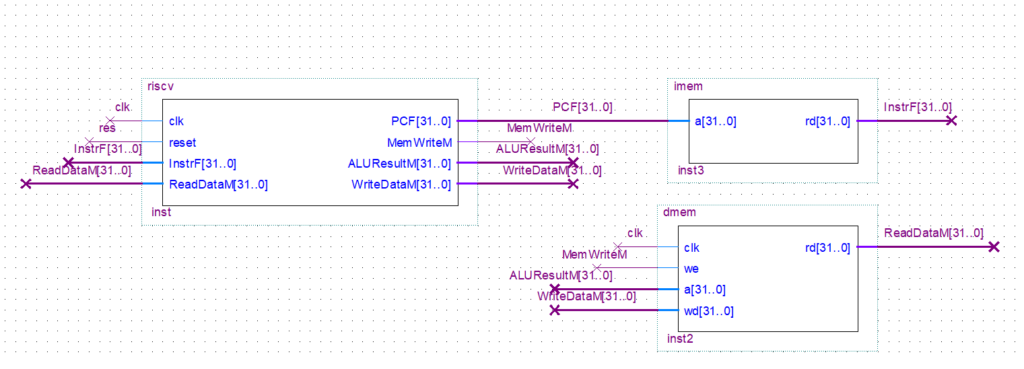

На рисунке 1 показана функциональная схема конвейерного процессорного ядра RISC-V из работы [1]. Конвейерный процессор представляет собой однотактный процессор, разделенный на пять стадий: Fetch (Выборка), Decode (Декодирование), Execute (Выполнение), Memory (Доступ к памяти) и Writeback (Запись результатов). В стадии Fetch процессор читает команду из памяти команд. В стадии Decode процессор читает операнды из регистрового файла и дешифрует команду, чтобы установить управляющие сигналы. В стадии Execute процессор выполняет вычисления в АЛУ. В стадии Memory процессор читает или пишет в память данных, а в стадии Writeback процессор, если нужно, записывает результат в регистровый файл. Конвейерный процессор имеет байпас и блок предотвращения конфликтов при помощи приостановок (hazard) [1,2].

III. СИМУЛЯЦИЯ КОНВЕЙЕРНОГО ПРОЦЕССОРА RISC-V С ПОМОЩЬЮ MODELSIM – INTELFPGASTARTEREDITION

Воспользуемся симулятором ModelSim – Intel FPGA Starter Edition 10.5b идущем в комплекте с САПР Altera Quartus Prime 17.1.0. Все исходные Verilog-коды (testbench, top, riscv, controller, maindec, aludec, datapath, hazard, adder, extend, flopr, flopenr, flopenrc, floprc, mux2, mux3, imem. dmem, alu) конвейерного ядра RISC-V приведены в работе [2], пример 7.25, стр.173-183. Тестовую программу, хранящуюся в ПЗУ (текстовый файл в шестнадцатеричном формате riscvtest.txt), возьмем из работ [1,2] (рис.7.64 и рис.7.65 из работы [1]). Тестируются следующие команды add, sub, and, or, slt, addi, lw, sw, beq, jal. Если тест проходит успешно, то значение 25 (0x19) должно записаться по адресу 100 (0x64).

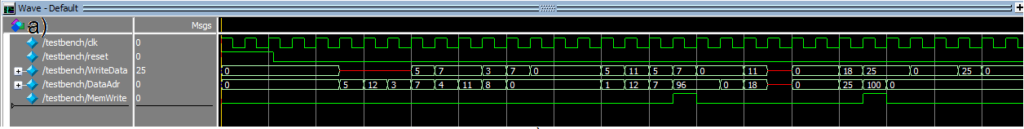

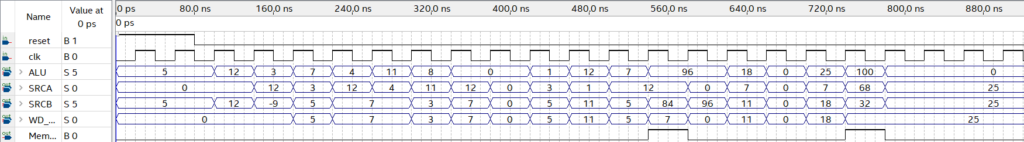

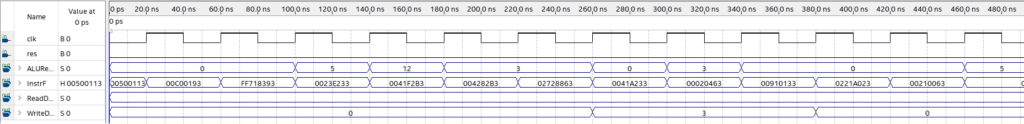

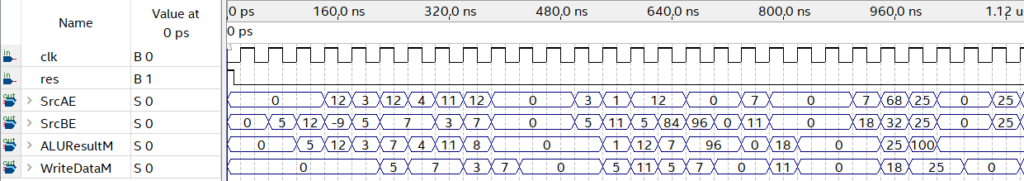

Создадим проект в ModelSim – Intel FPGA. Скомпилируем вышеперечисленные файлы из примера 7.25 работы [2]. Запустим на симуляцию файл testbench.sv. Как видим, конвейерный процессор RISC-V, созданный с помощью исходных кодов из работы [2] “работает из коробки” (рисунок 2, а). Для проверки правильности его работы приведем временные диаграммы однотактного процессорного ядра (рисунок 2, б) из работы [3]. Отличаются они наличием пузырька (bubble) у конвейерного процессора (между значениями 96 и 18 на выходной шине АЛУ, которая подключена к шине ОЗУ DataAdr[31..0] через конвейерный регистр со стадии Memory). Пузырек получается путем обнуления всех управляющих сигналов стадии Execute на время приостановки стадии Decode, так что он не приводит к изменениям архитектурного состояния. Приостановки конвейера ухудшают производительность, поэтому должны использоваться, если по-другому разрешить конфликт данных не удается.

Рисунок 2. Результаты симуляции конвейерного процессора RISC-V в ModelSim Altera (а) и функциональное моделирование однотактного процессора RISC-V в САПР Quartus v17.1.0 из работы [3] (б)

IV. СИНТЕЗ КОНВЕЙЕРНОГО ПРОЦЕССОРА RISC-V С ПОМОЩЬЮ САПР QUARTUS PRIME

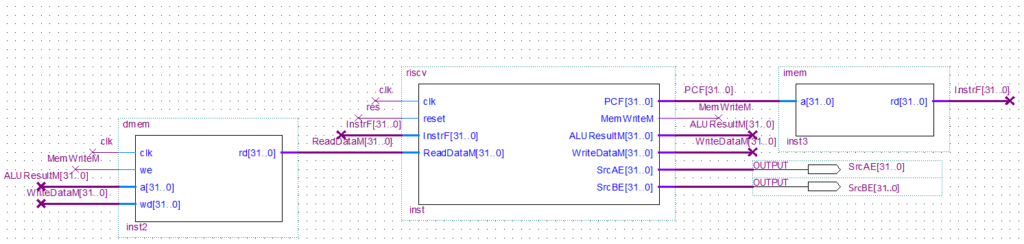

Реализуем это же конвейерное процессорное ядро в базисе ПЛИС Cyclone V в САПР Quartus Prime Standard Edition 17.1.0 (рисунок 3). При этом все настройки синтезатора Quartus остаются по умолчанию (как при первом запуске после инсталляции дистрибутива). Все оригинальные обозначения, принятые в [1,2] по возможности сохранены для исключения разночтения. Рисунок 4 показывает потерю функциональности процессорного ядра при реализации в базисе ПЛИС Cyclone V.

САПР Quartus выполняет синтез кода, оптимизируя его для целевой ПЛИС, что может привести к изменению логики по сравнению с исходным кодом. ModelSim не выполняет синтез, а только симулирует поведение схемы на основе исходного кода. В процессе синтеза Quartus может применять различные оптимизации, что может привести к тому, что симуляция в Quartus после синтеза будет отличаться от симуляции в ModelSim.

Приблизить поведение САПР Quartus к ModelSim возможно отключением оптимизации. В настройках синтеза в Quartus можно отключить оптимизацию, чтобы минимизировать изменения в логике. Это можно сделать через параметры компиляции, такие как Preserve Registers и Preserve Combinational Logic. Однако эти опции доступны в платной версии Quartus Prime Pro Edition. Предотвратить оптимизацию регистров в версиях Lite или Standard Edition возможно использованием специальной директивы (/* synthesis preserve */) в Verilog-коде. Ниже приводится пример с защитой регистра flopenrc от оптимизации. Для восстановления функциональности процессора требуется защитить четыре регистра: flopr; floprc; flopenr и flopenrc.

module flopenrc #(parameter WIDTH = 32)

(input logic clk, reset, clear, en,

input logic [WIDTH-1:0] d,

output reg [WIDTH-1:0] q);

/* synthesis preserve */

always_ff @(posedge clk, posedge reset)

if (reset) q <= 0;

else if (en)

if (clear) q <= 0;

else q <= d;

endmodule

V. КОНВЕЙЕРНЫЙ ПРОЦЕССОР RISC-V С “ЗАПЛАТКОЙ”

В данном разделе дается ответ на вопрос, как поправить ситуацию, если нет под рукой версии САПР Quartus Prime Pro Edition. Изменения коснулись схемы подключения регистрового файла, и потребовалось добавить дополнительный шинный мультиплексор три в один (“заплатка”), который позволяет обойти конвейерный регистр RegW для операции записи данных в регистровый файл. Мультиплексор коммутирует три шины со стадии Memory (ALUResultM[31..0], ReadData[31..0] и PCPlus4M[31..0]) в одну ResultMMM [31..0], которую необходимо подключить к входному порту шины данных регистрового файла wd3[31..0]. В схеме на рис.1 шина ResultW[31..0] со стадии обратной записи результатов (Writeback) подключается к входному порту шины данных регистрового файла wd3 [31..0].

К адресному порту a3[4..0], по которому осуществляется запись в регистровый файл взамен шины RdW[4..0] со стадии Writeback, необходимо подключить шину RdM[4..0] со стадии Memory. На вход we регисторного файла необходимо подать сигнал RegWriteM так же со стадии Memory, а не RegWriteW со стадии Writeback.

Правки необходимо внести в исходные Verilog-коды модулей controller, datapath и riscv из работы [2] пример, 7.25. В качестве примера (рисунок 5) пометим комментарием //Zaplatka и выделим красным цветом изменения в модуле потоковой обработки информации (module datapath).

module datapath(input logic clk, reset,

…

/ Zaplatka

input logic RegWriteM,

input logic [1:0] ResultSrcM,

logic [31:0] ResultMMM;

…

regfile rf(clk, RegWriteM, Rs1D, Rs2D, RdM, ResultMMM, RD1D, RD2D);

//regfile rf(clk, RegWriteW, Rs1D, Rs2D, RdW, ResultW, RD1D, RD2D);

mux3 #(32) muxmmm(ALUResultM, ReadDataM, PCPlus4M, ResultSrcM, ResultMMM);

…

Рисунок 5. Изменения, которые необходимо внести в модуль потоковой обработки информации

На рисунке 6 показан проект конвейерного процессора в САПР Quartus Prime 17.1 с использованием «подправленных» исходных кодов. Сравнивая временные диаграммы на рисунках 2 и 7, видим, что при различных вариантах реализации процессоры работают идентично. В таблице приведены используемые ресурсы ПЛИС серии Cyclone V для двух вариантов реализации процессора (временная модель Slow 1100 мВ, 85 0С).

IV. ЗАКЛЮЧЕНИЕ

Реализация конвейерного процессора RISC-V из примера 7.25 работы [2] в САПР Quartus Prime 17.1.0 в ПЛИС серии Cyclone V показывает потерю его функциональности. Симуляция в Quartus Prime после синтеза проекта отличается от симуляции в ModelSim. Приблизить поведение САПР Quartus к ModelSim возможно отключением оптимизации. Для восстановления функциональности процессора требуется защитить от оптимизации четыре регистра процессора использованием специальной директивы в Verilog-коде: flopr, floprc, flopenr и flopenrc.

Была доработана схема проекта конвейерного процессора, так, чтобы он проходил оптимизацию и при этом сохранял свою работоспособность. Для устранения несоответствия потребовалось внести изменения в схему подключения регистрового файла и добавить дополнительный шинный мультиплексор три в один (“заплатка”), который позволяет обойти конвейерный регистр RegW для операции записи данных в регистровый файл.

ЛИТЕРАТУРА

[1]. Сара Л. Харрис, Дэвид Харрис. Цифровая схемотехника и архитектура компьютера: RISC-V / пер. с англ. В.С. Яценкова, А.Ю. Романова; под ред. А. Ю. Романова. – М.: ДМК Пресс, 2021. – 810 с.

[2]. Sarah L. Harris and David Harris Exercise Solutions – Digital Design and Computer Architecture: RISC-V Edition Elsevier 2021. https://pages.hmc.edu/harris/ddca/ddcarv/DDCArv_solutions_odd.pdf

[3]. Строгонов А.В., Винокуров А., Строгонов А.И. Пример реализации однотактного процессорного ядра RISC-V в САПР Altera Quartus II // Электроника: Наука, Технология, Бизнес. 2024. № 9. С. 1-8.

Literature

[1]. Sarah L. Harris, David Harris. Digital Circuit Design and Computer Architecture: RISC-V / trans. from English by V.S. Yatsenkova, A.Yu. Romanov; edited by A. Yu. Romanov. – M.: DMK Press, 2021. – 810 p.

[2]. Sarah L. Harris and David Harris Exercise Solutions – Digital Design and Computer Architecture: RISC-V Edition Elsevier 2021. https://pages.hmc.edu/harris/ddca/ddcarv/DDCArv_solutions_odd.pdf

[3]. Strogonov A.V., Vinokurov A., Strogonov A.I. An Example of Implementation of a Single-Cycle RISC-V Processor Core in Altera Quartus II CAD // Electronics: Science, Technology, Business. 2024. No. 9. pp. 1-8.