УДК 621.382

А.В. Бунина, С.В. Калиниченко, И.А. Суров

АО «Научно-исследовательский институт электронной техники»

Аннотация: В статье рассматриваются особенности разработки топологии аналоговых сложно-функциональных блоков интегральных схем с целью уменьшения рассогласования параметров элементов. Показана роль топологических методов согласования при проектировании аналоговых схем, чувствительных к систематическим и случайным факторам рассогласования. На примере двухкаскадного операционного усилителя описан процесс компоновки и согласования элементов с использованием инструмента Virtuoso Module Generator, входящего в состав САПР Cadence Virtuoso. Рассмотрены основные возможности инструмента Modgen, включая формирование массивов согласованных транзисторов, использование фиктивных элементов, защитных колец и средств автоматизированной трассировки. Продемонстрирован процесс генерации модулей, их перенос в топологию и окончательная сборка топологии операционного усилителя. Показано, что применение инструмента Module Generator позволяет сократить время разработки топологии и упростить внесение изменений на этапе проектирования.

Ключевые слова: аналоговые СФ-блоки, интегральные схемы, топология, САПР, Cadence Virtuoso, Modgen.

Automation of analog integrated circuit layout design using CAD tools

A. V. Bunina, S. V. Kalinichenko, I. A. Surov

JSC «Research Institute of Electronic Engineering»

Abstract: This paper discusses the features of analog complex functional block layout design aimed at reducing parameter mismatch of circuit elements. The role of layout-based matching techniques in the design of analog circuits sensitive to systematic and random mismatch factors is presented. Using a two-stage operational amplifier as an example, the process of element placement and matching with the Virtuoso Module Generator tool included in the Cadence Virtuoso CAD system is described. The main capabilities of the Modgen tool are considered, including the formation of matched transistor arrays, the use of dummy devices, guard rings, and automated routing features. The process of module generation, its transfer to the layout environment, and the final assembly of the operational amplifier layout is demonstrated. It is shown that the use of the Module Generator tool reduces layout development time and simplifies design modifications during the development process.

Keywords: analog complex functional blocks, integrated circuits, layout, computer-aided design, Cadence Virtuoso, Modgen.

I. ВВЕДЕНИЕ

Разработка топологии является одним из самых трудоемких и длительных этапов проектирования аналоговых интегральных схем (ИС) и сложно-функциональных (СФ) блоков. Аналоговые блоки, такие как усилители, источники опорного напряжения (ИОН), матрицы взвешивающих элементов в составе цифроаналоговых и аналогово-цифровых преобразователей (ЦАП и АЦП), чувствительны к воздействию рассогласующих факторов на компоненты схемы. Рассогласование параметров может иметь случайный и систематический характер [1]. Основными причинами рассогласования являются [2]:

– геометрические погрешности;

– механические напряжения и их градиент;

– изменение геометрии элементов;

– генерация напряжения;

– изменение параметров элементов.

Для минимизации систематического рассогласования параметров применяют специальные методы расположения компонентов при разработке топологии, а для минимизации случайного рассогласования – методы индивидуальной калибровки. Совокупность схемотехнических и топологических методов позволяет достичь необходимых характеристик устройства. Поэтому важную роль играет совместное участие в работе инженеров-схемотехников и топологов.

Современные САПР для проектирования ИС пока не могут предложить универсальный инструмент для полностью автоматической генерации топологии аналоговых СФ-блоков, применимый для любых технологических процессов. Однако ускорить процесс компоновки элементов в аналоговых СФ-блоках позволяет инструмент среды проектирования интегральных схем Cadence Virtuoso – Virtuoso Module Generator (Modgen). Знакомство с этим инструментом проведем на примере ОУ, схема которого рассмотрена в разделе I. В разделе II приведены и описаны основные функции инструмента Modgen, а также показан процесс формирования топологии модулей ОУ. В завершающем III разделе показана окончательная сборка топологии из сгенерированных модулей и трассировка ОУ.

II. СХЕМА ОУ

Перед разработкой топологии ОУ необходимо проанализировать его электрическую схему. Основными функциональными блоками ОУ являются токовые зеркала и дифференциальная пара. Эти блоки требуют высокой степени согласования для уменьшения напряжения смещения [3].

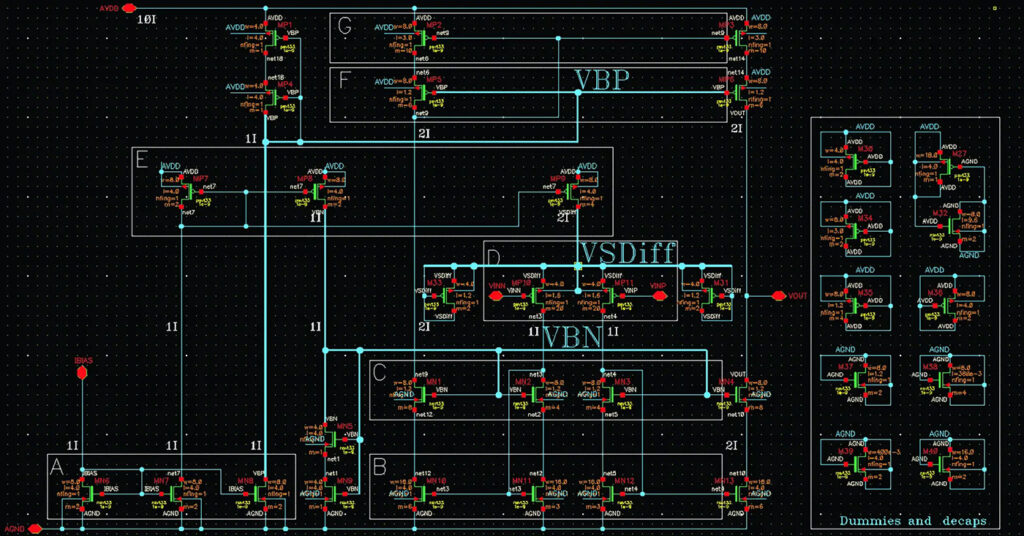

Разработанная в среде Cadence Virtuoso схема двухкаскадного операционного усилителя представлена на рисунке 1.

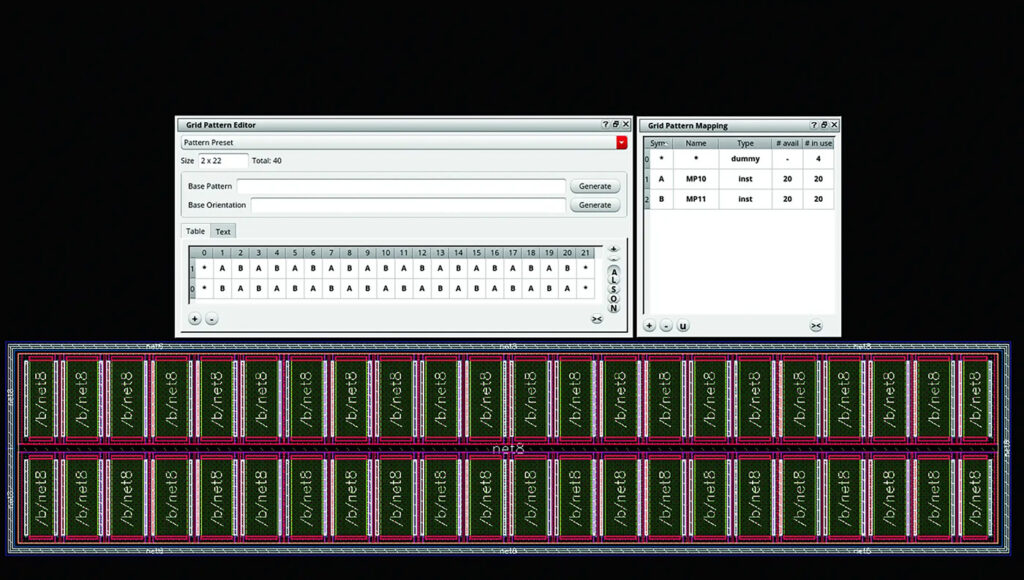

Рассмотрим более подробно схему ОУ. Дифференциальная пара ОУ выполнена на р-канальных транзисторах MP10 и MP11. Истоки транзисторов имеют общее соединение VSDiff и соединены с карманом n-типа. Согласование дифференциальной пары достигается за счёт размещения однотипных элементов в двумерном массиве с перекрестными связями [4].

К стокам транзисторов MP10 и MP11 подключена нагрузка в виде каскодных токовых зеркал на n-канальных транзисторах MN1, MN2, MN10, MN11 и MN3, MN4, MN12, MN13. Эти токовые зеркала имеют коэффициент передачи тока 2:1.

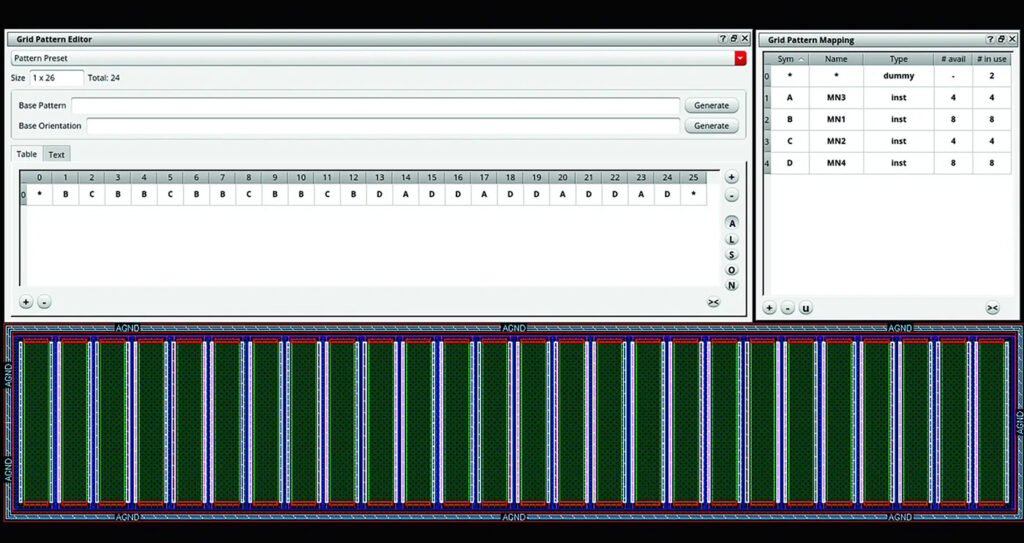

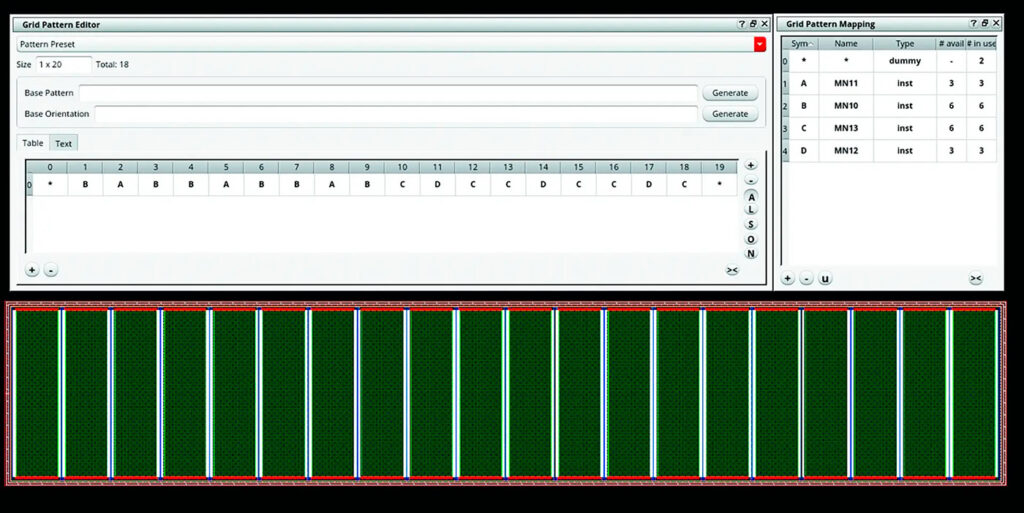

Транзисторы MN1, MN2, MN3, MN4 согласованы путём размещения в одномерном массиве с общей осью симметрии для каждой группы: слева расположены транзисторы MN1, MN2; справа – транзисторы MN3, MN4. Аналогичным образом построен массив транзисторов MN10, MN11, MN12, MN13: слева расположены транзисторы MN10, MN11; справа – транзисторы MN12, MN13.

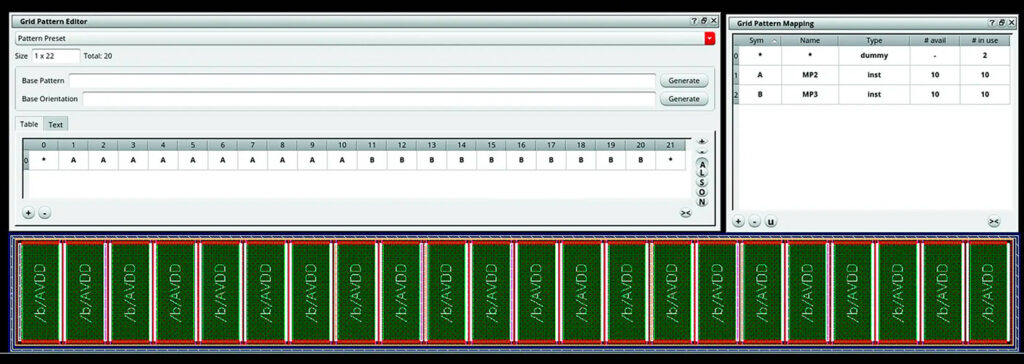

Ток стока транзистора MN1 поступает на сток транзистора MP5, который образует вместе с р-канальными транзисторами MP2, MP3, MP6 каскодное токовое зеркало с коэффициентом передачи тока 1:1. Транзисторы MP2, MP3 собраны в одномерный массив. Набор транзисторов MP5 расположен слева от массива транзисторов MP7, MP8, MP9. Аналогичным образом справа размещен набор транзисторов MP6.

Выходной ток каскодного токового зеркала вытекает из стока транзистора MP6 и распределяется между выходом ОУ и стоком транзистора MN4.

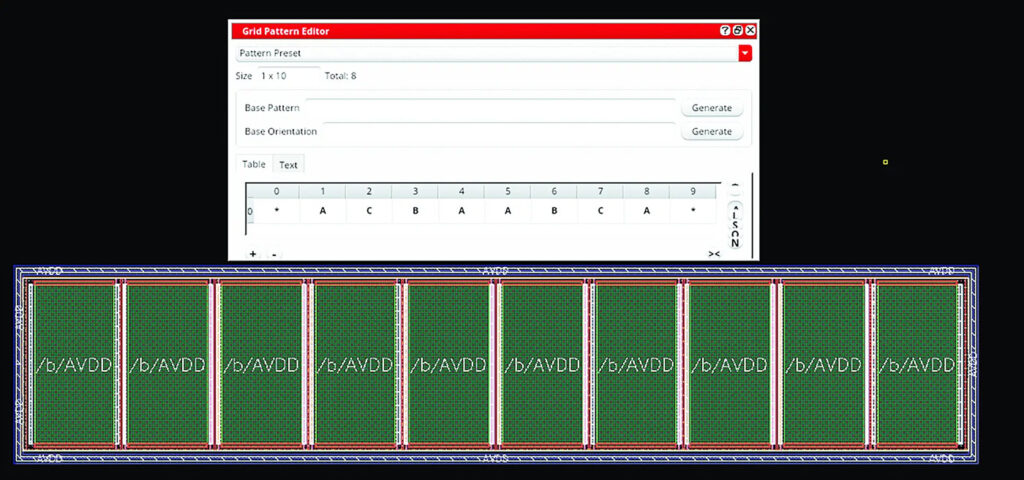

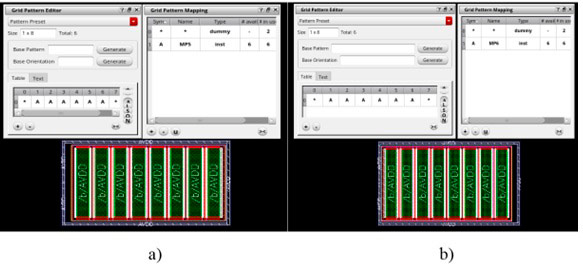

В данном ОУ нет внутреннего источника тока, поэтому опорный ток (I = 5 мкА) требуется подавать извне на вход IBIAS. Полученный опорный ток распределяется с помощью системы токовых зеркал на транзисторах MN6, MN7, MN8 и MP7, MP8, MP9. Ток величиной 2I поступает от стока транзистора MP9 на истоки дифференциальной пары. Транзисторы MN6, MN7, MN8 образуют двумерный массив согласованных идентичных элементов с перекрестными связями и общей осью симметрии. Транзисторы MP7, MP8, MP9 размещены в одномерном массиве с общим центром.

На составной транзистор в диодном включении MP1 – MP4 поступает отраженный опорный ток I, и на его стоке формируется потенциал VBP. Этот потенциал подается на затворы транзисторов MP5, MP6 для обеспечения режима насыщения транзисторов токового зеркала MP2, MP3.

Аналогичным образом работает формирователь напряжения смещения VBN для n-канальных токовых зеркал, основанный на составном транзисторе MN5 – MN9 в диодном включении.

По краям массивов транзисторов расположены фиктивные элементы. Они служат для обеспечения идентичности окружения у транзисторов, находящихся на периферии согласованной группы [5]. Также добавление фиктивных транзисторов p-типа позволяет уменьшить влияние эффекта близости края кармана n-типа (well proximity effect – WPE [6]).

III. ОПИСАНИЕ И ПРИМЕНЕНИЕ ИНСТРУМЕНТА MODGEN

Определившись с функциональным составом ОУ, можно приступать к разработке топологии. Работа с инструментом Modgen может осуществляться как из схемы, так и из топологии. Вначале создадим ограничения (Constraints), используя интерфейс окна редактора схемы Schematic Editor.

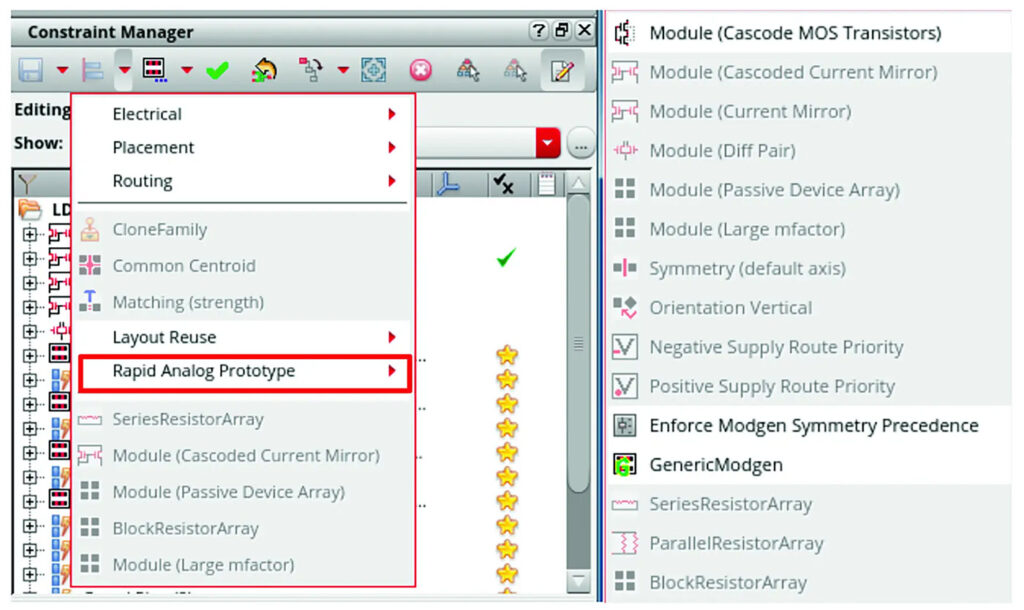

После выбора режима Constraints появляется окно управления ограничениями (Constraint Manager) c панелью инструментов, позволяющей создать массивы согласованных элементов. Меню управления ограничениями имеет в своем функционале уже готовые прототипы для базовых структур схемы (инструмент Rapid Analog Prototype).

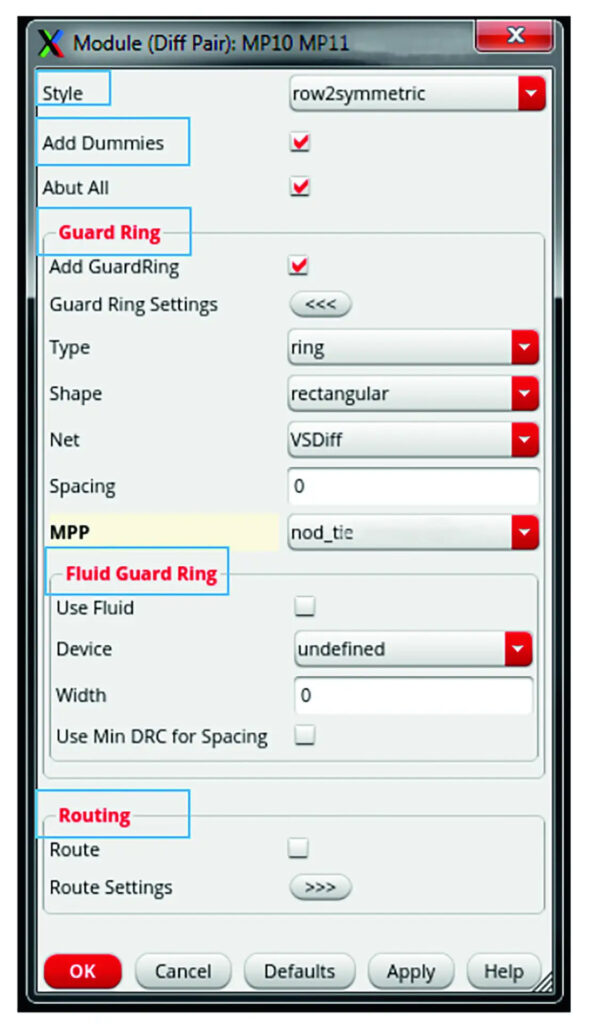

Для объединения согласованных транзисторов дифференциальной пары воспользуемся базовым модулем – Module (Diff Pair). Появляющееся окно позволяет задать настройки будущего массива (рисунок 3):

– выбрать размерность массива (инструмент Style);

– добавить фиктивные элементы (инструмент Add Dummies);

– добавить охранные кольца (инструменты Guard Ring иFluid Guard Ring);

– выполнить соединения выводов сегментов дифференциальной пары (инструмент Routing).

Окно редактирования Modgen Editing позволяет настроить созданный массив элементов в графическом режиме. Рассмотрим подробнее доступные инструменты окна. Инструменты размещения элементов (рисунок 4) позволяют:

– выравнивать объекты в заданном направлении (инструмент Align);

– добавлять фиктивные элементы (инструменты Dummies и Add Dummy Row/Column);

– добавлять пустые строки/столбцы (инструмент Add Empty Row/Column);

– добавлять в схему из редактора топологии все созданные фиктивные элементы (инструмент Backannotate All Active Dummy Instances);

– добавлять контакты между проводящим каналом и подложкой (инструмент Body Contact);

– состыковывать все или только выбранные сегменты с общим подключением (инструменты Abut All либо Abut), либо отрывать их (инструменты Unabut All, Unabut);

– применять один и тот же вариант примыкания к выбранным рядам элементов (инструмент Sync Abut OFF);

– указывать значения выравнивания и интервала по нужному слою для сегментов (инструмент Member Alignmemt/Spacing);

– объединять слои (инструмент Merge Layers);

– добавлять защитные кольца (инструмент Guard Ring);

– создавать шаблоны для согласованных структур (инструмент Pattern);

– менять местами два сегмента, строки или столбцы (инструмент Swap).

2 – Dummies;3 – Add Dummy Row/Column; 4 – Add Empty Row/Column;

5 – Backannotate All Active Dummy Instances; 6 – Body Contact; 7 – Abut All;

8 – Abut; 9 – Unabut All; 10 – Unabut; 11 – Sync Abut OFF; 12 – Member Alignmemt/Spacing;13 – Merge Layers; 14 – Guard Ring; 15 – Pattern; 16 – Swap

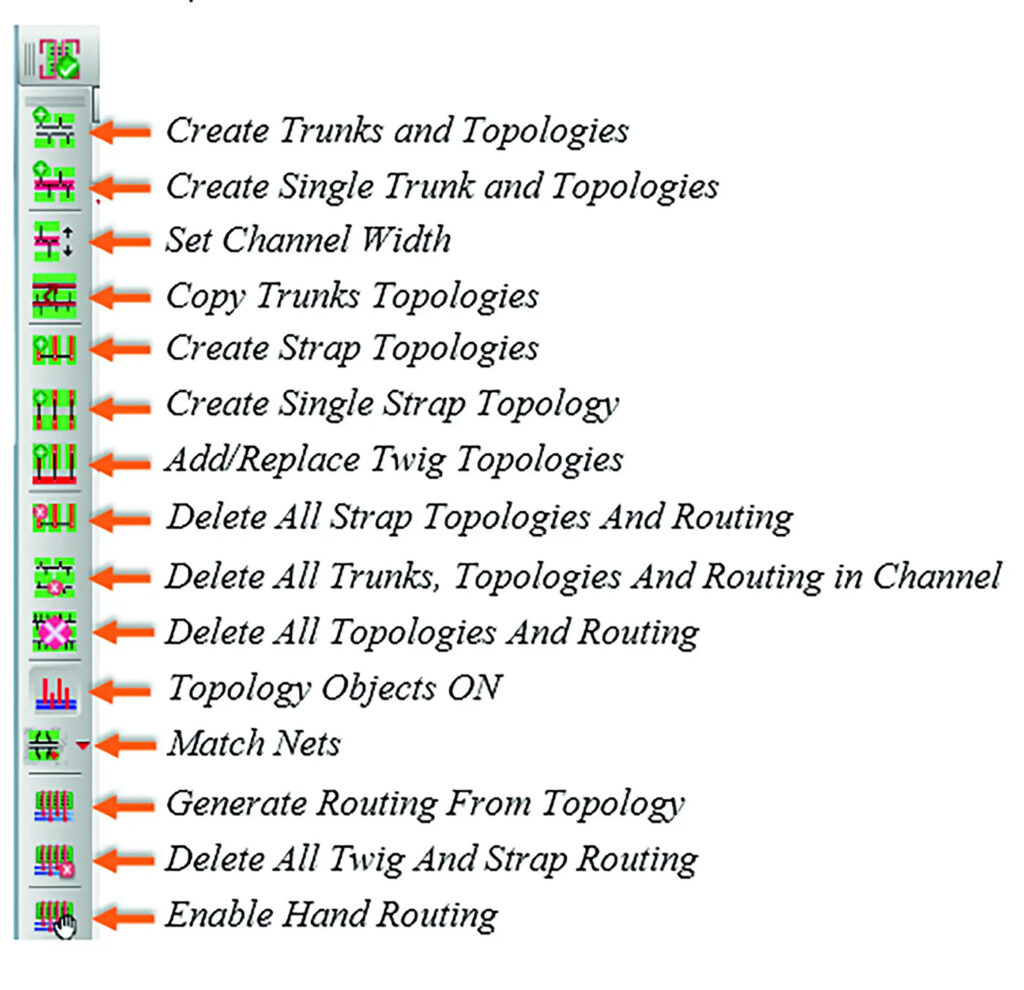

Инструменты трассировки (рисунок 5) позволяют:

– создавать одну или несколько шин и соединения к ним (инструменты Create Trunks and Topologies иCreate Single Trunk and Topologies);

– задавать ширину канала трассировки (инструмент Set Channel Width);

– копировать шины и соединения к ним (инструмент Copy Trunks Topologies);

– создавать все соединения к выводам сегментов (инструмент Create Strap Topologies);

– создавать определённое соединение к выводам сегментов (инструмент Create Single Strap Topologies);

– добавлять/заменять соединения от выводов к шинам (инструмент Add/Replace Twig Topologies);

– удалять всю топологию трассировки соединений к выводам сегментов (инструмент Delete All Strap Topologies And Routing);

– удалять всю топологию трассировки в выбранном канале (инструмент Delete All Trunks, Topologies And Routing in Channel);

– удалять всю топологию трассировки (инструмент Delete All Topologies And Routing);

– убирать отображение созданных соединений (инструмент Topology Objects ON);

– создавать группы соединений с одинаковыми параметрами (инструментMatch Nets);

– создавать соединения от контактов к шине (инструмент Generate Routing From Topology);

– удалять все соединения к шинам (инструмент Delete All Twig And Strap Routing);

– включать ручную трассировку (инструментEnable Hand Routing).

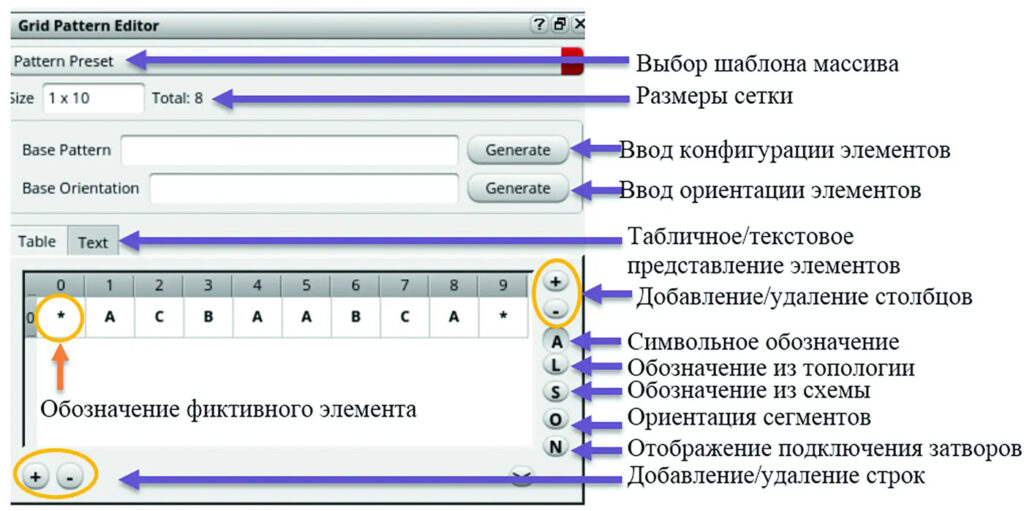

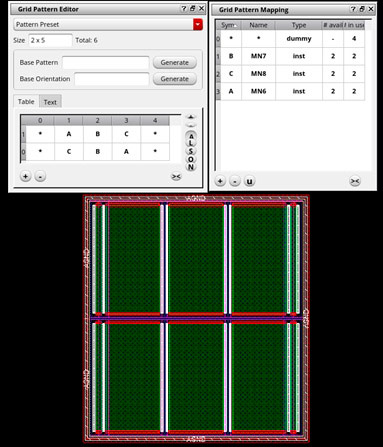

Инструмент Grid Pattern Editor (GPE), предоставляющий возможность просматривать и редактировать шаблон размещения элементов и их ориентацию (рисунок 6).

на транзисторах: MP7 (B), MP8 (C), MP9 (A)

Инструмент Grid Pattern Mapping (GPM), с помощью которого можно сопоставить элементы в схеме и топологии, показан на рисунке 7.

Пользуясь возможностями инструмента Modgen [7], выполним согласование дифференциальной пары путём расположения элементов с перекрестными связями.

Обеспечим компактность структуры, сблизив транзисторы между собой до минимального допустимого расстояния по активному слою (Member Alignmemt/Spacing). Также объединим все транзисторы по подложке

(Merge Layers). Между рядами транзисторов дифференциальной пары будут расположены соединения затворов. С помощью инструмента Set Channel Width устанавливается расстояние между верхним и нижним рядами дифференциальной пары по выбранному слою. Полученный блок представлен на рисунке 8.

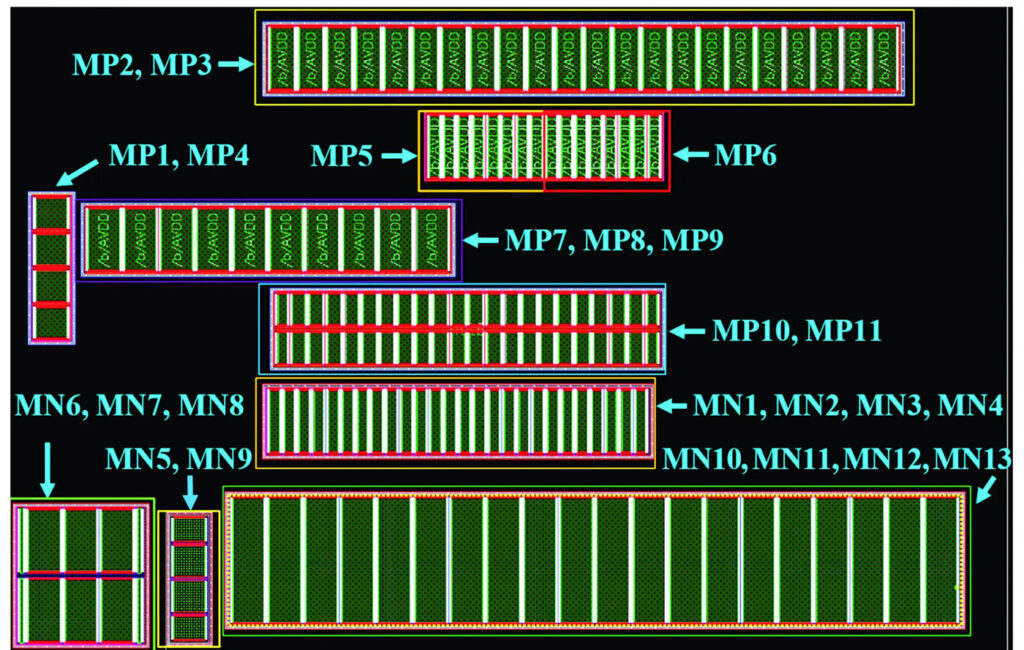

Токовые зеркала разделим на блоки с использованием инструмента ModuleCurrentMirror. Полученные блоки представлены на рисунках 9–14. Блоки составных транзисторов MP1, MP4 и MN5, MN9 созданы с помощью инструмента Modgen (рисунок 15).

На этом этапе завершается формирование согласованных наборов транзисторов. Внести изменения в созданные блоки можно в любой момент в процессе редактирования топологии ОУ.

IV. СБОРКА ТОПОЛОГИИ ОУ

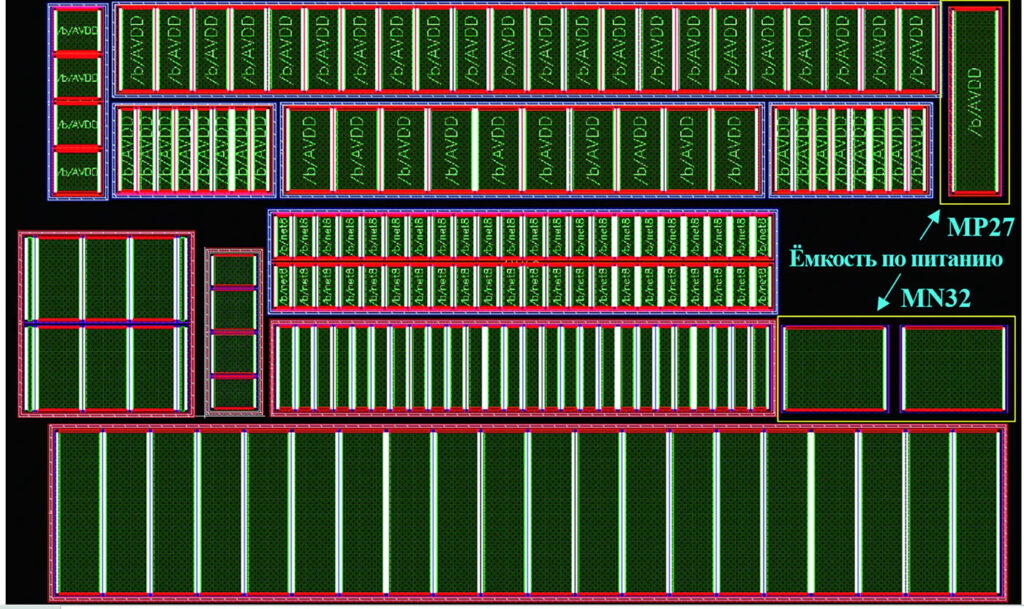

Перенесём созданные блоки из схемы в топологию (Layout) с помощью инструмента в нижней панели окна редактирования топологии – Generate All From Source (рисунок 16).

Основные блоки расположим симметрично относительно вертикальной оси. Результат представлен на рисунке 17. Для симметрии топологии и обеспечения идентичного окружения блоков транзисторов справа была добавлена ёмкость по питанию, выполненная на р-канальном и

n-канальном транзисторах.

Токовые зеркала на р-канальных транзисторах находятся под общим потенциалом напряжения питания (AVDD). Подложка дифференциальной пары подведена к соединению VSDiff, поэтому фиктивные элементы также подключены к этому узлу.

Наличие двух расположенных рядом карманов n-типа под разными потенциалами (VSDiff и AVDD) у наборов p-канальных транзисторов может привести к образованию паразитного канала между карманами. Для предотвращения утечек дифференциальную пару окружим защитным кольцом p-типа [8], подключенным к потенциалу AGND.

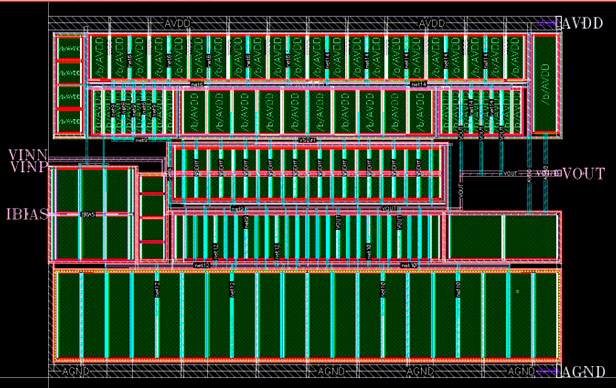

Далее приступим к соединению блоков между собой. Готовая топология представлена на рисунке 18.

VOUT – выходной порт ОУ; AVDD, AGND – шины питания

V. ЗАКЛЮЧЕНИЕ

Инструмент Module Generator, входящий в состав САПР Cadence Virtuoso, является эффективным средством автоматизации проектирования топологии аналоговых сложно-функциональных блоков и интегральных схем. Он позволяет сократить объём рутинных операций при компоновке и согласовании элементов, а также снизить вероятность ошибок, связанных с ручной разработкой.

Использование Module Generator обеспечивает формирование согласованных структур транзисторов с учётом топологических ограничений, включая симметрию, фиктивные элементы и защитные кольца, что особенно важно для аналоговых блоков, чувствительных к рассогласованию параметров. Автоматизация этапов размещения и трассировки ускоряет процесс разработки топологии, предоставляет больше времени для моделирования и оптимизации устройства и упрощает внесение изменений на последующих этапах проектирования.

ЛИТЕРАТУРА

- McCreary, J. L. Matching properties and voltage and temperature dependence of MOS capacitors. IEEE Journal of Solid-State Circuits, 16(6), 1981, pp. 608–616.

- В. И. Эннс. Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика / Под ред. В. И. Эннса. 2-е изд., стереотип. – М.: Горячая линия – Телеком, 2016. – 454 с.

- Gregor, R. W. On the relationship between topography and transistor matching in an analog CMOS technology, IEEE Transactions on Electron Devices, 39(2), 1992, pp. 275–282.

- Razavi Behzad. Design of analog CMOS integrated circuits, University of California, Los Angeles. Second edition, 2001, pp. 684.

- Phillip E. Allen, Douglas R. Holberg “CMOS Analog Circuit Design”, Oxford University Press, 2017, pp. 590.

- Drennan, P. G., Kniffin, M., & Locascio, D. Implications of Proximity Effects for Analog Design. IEEE Custom Integrated Circuits Conference 2006.

- Modgen / Rapid Adoption Kit// 2019, Cadence Design Systems.

- Alan Hastings. The Art of Analog Layout. Pearson Prentice Hall, Second Edition, 2006, pp. 648.

REFERENCE

- McCreary, J. L. Matching properties, and voltage and temperature dependence of MOS capacitors. IEEE Journal of Solid-State Circuits, vol. 16, no. 6, 1981, pp. 608–616.

- Enns, V. I. Design of Analog CMOS Integrated Circuits. A Concise Designer’s Handbook. 2nd ed., stereotype edition. Moscow: Hotline –Telecom, 2016, 454 p.(in Russian)

- Gregor, R. W. On the relationship between topography and transistor matching in an analog CMOS technology. IEEE Transactions on Electron Devices, vol. 39, no. 2, 1992, pp. 275–282.

- Razavi, B. Design of Analog CMOS Integrated Circuits. 2nd ed. Los Angeles: University of California, 2001, 684 p.

- Allen, P. E., Holberg, D. R. CMOS Analog Circuit Design. Oxford: Oxford University Press, 2017, 590 p.

- Drennan, P. G., Kniffin, M., Locascio, D. Implications of proximity effects for analog design. In: Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), 2006.

- Cadence Design Systems. Modgen / Rapid Adoption Kit. 2019.

- Hastings, A. The Art of Analog Layout. 2nd ed. Upper Saddle River, NJ: Pearson Prentice Hall, 2006, 648 p.