Цена по запросу

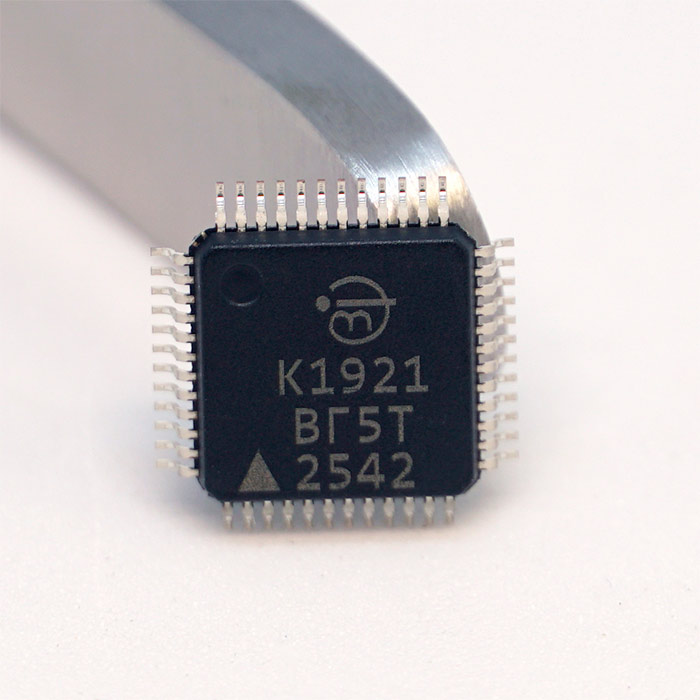

Универсальный 32-разрядный микроконтроллер архитектуры RISC-V, предназначенный для применения в портативных системах с ограничениями по размерам. Содержит энергонезависимую память объемом 512 Кбайт, набор универсальных, специализированных блоков и интерфейсов.

Состав и функциональные особенности:

• Микропроцессорное ядро RISC-V 32-бита, 32 регистра, встроенным модулем обработки команд с плавающей запятой с одинарной точностью (FPU), поддержкой отладочного интерфейса JTAG;

• Кэш команд и кэш данных объемом по 4 Кбайт каждый;

• 16-канальный контроллер прямого доступа к памяти DMA;

• Оперативная память TCM объемом 32 Кбайт;

• Оперативная память SRAM данных объемом 16 Кбайт;

• Flash-память объемом 512 Кбайт;

• Четыре 32-разрядных мультифункциональных таймера с поддержкой PWM и режима захвата;

• Три двухканальных блока ШИМ;

• Импульсный квадратурный декодер QEP;

• Три блока захвата CAP;

• Сторожевой таймер;

• Часы реального времени RTC c батарейным питанием;

• Два контроллера интерфейса SPI;

• Контроллер интерфейса I2C;

• Два контроллера интерфейса UART;

• Контроллер интерфейса CAN на 2 узла;

• Интерфейс ввода-вывода общего назначения GPIO;

• 4-канальный 12-битный АЦП;

• Супервизор питания POR/BOR;

• Максимальная частота работы 100 МГц;

• Корпус: LQFP-48.

• Микропроцессорное ядро RISC-V 32-бита, 32 регистра, встроенным модулем обработки команд с плавающей запятой с одинарной точностью (FPU), поддержкой отладочного интерфейса JTAG;

• Кэш команд и кэш данных объемом по 4 Кбайт каждый;

• 16-канальный контроллер прямого доступа к памяти DMA;

• Оперативная память TCM объемом 32 Кбайт;

• Оперативная память SRAM данных объемом 16 Кбайт;

• Flash-память объемом 512 Кбайт;

• Четыре 32-разрядных мультифункциональных таймера с поддержкой PWM и режима захвата;

• Три двухканальных блока ШИМ;

• Импульсный квадратурный декодер QEP;

• Три блока захвата CAP;

• Сторожевой таймер;

• Часы реального времени RTC c батарейным питанием;

• Два контроллера интерфейса SPI;

• Контроллер интерфейса I2C;

• Два контроллера интерфейса UART;

• Контроллер интерфейса CAN на 2 узла;

• Интерфейс ввода-вывода общего назначения GPIO;

• 4-канальный 12-битный АЦП;

• Супервизор питания POR/BOR;

• Максимальная частота работы 100 МГц;

• Корпус: LQFP-48.

Чертеж корпуса

3D-модель (находится в разработке)

3D-модель (находится в разработке)